Vol. 44 No. 2 Feb. 2023

DOI: 10. 19650/j. cnki. cjsi. J2210140

# 高速并行数字调制信号的产生与实现\*

李 浩1,王厚军1,肖 磊2,王志刚1,李 涛3

(1. 电子科技大学自动化工程学院 成都 611731; 2. 中国电子科技集团公司航空电子信息系统技术重点实验室 成都 610036; 3. 山西省检验检测中心(山西省标准计量技术研究院) 太原 030000)

摘 要:数字调制技术是高速通信传输系统的关键技术之一。本文提出了一种全并行的高速数字调制信号产生架构,该架构可以在现场可编程门阵列(FPGA)硬件平台中通过算法级的流水线实现。通过理论分析与推导,并行频域成型滤波器中的 DFT/IDFT 可以由低复杂度的两个基-8 FFT 算法级联构成,进一步给出了具体的 FPGA 架构和实现方法。另外,为了进一步降低硬件资源,本文分析并设计了一种适用于并行实现的免混频数字正交上变频架构。仿真实验对高速并行数字调制架构中的并行频域成型滤波器在时域和频域分别进行了算法验证,FPGA 硬件实现结果验证了高速并行数字调制信号产生的频谱性能。

关键词: 数字调制:成型滤波;基-8 FFT;FPGA 实现;数字正交上变频

中图分类号: TH85 文献标识码: A 国家标准学科分类代码: 510.50

## Generation and implementation of high-speed parallel digital modulation signals

Li Hao<sup>1</sup>, Wang Houjun<sup>1</sup>, Xiao Lei<sup>2</sup>, Wang Zhigang<sup>1</sup>, Li Tao<sup>3</sup>

(1. School of Automation Engineering, University of Electronic Science and Technology of China, Chengdu 611731, China;

2. CETC Key Laboratory of Avionic Information System Technology, Chengdu 610036, China;

3. Inspection and Testing Center of Shanxi Province (Institute of Standard Metrology of Shanxi Province), Taiyuan 030000, China)

Abstract: Digital modulation technology is one of the key technologies of the high-speed communication transmission system. In this article, an architecture of high-speed digital modulation signal generation in parallel is proposed, which can be implemented by algorithm-level pipeline in field programmable gate array (FPGA) hardware platform. With theoretical analysis and derivation, DFT/IDFT in parallel frequency domain forming filter can be cascaded by two levels of the low-complexity based-8 FFT algorithm, and the specific FPGA architecture and implementation method are given. In addition, a mixing-free digital orthogonal up-conversion architecture suitable for parallel implementation is analyzed and designed to further reduce hardware resource. The simulation experiments evaluate the algorithm of the high-speed parallel digital modulation architecture, and the FPGA hardware implementation results test the spectrum performance of the high-speed parallel digital modulation signal.

Keywords: digital modulation; forming filter; based-8 FFT; FPGA implementation; digital orthogonal up-conversion

# 0 引 言

随着无线通信技术的跨越式发展,个人应用领域(如高清电视、视频通话、实景娱乐等)、云服务、物联网、无人机等不同领域对高速传输速率提出了更高的需求[14]。 另外,军事领域也依赖于高速实时传输的情报命令等进 行信息化的指挥。而这些需求对移动通信卫星、广播电 视卫星等都提出了更高通信传输速率的要求。

调制技术是高速通信传输系统的核心环节<sup>[5]</sup>,调制的目的是将用户信息转变为在信道中传输的模拟波形。调制分为模拟调制和数字调制。但是模拟调制电路存在不稳定、可靠性差、元器件之间的幅相特性差、体积大等一些无法克服的弊端。而随着集成电路及国产数字芯片的发

收稿日期:2022-07-15 Received Date: 2022-07-15

展<sup>[6]</sup>,如:数模转换器(digital-analog converter, DAC)和现场可编程门阵列(field programmable gate array, FPGA)等,全数字的高速调制技术成为了研究热点,这是因为数字调制宽带信号具有抗干扰强、稳定性好、可靠性高、体积小等优势<sup>[7]</sup>。为了保障高速数传系统以及卫星通信系统的传输性能,数字调制成为了发射系统的关键技术<sup>[8]</sup>。因此,本文主要研究数字调制技术的设计与实现。

传统的数字调制技术采用串行架构,这只适用于低速率传输系统。由于 FPGA 数字芯片的工作时钟频率存在瓶颈(低于 300 MHz),所以通过串行架构来提高数据的传输速率是不可实现的。根据面积换取速率的并行化思想,采用并行处理架构可以将高速数据流分解到各个并行之路以降低速率<sup>[9]</sup>,进而 FPGA 在较低工作频率下完成高码率的调制。

国外对于高速并行数字调制解调技术的研究已进入军事化和产业化阶段,美国研制的宽带全球卫星通信系统容量最大达到了 3.6 Gbps<sup>[10]</sup>,实现了宽带通讯的全球覆盖;欧洲航空局研制的宽带卫星调制解调器<sup>[11]</sup>,最大目标信息速率达 1 Gbps;法国 DODIAC 公司研发的 Cortex HDL XXL 高速调制解调器,其最大传输速率可达 2 Gbps<sup>[12]</sup>;日本采用 QPSK 调制方案研制了数据速率高达 1.2 Gbps 的双通道通信卫星系统<sup>[13]</sup>。

国内对高速调制解调原理样机的研究也取得了不少成果。电子科技大学针对 QPSK 和 8PSK 采用并行架构研制了高速解调系统<sup>[12,14]</sup>,最大符号率为 360 MHz。中国电子科技集团公司第 54 研究所设计了支持 BPSK 和 QPSK 的调制解调器<sup>[15-16]</sup>,信息速率在 30~600 Mbps 范围内可变。

以 QPSK 调制信号为例,本文提出了一种高效、高码率的全并行调制架构。本文对高速并行数字调制架构的设计思路进行了详细论述,重点分析了调制技术中的成型滤波和数字正交上变频 2 个模块,并给出了 FPGA 实现框图。相比已有技术,本文设计的载波频率和符号率更高,而且降低了并行成型滤波器和数字正交上变频的乘法器资源。

### 1 数字调制技术基本原理

### 1.1 数字调制数学模型

数字调制技术的基本原理是通过正交调制法完成模 拟信号的发射。调制信号的数学表达式为:

$$s(t) = A(t)\cos\left[2\pi f_c t + \theta(t)\right] \tag{1}$$

其中, A(t) 为信号幅度;  $f_c$  为载波信号的频率;  $\theta(t)$

为载波信号的相位。将式(1)分解,可得:

$$s(t) = \underbrace{A(t)\cos[\theta(t)]}_{I(t)}\cos[2\pi f_c t] - \underbrace{A(t)\sin[\theta(t)]}_{\theta(t)}\sin[2\pi f_c t] =$$

(2)

$I(t)\cos[2\pi f_c t] - Q(t)\sin[2\pi f_c t]$

其中, I(t) 和 Q(t) 分别为调制信号 s(t) 的同相分量和正交分量。

由式(2)可知,正交调制的基本方法为:首先根据星座图映射出两路独立的 IQ 分量;然后用 IQ 分量分别对两个正交载波信号进行相乘;最后将调制后的两路信号进行相减,即可得到数字调制信号。对于 MPSK、MQAM等数字调制信号,由于其调制信息都可以分解为复基带信号,因此上述信号都可以通过正交调制方法加以实现。

#### 1.2 最佳接收的成型滤波理论

影响数字通信传输性能的主要因素是信道的传输特性、随机噪声和码间串扰。如何从信道干扰中提取出信噪比最大的有用信号是最佳接收理论的目标,从而实现最佳的传输性能。

在实际传输系统中,基带信息是矩形脉冲,其频谱是 无限的。然而系统的信道往往是有限的,这会导致码间 串扰的产生。因此,发射端的基带信号需要添加成型滤 波器将信号的频谱限定在一定带宽。当基带信号使用升 余弦滚降滤波器时,信道的传输特性满足奈奎斯特第一 准则,即可以实现基带信号无码间串扰的带限传输。升 余弦滚降滤波器的频谱为:

$$H(w) = \begin{cases} T, & 0 \leq |w| \leq \frac{(1-\alpha)\pi}{T} \\ \frac{T}{2} \left\{ 1 - \sin \left[ \frac{T}{2\alpha} \left( w - \frac{\pi}{T} \right) \right] \right\}, & \frac{(1-\alpha)\pi}{T} \leq |w| \leq \frac{(1+\alpha)\pi}{T} \\ 0, & |w| \geqslant \frac{(1+\alpha)\pi}{T} \end{cases}$$

$$(3)$$

其中, $\alpha$ 为滚降系数,且 $0<\alpha\leq 1$ ;T为符号周期。

为了实现无码间串扰的最佳接收,传输系统的成型 滤波器和匹配滤波都需满足以下升余弦滚降特性:

$$H(w) = H_T(w)H_R(w) = |H_T(w)|^2$$

(4)

因此,当成型滤波  $H_r(w)$  与匹配滤波  $H_R(w)$  相等且为根升余弦滚降滤波器时,接收端信号的信噪比最大。由此可得:

$$H_T(w) = H_R(w) = \sqrt{H(w)}$$

(5)

# 2 高速并行数字调制架构

为了实现高符号率的数字调制,如表 1 所示,必须采用并行的调制架构。基于传统的数字中频调制器,本文

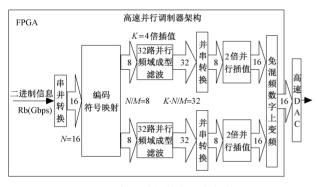

针对设计了适用于高速率传输的全并行数字调制架构,如图 1 所示。图 1 中的高速并行调制架构不受限于表 1 中的参数设置,通过设置调制格式、并行路数完成更高码率的信号调制,也可以通过配置 DAC 采样率完成更高载波频率的调制。

表1 调制参数

Table 1 Modulation parameters

| 参数           | 数值   |

|--------------|------|

| 调制格式         | QPSK |

| 载波频率/MHz     | 800  |

| 符号率/MHz      | 400  |

| 滚降因子         | 0. 4 |

| DAC 采样率/GSPS | 3. 2 |

| 信号动态范围/dBm   | >50  |

图 1 高速并行数字调制架构

Fig. 1 High speed parallel digital modulation architecture

图 1 中,编码和符号映射可以通过软件设计完成,这样降低了硬件实现的复杂度; 2 倍并行插值可以通过时域的多相滤波器快速实现。因此,本文主要关注并行成型滤波和免混频数字上变频的硬件实现方法。

#### 2.1 并行频域成型滤波方案选择

成型滤波器的原理是把输入信号与滤波器系数进行卷积运算,而由卷积定理及性子,卷积运算可以变换到频域运算。假设输入信号为x(n),则将其离散傅里叶变换(discrete Fourier transformation,DFT)运算结果 X(k) 与成型滤波器的频率响应 H(k) 相乘,得到 Y(k)=X(k)H(k),对 Y(k) 做离散傅里叶逆变换(inverse discrete Fourier transform,IDFT)运算即可得到时域的成型滤波结果。然而,2 个离散序列频域相乘结果对应的是 2 个序列的循环卷积,若要采用循环卷积的方法来实现两个序列的线性卷积,就必须对序列作抗混叠处理,即通过重叠保留法分段处理。具体做法为:假设输入的无限长序列 x(n) 分为 Q(Q < P) 段,与长度为 P 的成型滤波响应 h(n) 做循环卷积,则 Q 点循环结果中前 P-1 点

是错误数值,剩余点为线性卷积结果。为此,本文利用重叠保留法将每个输入段与先前的序列重叠P-1点,这样每段有Q-P+1个序列,再将该序列与长度为P的滤波器序列做循环卷积,将得到的结果的前P-1点的混叠数据删除,得到的后Q点数据就是线性卷积结果。

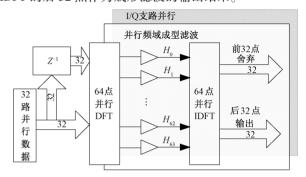

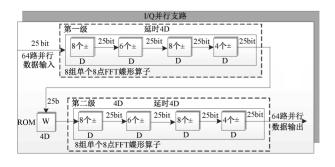

本文设计的成型滤波器阶数为 32,这决定了频域成型滤波采用 32 路并行架构,当频域匹配滤波每次重叠 50%的长度时,运算效率最大化,即每次重叠 32 路进行 64点 DFT 的频域成型滤波,如图 2 所示,每次取 64点 IDFT 的后 32 点作为成形滤波的输出结果。

图 2 并行频域成型滤波架构

Fig. 2 Parallel frequency domain forming filter architecture

#### 2.2 并行频域成型滤波的 FPGA 实现

完成并行频域成型滤波的关键是 N 点 DFT 和 IDFT 的并行实现。对于 N 点的 DFT 和 IDFT,使用快速傅里叶变换(fast Fourier transform,FFT)算法可以使计算复杂度由  $O(N^2)$  降低为  $O(N\ln_2N/2)$ 。 FFT 的可以分为基-2、基-4 和基-8 等不同基数的实现方式。基数越高,其计算复杂度越小,资源消耗量也越小,如表 2 所示。

表 2 FFT 算法的复杂度比较 Table 2 Complex comparison of FFT algorithms

| FFT 算法 | 乘法器                        | 加法器                        |

|--------|----------------------------|----------------------------|

| 基-2    | $(2\ln_2 N - 4)N + 4$      | $(3\ln_2 N - 2)N + 2$      |

| 基-4    | $(1.5 \ln_2 N - 4) N + 4$  | $(2.75 \ln_2 N - 2) N + 2$ |

| 基-8    | $(1.33 \ln_2 N - 4) N + 4$ | $(2.75 \ln_2 N - 4) N + 2$ |

根据表 2,本文选择基-8 FFT 算法来快速实现 64 点 DFT,完成并行频域匹配滤波器的设计。下面给出了基-8 FFT 算法实现 N 点 DFT 的具体过程。

#### 1)基-8 FFT 算法

假设输入序列 x(n) 的点数满足  $N = 8^L$ ,则输入时间变量 n 和输出频率变量 k 可以表示为:

$$\begin{cases} n = \sum_{i=0}^{L-1} n_i 8^i, & n_i = 0, 1, \dots, 7 \\ k = \sum_{i=0}^{L-1} k_i 8^i, & k_i = 0, 1, \dots, 7 \end{cases}$$

(6)

进而, N 点 DFT 的结果 X(k) 可以表示为:

$$X(k) = \sum_{n=0}^{N-1} x(n) W_N^{nk}, \quad 0 \le k \le N-1$$

(7)

其中,

$$W_N^{nk} = e^{-j2\pi/N \cdot nk}$$

,由于 $nk = \left(\sum_{i=0}^{L-1} n_i 8^i\right) \left(\sum_{i=0}^{L-1} k_i 8^i\right)$ ,

则上式可进一步转换为:

将  $N = 8^L$  代入式(8),可得:

$$W_{N}^{nk} = W_{N}^{8^{L-1}k_{0}n_{L-1}} W_{N}^{(8k_{1}+k_{0})8^{L-2}n_{L-2}} \cdots W_{N}^{(\sum\limits_{i=0}^{L-2}k_{i}S^{i})8n_{1}} W_{N}^{(\sum\limits_{i=0}^{L-1}k_{i}S^{i})n_{0}}$$

(9)

将式(9)代入式(7)可得:

$$X(k) = \sum_{n_0=0}^{7} \sum_{n_1=0}^{7} \cdots \sum_{n_{L-1}=0}^{7} x(n_{L-1}, n_{L-2}, \cdots, n_1, n_0) \times$$

$$W_{N}^{8^{L-1}k_{0}n_{L-1}} \times W_{N}^{(8k_{1}+k_{0})8^{L-2}n_{L-2}} \cdots W_{N}^{(\sum_{i=0}^{L-2}k_{i}8^{i})8n_{1}} W_{N}^{(\sum_{i=0}^{L-1}k_{i}8^{i})n_{0}},$$

$$0 \leq k \leq N-1$$

(10)

式(10)可以分解为:

$$X_1(k_0, n_{L-2}, \cdots, n_1, n_0) =$$

$$\sum_{n_{L-1}=0}^{7} x(n_{L-1}, n_{L-2}, \dots, n_{1}, n_{0}) W_{N}^{8^{L-1}k_{0}n_{L-1}} = \sum_{n_{L-1}=0}^{7} x(n_{L-1}, n_{L-2}, \dots, n_{1}, n_{0}) W_{8}^{k_{0}n_{L-1}}$$

(11)

式(11)表示输入变量为  $n_{L-1}$  的一个 8 点 DFT 结果,输出变量为  $k_0$ 。

$$X_{2}(k_{0}, k_{1}, n_{L-3}, \cdots, n_{1}, n_{0}) = \sum_{n_{L-2}=0}^{7} X_{1}(k_{0}, n_{L-2}, \cdots, n_{1}, n_{0}) W_{N}^{8^{L-1}k_{1}n_{L-2}} W_{N}^{8^{L-2}k_{0}n_{L-2}} = \sum_{n_{L-2}=0}^{7} \left[ X_{1}(k_{0}, n_{L-2}, \cdots, n_{1}, n_{0}) W_{N}^{8^{L-2}k_{0}n_{L-2}} \right] W_{8}^{k_{1}n_{L-2}}$$

(12)

式(12)表示将  $X_1(k_0,n_{L-2},\cdots,n_1,n_0)$  乘以  $W_N^{8^{-2}k_0n_{L-2}}$  后,以输入变量为  $n_{L-2}$  的一个 8 点 DFT 结果,输出变量为  $k_1$ 。 因此,可以获得:

$$X_{L}(k_{0}, k_{1}, \cdots, k_{L-2}, k_{L-1}) = \sum_{k_{L-2}=0}^{7} \left[ X_{L-1}(k_{0}, k_{1}, \cdots, k_{L-2}, n_{0}) W_{N}^{(\sum_{i=0}^{L-2} k_{i} 8^{i}) n_{0}} \right] W_{8}^{k_{L-1} n_{0}}$$

(13)

可以发现,序列  $X_L(k_0,k_1,\cdots,k_{L-2},k_{L-1})$  的频率变量相对于输入序列  $x(n_{L-1},n_{L-2},\cdots,n_1,n_0)$  的时间变量是相反的。通过重新排列得到如下正常序列的输出,

$$X(k) = X(k_{L-1}, k_{L-2}, \dots, k_1, k_0) = X_L(k_0, k_1, \dots, k_{L-2}, k_{L-1})$$

(14)

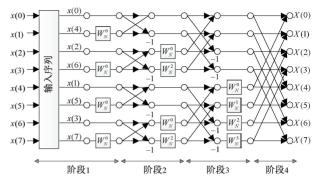

至此,利用基-8 FFT 算法完成了 N 点 DFT 的计算。 由此可知, N 点 DFT 可以利用 L 级 FFT 实现。每一级由 一个基-8 的蝶形算子组成,如图 3 所示,而且每一级之间 需要乘以相应的旋转因子。

图 3 基-8 FFT 算法架构

Fig. 3 Based-8 FFT algorithm architecture

2)64 点并行 DFT 和 IDFT 的 FPGA 实现 对于 64 点 DFT,由式(7)可得:

$$X(k) = \sum_{n=0}^{63} x(n) W_{64}^{nk}, \quad 0 \le k \le 63$$

(15)

分别用八进制来表示输入的时间变量 n、倒序的时间变量  $\overline{n}$  和输出的频率变量 k,则:

$$\begin{cases} n = 8n_1 + n_0, & 0 \le n_i \le 7, i = 0, 1 \\ n = 8n_0 + n_1, & 0 \le n_i \le 7, i = 0, 1 \\ k = 8k_1 + k_0, & 0 \le k_i \le 7, i = 0, 1 \end{cases}$$

(16)

假设  $X(k) = X(k_1, k_0), x(n) = x(n_1, n_0), x(n) = x(n_0, n_1), 式(7)$ 可以变为:

$$X(k) = X(k_1, k_0) = \sum_{n=0}^{63} x(\bar{n}) W_{64}^{\bar{n}k} =$$

$$\begin{split} &\sum_{n_{1}=0}^{7}\sum_{n_{0}=0}^{7}x(n_{0},n_{1})W_{64}^{(8n_{0}+n_{1})(8k_{1}+k_{0})} = \\ &\sum_{n_{1}=0}^{7}\sum_{n_{0}=0}^{7}x(n_{0},n_{1})W_{64}^{(64n_{0}k_{1}+8n_{1}k_{1}+8n_{0}k_{0}+n_{1}k_{0})} = \end{split} \tag{17}$$

$$\sum_{n_1=0}^{7} \sum_{n_0=0}^{7} x(n_0, n_1) W_8^{n_0 k_0} W_{64}^{n_1 k_0} W_8^{n_1 k_1}$$

由式(17)可知,64点 DFT 分解为了两级基-8的 FFT 运算,因此,可以获得:

$$\begin{cases} X_{1}(n_{1},k_{0}) = \sum_{n_{0}=0}^{7} x(n_{0},n_{1}) W_{8}^{n_{0}k_{0}}, \\ 0 \leq k_{0} \leq 7 \\ X_{2}(k_{1},k_{0}) = \sum_{n_{1}=0}^{7} \left[ X_{1}(n_{1},k_{0}) W_{64}^{n_{1}k_{0}} \right] W_{8}^{n_{1}k_{1}}, \\ 0 \leq k_{1} \leq 7 \end{cases}$$

$$(18)$$

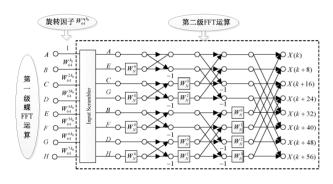

第一级  $X_1(n_1,k_0)$  可以由图 4 的基-8 的 FFT 架构实现;第二级  $X_2(k_1,k_0)$  为 $X_1(n_1,k_0)$  乘以旋转因子  $W_{64}^{n_1k_0}$  结果的 8 点 FFT。综上,64 点 DFT 需要实现两级基-8 的 FFT 运算,以及两极之间乘以旋转因子。下面将讨论 64 点 DFT 的并行实现方法。

本文假设输入的 64 路并行数据 x(n),按照时间变量可以分为 8 个数据组:x(8m),x(8m + 1),…,x(8m + 7),则式(15)可以写为:

$$X(k) = \sum_{m=0}^{7} x(8m) W_{64}^{8mk} + \sum_{m=0}^{7} x(8m+1) W_{64}^{(8m+1)k} + \dots + \sum_{m=0}^{7} x(8m+6) W_{64}^{(8m+6)k} + \sum_{m=0}^{7} x(8m+7) W_{64}^{(8m+7)k} = \sum_{m=0}^{7} x(8m) W_{8}^{mk} + W_{64}^{k} \underbrace{\sum_{m=0}^{7} x(8m+1) W_{8}^{mk}}_{64} + \dots + W_{64}^{6k} \underbrace{\sum_{m=0}^{7} x(8m+6) W_{8}^{mk}}_{64} + W_{64}^{7k} \underbrace{\sum_{m=0}^{7} x(8m+7) W_{8}^{mk}}_{64} + \dots + W_{64}^{mk} \underbrace{\sum_{m=0}^{7} x(8m+7)$$

其中,  $0 \le k \le 7$ ; A, B,  $\cdots$ , G, H 分别表示每 8 个数据的基-8 FFT 计算结果, 这是第一级基-8 FFT 运算的输出。利用基-8 FFT 算法实现的 64 点 DFT 架构如图 4 所示, 其中第一级基-8 FFT 的结果乘以旋转因子后需要重新排列, 才能获得正确的输出序列。

图 4 基-8 FFT 算法的 64 点 DFT 架构

Fig. 4 64 points DFT architecture based-8 FFT algorithm

在 FPGA 实现时,需要对旋转因子进行定点量化,本 文将输入数据量化为 25 bit,将旋转因子量化成 18 bit,这 样便于充分利用 FPGA 的硬件逻辑资源。利用基-8 FFT 算法的 64 点 DFT 流水线实现架构如图 5 所示。

图 5 基-8 FFT 算法的 64 点 DFT 流水线实现架构 Fig. 5 64 points DFT pipeline architecture based-8 FFT algorithm

图 5 中,将旋转因子  $|W_{64}^{n_1k_0}| \le 1$ ,  $(0 \le k_0, n_1 \le 7)$  放大了  $2^{17}$  倍,进而量化为 18 bit 的二进制定点数,其中第一位表示符号位,其他位表示小数位。由于旋转因子是固定的系数,因此在 FPGA 的实现中,可以将其做成ROM 查找表。FFT 计算时只需要查找 ROM 的地址即可获取相应的旋转因子,同时截取乘法器输出结果的低17 位,这样便完成了小数乘法的高效高速高精度计算。在频域成型滤波算法的逻辑实现中,滤波器系数对应的频域数据也需要进行定点量化至 18 bit。成型滤波器的系数可以由 MATLAB 中的根升余弦函数产生,h = rcosine(fs,4\*fs,'sqrt',0.4,4),该系数的整数部分只需要 2 bit 即可表示,依据 XQN 量化原理,此处系数应量化为 2Q15,即将图 2 中的 H(k),0  $\le k \le 63$  放大  $2^{15}$  倍,同时截取乘法器输出结果的低 15 位。

在图 2 中,64 点 DFT 与 64 点成型滤波系数相乘之后,需要对输出结果的 64 路并行数据进行 IDFT 处理。 DFT 和 IDFT 相互转换如下:

$$x(n) = IDFT(X(k)) = \frac{1}{N} \sum_{k=0}^{N-1} X(k) W_N^{-nk} = \frac{1}{N} \left[ \sum_{k=0}^{N-1} X^*(k) W_N^{nk} \right]^* = \frac{1}{N} \left\{ DFT[X^*(k)] \right\}^*$$

(20)

式(20)表明在进行 IDFT 计算时,首先将输入信号取共轭再进行 DFT 计算,然后将得到的 DFT 数据再取共轭,乘以相应的系数,即可完成 IDFT 计算。

#### 2.3 免混频数字上变频的 FPGA 实现

在图 2 中,经过成型滤波及并行插值的信号为基带信号。为了实现带通传输,需要数字上变频将基带信号的频谱搬移到信道的通带。串行的数字正交上变频公式为:

$$s(n) = I(n)\cos[w_0n] - Q(n)\sin[w_0n]$$

(21)

其中,  $w_0 = 2\pi f_c/f_s$ ;  $f_c$  为载波信号的频率;  $f_s$  为 DAC

的采样频率。

传统的高速并行数字正交上变频是将式(21)进行分解,将各个支路的基带信号分别与对应的载波信号相乘。但是该方法消耗大量的乘法器资源,而且对每个支路的同步要求较高。本文设计的 DAC 采样频率为载波频率的 4 倍,则式(21)可以转换为:

$$s(n) = I(n)\cos\left[\frac{\pi n}{2}\right] - Q(n)\sin\left[\frac{\pi n}{2}\right] =$$

$$[I(0), -Q(1), -I(2), Q(3), I(4), -Q(5), -I(6), Q(7), \cdots]$$

(22)

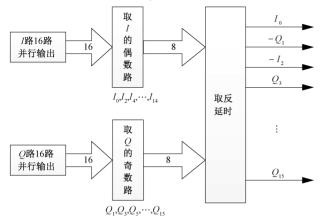

由式(22)可以看出,将插值后的 *IQ* 基带信号与载波信号对应相乘即可完成正交上变频。可以发现,载波的 *I* 路为 ±1 时,*Q* 路为 0;反之载波的 *Q* 路为 ±1 时,*I* 路为 0。这样,只需要将各个支路的输入数据进行取反延时操作即可实现免混频数字正交上变频。

免混频数字正交上变频的并行实现架构如图 6 所示,该结构只需要分别取 *IQ* 的偶数路和奇数路,再进行取反、延时、交织 3 个步骤,即可实现上变频。

图 6 免混频数字正交上变频并行实现架构

Fig. 6 Parallel implementation architecture of digital orthogonal up-conversion without mixing

### 3 仿真与实现

本节将对设计的高速并行数字调制架构进行 MATLAB 仿真验证及 FPGA 实现结果讨论。

#### 3.1 MATLAB 仿真验证

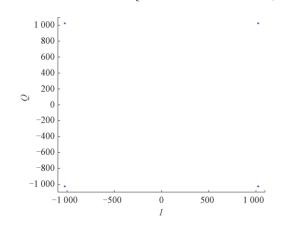

根据表 1 中的参数设置,本文在 MATLAB 中产生一段随机序列,经过差错编码及 QPSK 映射之后输出 *IQ* 各8 路信号,分别作为并行频域成型滤波的输入信号。MATLAB 生成的一个标准 OPSK 星座图如图 7 所示。

图 7 QPSK 标准星座图 Fig. 7 QPSK standard constellation

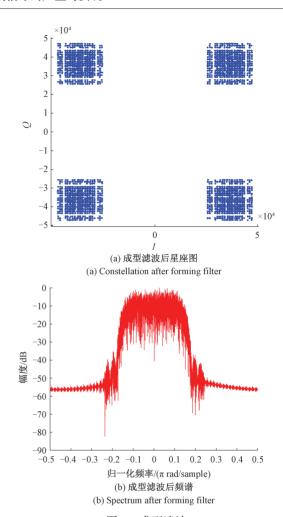

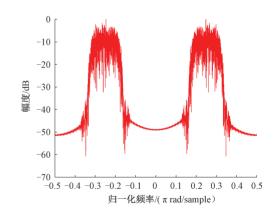

图 8 是成型滤波后的基带信号星座图和频谱图,可以看出,频谱在零中频,中频分析带宽为 0.175×3 200 = 560 MHz,符合表 1 中符号率和滚降因子的要求。

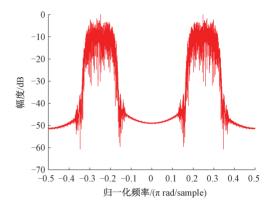

图 9 给出了免混频数字正交上变频后的 QPSK 频谱图,可以看出,载波频率为 0. 25×3 200=800 MHz,中频分析带宽为 560 MHz。

图 8 成型滤波 Fig. 8 Forming filter

图 9 数字正交上变频后频谱

Fig. 9 Spectrum after digital orthogonal up-conversion

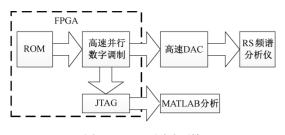

#### 3.2 FPGA 实现

为了对 FPGA 的实现结果进行测试验证,本文设计了图 10 所示的测试环境,其中 ROM 存入了图 7 的标准 QPSK 信号,由 JTAG 调试接口可以获取高速并

行调制架构中的数据,然后可以导入 MATLAB 进行对比分析。

图 10 FPGA 测试环境 Fig. 10 FPGA test environment

图 11 (a) 为从 FPGA 获取的并行频域成型滤波后的 QPSK 星座图,与图 8 (a)中的 MATLAB 仿真实验室对比发现,QPSK 星座图幅值几乎一致;图 11 (b) 为相应的成型滤波器后的频谱图。可以看出,频谱在零中频,中频分析带宽为 0. 175×3 200 = 560 MHz,与图 8 (b)显示的仿真结果一致。上述对比说明了本文设计的 FPGA 并行频域成型滤波算法的有效性。

图 11 FPGA 中成型滤波 Fig. 11 Forming filter in FPGA

图 12 展示了从 FPGA 获取的免混频数字正交上变频后的频谱图,图中载波频率为 0.25×3 200 = 800 MHz,中频分析带宽为 560 MHz。这表明了本文设计的免混频数字正交上变频 FPGA 实现方法的可行性。

图 12 FPGA 中数字正交上变频后频谱 Fig. 12 Spectrum after digital orthogonal up-conversion in FPGA

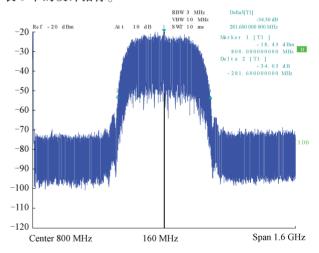

图 13 是将高速 DAC 输出的模拟信号接入 RS 频谱 仪显示的频谱。图中显示载波频率为 800 MHz, 带宽为 560 MHz。另外, 频谱的动态范围大于 50 dBm, 可以满足表 1 中的设计指标。

图 13 RS 中频谱 Fig. 13 Spectrum in RS

### 4 结 论

本文设计了一种适用于 FPGA 硬件实现的全并行数 字调制架构,该架构可以在较低时钟频率下实现高符号 率信号的调制。基于设计的高速数字调制架构,可以在 FPGA 中实现 800 MHz 载波频率、400 MHz 符号率的 QPSK 信号调制。另外,该架构具有较强的可移植性,对 于高阶调制格式和更高符号率,只需要相应扩展架构即可实现调制信号的发射。

#### 参考文献

- [ 1 ] TZANAKAKI A, ANASTASOPOULOS M P, ZERVAS G S, et al. Virtualization of heterogeneous wireless-optical network and IT infrastructures in support of cloud and mobile cloud services [ J ]. IEEE Communications Magazine, 2013, 51(8): 155-161.

- [2] VASHIS, RAM J, MODI J, et al. Internet of things (IoT): A vision, architectural elements, and security issues [C]. IEEE International Conference on I-smac, 2017.

- [ 3 ] FOTOUHI A, QIANG H, DING M, et al. Survey on UAV cellular communications: Practical aspects, standardization advancements, regulation, and security challenges [ J ]. IEEE Communications Surveys and Tutorials, 2019; 3417-3442.

- [4] PENG J, GAO H, LIU L, et al. FNTAR: A future network topology-aware routing protocol in UAV networks[C]. IEEE Wireless Communications and Networking Conference, 2020.

- [5] 林长星. 2 Gbps 高速通信解调技术及其实现研究[D]. 北京:清华大学, 2012.

LIN CH X. Research on 2 Gbps high-speed communication demodulation technology and its implementation[D]. Beijing: Tsinghua University, 2012.

- [6] 崔文涛, 李杰, 张德彪, 等. 基于国产 ADC 芯片的 TIADC 系统时间误差自适应校准算法[J]. 仪器仪表 学报,2021,42(11): 132-139.

CUI W T, LI J, ZHANG D B, et al. TIADC system time error adaptive calibration algorithm based on domestic ADC chip[J]. Chinese Journal of Scientific Instrument, 2021, 42(11): 132-139.

- [7] 车克龙,廖薇,周灵丽. 超宽带信号在运动人体下阴影衰落对通信性能的影响[J]. 电子测量与仪器学报, 2022,36(5):155-162.

CHE K L, LIAO W, ZHOU L L. Influence of shadow fading of UWB signal under movinghuman body on communication performance [J]. Journal of Electronic Measurement and Instrumentation, 2022, 36(5): 155-162.

- [8] 王俭. QPSK 全数字中频调制解调器的 FPGA 实现[D]. 西安:西安电子科技大学, 2013. WANG J. FPGA implementation of QPSK full digital

- intermediate frequency modem [ D ]. Xi' an: Xidian University, 2013.

- [9] 周钦. 星载高速高阶 QAM 调制技术设计与实现[D]. 西安: 西安电子科技大学, 2014.

ZHOU Q. Design and implementation of spaceborne high-speed high-order QAM modulation technology [D].

Xi'an: Xidian University, 2014.

- [10] 范永辉, 王宪栋, 石奇鑫, 等. 2015 年各国航天发射活动回顾[J]. 中国航天, 2016, 26(3): 33-37. FANG Y H, WANG X D, SHI Q X, et al. Review of space launch activities of various countries in 2015[J]. China Aerospace, 2016, 26(3): 33-37.

- [11] BENEDETTO S, GARELLO R, MONTORSI G.

MHOMS: High-speed ACM modem for satellite

applications[J]. IEEE Wireless Communications, 2008,

12(2): 66-77.

- [12] 朱露敏. 高速多制式矢量解调器解调通用处理模块的设计与实现[D]. 成都: 电子科技大学, 2016.

ZHU L M. Design and implementation of high-speed multi-system vector demodulation general processing module[D]. Chengdu: University of Electronic Science and Technology of China, 2016.

- [13] OGAWA Y, HASHIMOTO Y, YOSHIMURA N, et al. 622 Mbps HIGH-speed satellite communication system for WINDS[J]. Acta Astronautica, 2006, 59(5):96-99.

- [14] 肖磊. 并行高速通信解调系统中同步技术的研究与实现[D]. 成都: 电子科技大学, 2017.

XIAO L. Research and implementation of synchronization technology in parallel high-speed communication demodulation system [D]. Chengdu: University of Electronic Science and Technology of China, 2017.

- [15] 陈晖,郝志松,王正. 超高符号率数字均衡技术研究与实现[J]. 电子测量与仪器学报, 2013, 27(1): 26-31. CHEN H, HAO ZH S, WANG ZH. Research and implementation of high symbol rate digital equalization technology[J]. Journal of Electronic Measurement and Instrumentation, 2013, 27(1): 26-31.

- [16] 陈晖, 易克初, 李文铎. 高速解调中的并行处理算法[J]. 电子与科技大学学报, 2012, 9(3): 40-345. CHEN H, YI K CH, LI W D. Parallel processing algorithm for high speed demodulation [J]. Ournal of University of Electronic Science and Technology of China, 2012, 9(3): 40-345.

#### 作者简介

李浩,2020年于电子科技大学获得博士 学位,现为电子科技大学自动化工程学院助 理研究员,主要研究方向为通信测试技术。

E-mail: haoli@ uestc. edu. cn

Li Hao received his Ph. D. degree from

University of Electronic Science and Technology of China (UESTC) in 2020. He is currently a research assistant with the School of Automation Engineering at UESTC. His main research interest is communication test technology.

**王厚军**,1991年于电子科技大学获得博士学位,现为电子科技大学自动化工程学院教授,主要研究方向为通信测试技术。

E-mail: hjwang @ uestc. edu. cn

Wang Houjun received his Ph. D. degree

from UESTC in 1991. He is currently a professor with the School of Automation Engineering at UESTC. His main research interest is communication test technology.

**肖磊**,2017年于电子科技大学获得硕士 学位,现为中国电子科技集团公司航空电子 信息系统技术重点实验室工程师,主要研究 方向为通信测试技术。

E-mail: 905702112@ qq. com

Xiao Lei received his M. Sc. degree from UESTC in 2017. He

is currently an engineer at CETC Key Laboratory of Avionic Information System Technology. His main research interest is communication test technology.

**王志刚**(通信作者),1982年于电子科 技大学获得硕士学位,现为电子科技大学自 动化工程学院教授,主要研究方向为通信测 试技术。

E-mail: wangzhigang@ uestc. edu. cn

Wang Zhigang (Corresponding author) received his M. Sc. degree from UESTC in 1982. He is currently a professor with the School of Automation Engineering at UESTC. His main research interest is communication test technology.

李涛,2017年于中北大学获得硕士学位,现为山西省检验检测中心(山西省标准计量技术研究院)助理工程师,主要研究方向为现代测试技术。

E-mail: 631055037@ qq. com

Li Tao received his M. Sc. degree from UESTC in 2017. He is currently an assistant engineer at Inspection and Testing Center of Shanxi Province (Institute of Standard Metrology of Shanxi Province). His main research interest is modern test technology.