# 针对逻辑门功能异常的 VLSI 故障仿真方法研究

戴金玲1 许爱强2 王 栋3 唐小峰2,4

(1. 海军航空工程学院研究生二队 烟台 264001;2. 海军航空工程学院科研部 烟台 264001;3. 海军航空工程学院飞行器工程系 烟台 264001;4. 中国人民解放军 92514 部队 烟台 264007)

摘 要:为准确评价测试集对超大规模集成电路(VLSI)内部故障的覆盖效果,提出一种 VLSI 故障建模与仿真方法。首先,在电路级综合运用仿真和实验手段向逻辑门内部注入多个故障,统计并分析这些故障对其功能的影响以构建由变异真值表(MTT)组成的故障字典;其次,考虑 MTT 及其发生的相对概率权重,提出一种有效的测试覆盖率评价模型,并将其应用于门级故障仿真算法中;最后,针对若干组合逻辑基准电路进行了实例验证,仿真实验结果表明,所提方法相较于经典的固定值故障模型能够更真实地反映测试集的故障覆盖能力。

关键词:超大规模集成电路(VLSI)测试;故障建模;故障仿真;故障覆盖率;变异真值表(MTT)

中图分类号: TP399 TN47 文献标识码:A 国家标准学科分类代码: 460.40

# Fault simulation of VLSI based on functional fails of logic gate

Dai Jinling <sup>1</sup> Xu Aiqiang<sup>2</sup> Wang Dong<sup>3</sup> Tang Xiaofeng<sup>2,4</sup>

- (1. Graduate Student Team Two, Naval Aeronautical and Astronautical University, Yantai 264001, China;

- 2. Department of Scientific Research, Naval Aeronautical and Astronautical University, Yantai 264001, China;

- 3. Department of Airborne Vehicle Engineering, Naval Aeronautical and Astronautical University, Yantai 264001, China; 4. Unit 92514 of the PLA, Yantai 264007, China)

Abstract: In order to evaluate the fault coverage in VLSI accurately, a new logic fault modeling and simulation method is proposed in this paper. Firstly, the circuit-level faults are injected into the logic cells by simulation and experiments, and the fault dictionary consisted of MTTs is built by analyzing the experimental data. Secondly, an effective testing coverage model is proposed based on the MTTs and their weights, which are then applied to the gate-level fault simulation. At Last, the proposed method is proved on several combinational benchmark circuits. The results show that, comparing to the traditional stack-at fault model, the proposed method can better reflect the fault coverage capability of a given testing set

Keywords: VLSI testing; fault modeling; fault simulation; fault coverage rate; mutated truth table (MTT)

### 1 引 言

提高测试集对真实故障的覆盖率一直是超大规模集成电路(very large scale integration, VLSI)测试领域的一个重要课题。故障模型的质量直接决定着测试集的质量。固定值故障(stuck-at fault, SAF)模型一直在数字电路测试领域扮演主要角色[1-3],但有研究表明仍有许多故障不能由 SAF 表示<sup>[4]</sup>。因此,近年来不断有新的故障模型和仿真测试方法被相继提出。文献[5]在电路级对 CMOS逻辑门中的各种常见故障进行了仿真分析,并归纳整理出

SAF、不定态、延时等多种门级故障模型;文献[6]基于静态电源电流测试方法对逻辑门内部的桥接故障进行了仿真测试,并给出了针对这类故障的测试覆盖率计算方法;文献[7]通过延时仿真算法对电阻式开路故障进行仿真和诊断,通过较小的计算量实现了对开路故障的精确定位;文献[8]基于功能测试对时序电路中所建立的路径延时故障模型进行仿真,并得到较其他方法更高的故障覆盖率。就逻辑单元内部故障引起的功能异常而言,现有的研究尚未给出较为全面的描述模型。

本文针对 VLSI 中的基本逻辑门,首先基于其内部的

收稿日期:2016-06

电路级故障模型,综合运用仿真和实验手段确定其外部故障模式以及这些故障模式发生的相对概率权重,并构建其故障字典。然后,针对故障字典中存储的故障模式信息,提出一种测试覆盖率模型以及门级故障仿真算法,以更真实地评价测试集对被测电路(circuit under test,CUT)内部故障的覆盖能力。

### 2 故障字典

### 2.1 电路级故障模型

一个逻辑门在底层是由多个晶体管通过导线互连而成,为研究逻辑门的外部故障行为,本文主要分析以下两种内部故障:

1)开路故障(open fault,OF)。OF 发生于元器件的端口或电气节点上,在仿真时通常用一个高阻值的开路电阻与目标端口串联来模拟元器件上的 OF。对于节点开路,为避免与元器件端口上的开路在效果上重复,只考虑连线数量≥4的节点被分为两组的情况,并且要求分裂所得的新节点上连线数量≥2;

2) 桥接故障(bridging fault, BF)。BF 发生于一对原本互不相连的电气节点上(称为节点对),在仿真时通常用一个低阻值电阻桥接于组成目标节点对的两个节点之间。

上述故障改变了目标电路的拓扑结构,称为硬故障;与之对应的软故障则是指晶体管的工艺或模型参数超出规定容差的情况。与硬故障容易造成逻辑门功能失效不同,软故障通常只是导致逻辑门的性能下降。本文主要研究内部故障[9-10]对逻辑门功能(即真值表)的影响,因此不考虑软故障模型。

#### 2.2 故障字典的内容和结构

对于任意的逻辑门类型 G,假设其输入和输出端口数量分别为 m 和 n,正常状态时该逻辑门类型的真值表为  $T_G$ ,是一个  $2^m \times (m+n)$  的矩阵,其中前 m 列(输入列)为输入逻辑值组合,后 n 列(输出列)为每个输入向量对应的输出值。当 G 的内部电路中有故障时,若其对应的真值表  $T_G^* \neq T_G$ ,则称  $T_G^*$  为逻辑门类型 G 的一个变异真值表 (mutated truth table,MTT)。实际上,真值表中输入列部分是不变的,因此  $T_G^*$  与  $T_G$  的区别仅在于输出列中的逻辑值不同。

显然,G 中包含不止一种的内部故障,因此通常存在多个与这些内部故障相对应的 MTT,它们即构成了该逻辑门类型 G 的故障字典,记为  $\mathbf{D}_G = \{ \langle T_{G,k}^*, \omega_{G,k} \rangle | k = 1,2,\ldots,N_G \}$ ,其中  $N_G$  表示 MTT 的数量; $\omega_{G,k}$  表示  $T_{G,k}^*$  出现概率的归一化相对权重,其计算公式如式(1):

$$\omega_{G,k} = \frac{\lambda_{G,k}}{\lambda_G} \tag{1}$$

式中:  $\lambda_G$  表示在 G 中注人故障的总数;  $\lambda_{G,k}$  表示对应的 MTT 等于  $T_{G,k}^*$  的故障的数量。显然,一个 MTT 对应的 内部故障数量越多,它在逻辑门的故障行为空间中出现的

概率就越大。

当 CUT 由多种类型的逻辑门组成时,需为每种逻辑门构建相应的故障字典,它们的集合即为整个 CUT 的故障字典,记为  $\mathbf{D} = \{D_{G_i} \mid i = 1, 2, \dots, N\}$ ,其中  $D_{G_i}$  表示第 i 类逻辑门的故障字典。

### 2.3 故障字典的构建方法

考虑到某些故障的仿真结果与实际情况不一致,本文结合电路级故障仿真和实物电路实验来构建 CUT 的故障字典。令  $\mathbf{F} = \{f_i \mid i=1,2,\ldots,N_F\}$  表示目标故障集,故障字典构造的具体过程如下所示:

Step1. 给定逻辑门的内部电路原理图,使用文献[9]提出的电路变异实验工具 CMLab 对其进行自动故障注人操作,按变异配置生成该逻辑门的故障电路实例(在文献 [11-12]中称为变异体),得到  $\mathbf{F}$ ;

Step2. 对 F 中的每个元素 f, 及其对应的故障电路, 调用 PSpice 仿真程序对其进行瞬态分析, 在输出端采集逻辑门电路的故障响应(对于仿真结果可信度低的故障, 该步骤则由实物电路实验完成):

Step3. 对采集到的模拟信号进行数字量化,即确定逻辑值对应的电压范围,并为当前逻辑门类型构造相应的MTT,若MTT等于正常真值表则忽略之,否则将其保存到故障字典  $D_G$  中并进行同类合并,同时更新其权重,返回Step2;

Step4. 合并 CUT 中每个逻辑门类型的故障字典,最终构成完整的故障字典 D。

### 3 门级故障仿真

### 3.1 实现框架

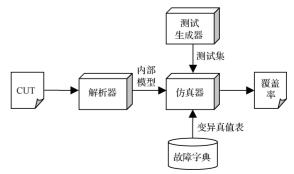

门级故障仿真的实现框架如图 1 所示,其中:

- 1)解析器负责将文本格式的 CUT 门级网表解析为一种方便计算机处理的内部模型;

- 2)测试生成器用于随机生成规定数量的输入测试序列,即测试集:

- 3)仿真器应用一种事件驱动的仿真算法<sup>[6,13]</sup>,既能对 CUT 进行功能仿真,也能通过查询每个逻辑门对应的故 障字典,实现故障仿真。

图 1 门级故障仿真框架

# 理论与方法

### 3.2 测试覆盖率模型

设  $CUT = \{g_i \mid i = 1, 2, ..., N_g\}$ , 其中  $g_i$  表示该 CUT 中一个逻辑门的实例, 并假定每个逻辑门实例上发生故障的概率相等。令测试集为  $TS = \{t_i \mid j = 1, 2, ..., N_{TS}\}$ , 其中  $t_j$  表示一个测试序列。那么,测试序列  $t_j$  对 CUT 中的任意一个逻辑门实例  $g_i$  上的 MTT 的覆盖率定义为:

$$FC_{j,i} = rac{1}{N_g} \sum_{k=1}^{N_{G(g_j)}} \omega_{G(g_j),k} \; ,$$

根据式(2),可得 $t_i$ 对 CUT 中所有 MTT 的覆盖率为:

$$FC_{j} = \sum_{i=1}^{N_{s}} FC_{j,i} \tag{3}$$

进一步可得测试集 TS 对 CUT 中所有 MTT 的覆盖率为:

$$FC = \sum_{i=1}^{N_{rs}} FC_i \tag{4}$$

### 3.3 门级故障仿真算法

门级故障仿真以事件驱动的功能仿真算法为基础<sup>[6]</sup>,即以 CUT 端口和内部连线上信号逻辑值的变化为事件,以此来驱动逻辑门的执行,直到没有新事件发生为止。基于这种方法,在仿真故障时只需根据故障字典中的信息更改某根连线上的逻辑值,即可通过产生的事件自动执行故障仿真过程。具体算法如下所示:

Step1. 将测试集 TS 中的每个测试序列  $t_j(j=1,2,\ldots,N_{TS})$  依次加到 CUT 输入端,仿真后得到 CUT 在  $t_i$  下的正常输出;

Step2. 对 CUT 中的每个逻辑门实例  $g_j(i=1,2,\ldots,N_g)$ ,从故障字典 D 中查询与  $g_j$  所属逻辑门类型 G 相对应的故障字典  $\mathbf{D}_{G(g)}$ ;

Step3. 对故障字典  $D_{G(g_i)}$  中的每个元素  $< T^*_{G(g_i),k}$ ,  $\omega_{G(g_i),k} > (k=1,2,\ldots,N_{G(g_i)})$ , 根据  $g_i$  当前输入连线上的逻辑值在每个 MTT(即  $T^*_{G(g_i),k}$ )中查询对应的输出值,若该输出值与  $g_i$  正常时不同,则产生一个事件,由此驱动后续逻辑门的仿真;若最终得到的 CUT 输出不同于正常输出,则表明  $T^*_{G(g_i),k}$  被  $t_i$  覆盖,按(2)式计算  $t_i$  对  $g_i$  的覆盖率,并置  $flag_{G(g_i),k}$  为 1。将 CUT 内部连线的逻辑值恢复至正常状态,然后返回 Step2;

Step4. 按(3)式计算  $t_j$  对 CUT 的覆盖率,然后返回 Step1,直到遍历**TS**中所有测试序列为止;最后按(4)式计

算 TS 对 CUT 的覆盖率。

## 4 仿真实验与结果分析

下面以 CMOS(complimentary metal-oxide-semiconductor)工艺的逻辑门<sup>[14]</sup>及其构成的 CUT 为例对所提方法进行说明。首先,为基本的逻辑门类型构建故障字典,包括非门(Inv),缓存器(Buff)以及两输入的与非门(Nand2)、或非门(Nor2)、与门(And2)、或门(Or2)和异或门(Xor2)。

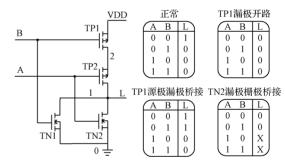

以图 2 所示的 Nor2 逻辑门为例,图中左侧为该逻辑门的内部电路原理,右侧为相应的真值表以及若干 MTT示例。例如,当 TP1 漏极开路时,输出端 L 与供电电源的通路被切断,因此其逻辑值将固定在低电平。当 TP1 源极与漏极桥接时,TP2 源极直接与供电电源相连,此时电路逻辑功能变为以 A 为输入、L 为输出的非门,输出 L 的逻辑值与 A 的逻辑值正好相反。当 TN2 漏极与栅极桥接时(L 与 A 相连),当 A 为低电平时 TN2 截止,L 与 A 的逻辑值相同;当 A 为高电平时,TN2 导通,并与前级驱动电路中导通的晶体管相连,形成一个由导通电阻构成的分压电路,L 的逻辑值取决于中间点的电压,通常为不定态'X'。

图 2 两输入或非门电路原理与 MTT 示例

如表 1 所示为 Nor2 逻辑门的所有内部故障。从图 2 所示原理图可见,或非门中不存在连线数量 > 4 的节点,因此表 1 中只有元器件端口的开路故障。而电路结构相对复杂的与门、或门和异或门就需要考虑节点开路问题。

如表 2 所示为 Nor2 逻辑门类型关联的故障字典,其中第 1 列为编号,第 2 列为 MTT(简洁起见,表中只列出了输出列的值),第 3 列为 MTT 对应的权重,第 4 列为能够导致该 MTT 出现的内部故障。在第 2 列 MTT 中,考虑逻辑门的噪声容限,设不定态'X'的输出电压范围为[1.5 V,3.5 V],逻辑'0'和逻辑'1'的输出电压分别为[0 V,1.5 V)和(3.5 V,5 V]。

仿真实验结果表明:

1)向逻辑门电路中注入硬故障均会引起功能异常,而功能异常的具体形式与故障发生的位置有关;

表 1 两输入或非门内部故障类别

|          |            | 1        |            |

|----------|------------|----------|------------|

| 标识       | 描述         | 标识       | 描述         |

| $f_1$    | TN1 漏极开路   | $f_{15}$ | TP1 栅极开路   |

| $f_2$    | TN1 源极开路   | $f_{16}$ | TP1 漏极栅极桥接 |

| $f_3$    | TN1 栅极开路   | $f_{17}$ | TP1 栅极源极桥接 |

| $f_4$    | TN1 漏极栅极桥接 | $f_{18}$ | TP1 源极漏极桥接 |

| $f_5$    | TN1 栅极源极桥接 | $f_{19}$ | TP2 漏极开路   |

| $f_6$    | TN1 源极漏极桥接 | $f_{20}$ | TP2 源极开路   |

| $f_7$    | TN2 漏极开路   | $f_{21}$ | TP2 栅极开路   |

| $f_8$    | TN2 源极开路   | $f_{22}$ | TP2 漏极栅极桥接 |

| $f_9$    | TN2 栅极开路   | $f_{23}$ | TP2 栅极源极桥接 |

| $f_{10}$ | TN2 漏极栅极桥接 | $f_{24}$ | TP2 源极漏极桥接 |

| $f_{11}$ | TN2 栅极源极桥接 | $f_{25}$ | (A,B)桥接    |

| $f_{12}$ | TN2 源极漏极桥接 | $f_{26}$ | (2,0)桥接    |

| $f_{13}$ | TP1 漏极开路   | $f_{27}$ | (VDD, L)桥接 |

| $f_{14}$ | TP1 源极开路   | $f_{28}$ | (VDD, A)桥接 |

表 2 两输入或非门的故障字典

| ID | $T_G^*$            | $\omega_G$ | 内部故障                                                                                          |

|----|--------------------|------------|-----------------------------------------------------------------------------------------------|

| 1  | $[1, X, 1, 0]^{T}$ | 0.107      | $f_1$ , $f_2$ , $f_3$ ,                                                                       |

| 2  | $[0, 1, 0, 1]^{T}$ | 0.036      | $f_4$                                                                                         |

| 3  | $[1, 0, 1, 0]^{T}$ | 0.071      | $f_{\scriptscriptstyle 5}$ , $f_{\scriptscriptstyle 24}$                                      |

| 4  | $[0, 0, 0, 0]^{T}$ | 0.321      | $f_6$ , $f_{12}$ , $f_{13}$ , $f_{14}$ , $f_{17}$ , $f_{19}$ , $f_{20}$ , $f_{26}$ , $f_{28}$ |

| 5  | $[1, 1, X, 0]^{T}$ | 0.107      | $f_7$ , $f_8$ , $f_9$                                                                         |

| 6  | $[0, 0, 1, 1]^{T}$ | 0.071      | $f_{10}$ , $f_{22}$                                                                           |

| 7  | $[1, 1, 0, 0]^{T}$ | 0.071      | $f_{11}$ , $f_{18}$                                                                           |

| 8  | $[1, X, 0, 0]^T$   | 0.036      | $f_{15}$                                                                                      |

| 9  | $[0, 1, 0, 0]^{T}$ | 0.036      | $f_{16}$                                                                                      |

| 10 | $[1, 0, X, 0]^{T}$ | 0.036      | $f_{21}$                                                                                      |

| 11 | $[X,0,X,0]^T$      | 0.036      | $f_{23}$                                                                                      |

| 12 | $[1,X,X,0]^T$      | 0.036      | $f_{25}$                                                                                      |

| 13 | $[1, 1, 1, 1]^{T}$ | 0.036      | $f_{27}$                                                                                      |

2)含不定态'X'逻辑值的 MTT 种类约占 MTT 总数的一半。说明不定态是一种常见的逻辑门外部故障模式;

3)固定 0 故障出现的次数最多,其权重为 0.321,固定值(包括固定 0 和固定 1)故障的权重为 0.357,高于其他任何一种故障类型,可见,固定值故障仍然是一类重要的故障模式。

4)非固定值故障的 MTT 的权重之和为 0.643,超过 50%,由此可见,经典的固定值故障模型并不足以代表数 字电路中存在的大多数真实故障。

如表 3 所示为针对若干组合逻辑基准电路的故障仿真结果。第 1 列为 CUT 的名称,第 2 列和第 5 列为随机生成的测试系列数量;第 3 列和第 6 列为由本文所提方法得出的测试覆盖率;第 4 列和第 7 列为仿真时间消耗(仿真实验在 3 GHz CPU、4 GB RAM 的计算机上执行)。表

3 中,只有 c17 的测试集规模为 V=32(已穷举其所有输入组合),其他基准电路的测试集规模均分别为  $10^3$  和  $10^4$  。

由表 3 所示结果可见:

1)随着 CUT 的规模不断增大,测试覆盖率并未表现 出某种规律性,说明测试覆盖率和 CUT 的复杂度没有必 然联系;

表 3 组合基准电路门级故障仿真结果

| CUT   | V        | FC(%) | T(s)   | V        | FC(%) | T(s)     |

|-------|----------|-------|--------|----------|-------|----------|

| c17   | 32       | 100   | _      | 32       | 100   | _        |

| c432  | $10^{3}$ | 95.6  | 1.27   | $10^{4}$ | 96.5  | 9.75     |

| c499  | $10^{3}$ | 99.4  | 1.81   | $10^{4}$ | 99.9  | 11.82    |

| c880  | $10^{3}$ | 95.7  | 5.97   | $10^{4}$ | 96.9  | 53.47    |

| c1355 | $10^{3}$ | 95.4  | 6.09   | $10^{4}$ | 97.1  | 53.95    |

| c1908 | $10^{3}$ | 88.2  | 43.37  | $10^{4}$ | 89.1  | 350.57   |

| c2670 | $10^{3}$ | 80.8  | 150.21 | $10^{4}$ | 81.0  | 1 393.41 |

| c3540 | $10^{3}$ | 78.4  | 259.71 | $10^{4}$ | 83.4  | 1 934.73 |

| c5315 | $10^{3}$ | 96.4  | 267.32 | $10^{4}$ | 96.5  | 2 181.30 |

| c6288 | $10^{3}$ | 93.6  | 197.49 | $10^{4}$ | 93.6  | 1 922.55 |

| c7552 | $10^{3}$ | 90.7  | 655.31 | $10^{4}$ | 92.6  | 5 106.94 |

2)CUT 的故障仿真时间与其电路规模和测试集规模成正比;

3)测试集规模为 10<sup>3</sup> 时,其测试覆盖率与规模为 10<sup>4</sup> 时的覆盖率在多数情况下相差无几。由此可见,当测试集规模达到一定程度后,继续增加测试序列不一定能取得显著效果。实际应用中,应综合考虑时间成本和故障覆盖率水平,得到一个较优的测试集。

### 5 结 论

本文从底层的电路级故障出发,针对数字电路中的逻辑门功能异常构建了故障字典,其具体内容为不同内部故障对应的变异真值表(MTT)的集合。基于得到的不同逻辑门类型的故障字典,提出一种新的覆盖率模型,用以衡量测试集的质量,并开发了相应的门级故障仿真算法。针对若干组合逻辑基准电路的故障仿真实验结果表明所提方法能够更真实地反映测试集的故障覆盖能力。后续将进一步基于所得的逻辑门故障模式,研究相应的测试向量优化生成技术。

### 参考文献

- [1] FAN X Y, Will M, CAMELIA H, et al. A novel stuck-at based method for transistor stuck—open fault diagnosis [C]. Proceedings of IEEE International Test Conference, 2005;1-9.

- [2] PIET E, ILIA P, BERND B. Simulating resistive-bridging and stuck-at faults [J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2006, 25(10):2181-2192.

- [3] 陈绍炜,柳光峰,冶帅,等. 基于蝙蝠算法优化 ELM

# 理论与方法

- 的模拟电路故障诊断研究[J]. 电子测量技术,2015,38(2):138-141.

- [4] IRITH P, REDDY S M. A bridging fault model where undetectable faults imply logic redundancy[C]. Proceedings of 2008 Design, Automation and Test in Europe, 2008;1166-1171.

- [5] TANG X F, XU A Q, LI W H, et al. Fault models of CMOS gates: an empirical study based on mutation analysis [C]. Proceedings of IEEE International Conference on Software Engineering and Service Sciences, 2014:916-920.

- [6] 许爱强, 唐小峰, 牛双诚, 等. 基于 IDDQ 测试的 VL-SI 门内电阻式桥接故障仿真研究[J]. 北京工业大学学报, 2016, 42(1):128-133.

- [7] KOJI Y, TOSHIYUKI T, HIROYUKI Y, et al. A method for diagnosing resistive open faults with considering adjacent lines [C]. Proceedings of IEEE International Symposium on Communications and Information Technologies, 2010;609-614.

- [8] MAHILCHI M V K, SPYROS T, SREEJIT C. Exact delay fault coverage in sequential logic under any delay fault model [J]. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2006, 25(12):2954-2964.

- [9] 李曼,王彩利,龙兵,等. 多特征故障字典及其在模拟电路可测性分析中应用[J]. 电子测量与仪器学报,2015,29(3):368-373.

- [10] 谈恩民,何正岭.模拟电路故障重叠诊断方法研究[J]. 国外电子测量技术,2015,34(6):33-36.

- [11] 唐小峰,许爱强,李文海. 多层次模拟电路随机变异 生成方法研究[J]. 中国测试,2016,42(1):12-15.

- [12] JIA Y, HARMAN M. An analysis and survey of the development of mutation testing [C]. IEEE Transactions on Software Engineering, 2011, 37 (5): 649-678.

- [13] 王新安, 蒋安平, 宋春殚, 等. 数字系统测试[M]. 北京:电子工业出版社, 2007:42-94.

- [14] 康华光, 皱寿彬, 秦臻, 等. 电子技术基础[M]. 北京:高等教育出版社, 2006:76-82.

### 作者简介

戴金玲,1991年出生,女,在读硕士,主要研究方向为 数字电路故障仿真与测试生成技术。

E-mail: 904227878@qq. com

许爱强,1963年出生,男,教授,主要研究方向为电子信息系统测试与诊断技术研究。

E-mail: xuaiqiang1963@163. com

王栋,1986年出生,男,讲师,主要研究方向为装备系统工程与故障诊断理论。

E-mail:1159416532@qq.com

唐小峰,1984年出生,男,在读博士,主要研究方向为 电子信息系统测试性理论与应用。

E-mail:vivorimage@126.com