# 基于正交锁定结构的高精度阻抗分析仪设计<sup>\*</sup>

李松凯<sup>1</sup> 关贝贝<sup>2</sup> 刘金海<sup>3</sup>

(1. 东北大学保密委员会办公室 沈阳 110819; 2. 东北大学计算机科学与工程学院 沈阳 110819;

3. 东北大学信息科学与工程学院 沈阳 110819)

**摘要:** 精密测量技术在生物医学阻抗分析、电化学、电力传输、射频天线分析等诸多分析仪器领域,一直作为核心技术而存在。现代的精密测量仪器中,阻容的数量动辄成百上千,并且对其阻抗参数要求极为严苛,所使用的阻容质量以及其自身阻抗值的稳定性是影响电子系统性能的一个重要因素,因此精密阻容测量成为诸多电子系统设计中重要的一环。在这一背景下,本文提出一种以硬件正交锁相结构为核心的高精度阻容分析仪。该设计以硬件正交鉴相为核心,围绕该部分设计了正交频率发生器、I-V转换调节模块、Sallen-Key滤波器等硬件结构,同时设计了用于模块控制与驱动、任务分配与调度以及数据采集与处理的单片机系统。最后对系统关键部件及实物整机进行性能测试,实现了对阻容的判断以及阻抗值的测量。经过系统实际测试并与标准电桥测试进行比对,该系统对于电阻测量误差的均值为0.032 4%,对于电容测量误差的均值为0.054 7%。并且在实现较低的测量误差的同时,保证了整体系统的小体积以及便携性,最终使设计达到预期目标。

**关键词:** 阻容测量;正交鉴相;矢量测量;单片机系统设计;信号调理与滤波;数字信号处理

**中图分类号:** TN98    **文献标识码:** A    **国家标准学科分类代码:** 510.4010

## Design of high-precision impedance analyzer based on orthogonal locking structure

Li Songkai<sup>1</sup> Guan Beibei<sup>2</sup> Liu Jinhai<sup>3</sup>

(1. Security Committee, Northeastern University, Shenyang 110819, China;

2. College of Computer Science and Engineering, Northeastern University, Shenyang 110819, China;

3. College of Information Science and Engineering, Northeastern University, Shenyang 110819, China)

**Abstract:** Precision measurement technology has always been the core technology in the fields of biomedical impedance analysis, electrochemistry, power transmission, radio frequency antenna analysis and many other analytical instruments. In modern precision measuring instruments, the number of resistance-capacitance is often hundreds of thousands, and the impedance parameters are very strict, the quality of the resistance-capacitance used and the stability of its own impedance value is an important factor affecting the performance of electronic systems, so the precision resistance-capacitance measurement has become an important part of the design of many electronic systems. Under this background, a high precision resistance-capacitance analyzer based on hardware orthogonal phase-locked structure is proposed in this paper. The design takes hardware orthogonal phase discrimination as the core. Around this part, the orthogonal frequency generator, I-V conversion regulation module, Sallen-Key filter and other hardware structures are designed. At the same time, the MCU system is designed for module control and drive, task allocation and scheduling, and data acquisition and processing. Finally, performance tests were conducted on the key components of the system and the physical complete machine, achieving the judgment of resistance and capacitance as well as the measurement of impedance values. After the actual system test and comparison with the standard bridge test, the average value of the resistance measurement error of this system is 0.032 4%, and the average value of the capacitance measurement error is 0.054 7%. And while achieving a lower measurement error, it ensures the small volume and portability of the overall system, ultimately enabling the design to reach the expected goal.

**Keywords:** RC measurement; orthogonal phase discrimination; vector measurement; microcontroller system design; signal conditioning and filtering; digital signal processing

## 0 引言

现代科学技术的发展已经进入了集成化、数字化、信息

化时代,对各类电子系统的性能要求逐渐提升,阻容的质量及其关键阻抗参数是决定电子系统性能的一个重要因素。准确可靠的阻抗测量成为军用及民用电子至关重要的技

术。阻容精密测量技术广泛运用于生物医学阻抗分析、电化学、电力传输、射频天线分析等诸多技术领域<sup>[1-5]</sup>。

常见的阻抗测量方法有电桥法、谐振法以及矢量电压电流法<sup>[6-8]</sup>。电桥法可以获得较高的测量精度,但它需要反复调节使得电桥平衡,测量简单阻抗通常需要 10~30 s,在面对高频、非线性元件等复杂阻抗时需要分钟级的平衡时间,测量速度较慢。谐振法是利用谐振回路的谐振特性而建立的测量方法,在低频部分(2~20 kHz)精度可达到 0.1% 以上,但面对 50 kHz 以上的测量时,寄生电容、线路电感等分布参数将引入显著误差,从而导致测量精度具有较大的局限性。

由于待测阻抗存在多种情况,因此需要通过矢量电压电流法测量测得阻抗角,从而判断阻抗类型。矢量电压电流检测法的核心在于相位检测<sup>[9-11]</sup>,而在相敏检波器的设计中存在两种鉴相方式,乘法鉴相与脉冲积分鉴相。在乘法鉴相中,鉴相器前端出现的直流漂移以及模拟乘法器本身存在的谐波失真会极大地影响鉴相精度,而且模拟乘法器本身造价昂贵。

脉冲积分鉴相本身的特性使得造价相对适中,并且在一定的使用范围内相较于乘法鉴相具有无可比拟的优势。因此本文设计了一种基于矢量电压电流法,采用脉冲积分鉴相的硬件正交锁相放大器的方案,该方案出的突出优势是造价低、测量精度适中,且针对电阻与电容的测量响应速度快。

## 1 总体系统设计要求

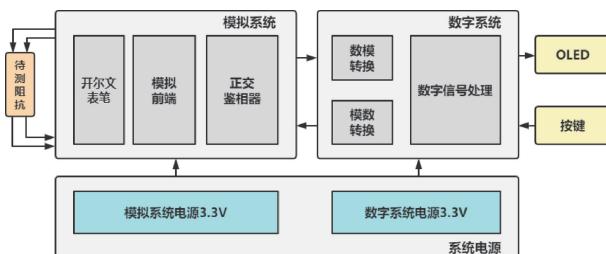

本系统以矢量电压电流法为基础,采用硬件正交鉴相器进行鉴相部分的设计。因此需要模拟前端将激励施加于待测阻抗,对反馈的模拟信号进行处理,并经过正交鉴相器后通过模数转换器进行信号采集,最后送入微控制器(micropogrammed control unit, MCU),在通过一系列数字信号处理后,将最终的计算结果送至显示屏幕进行显示。整体系统框图如图 1 所示。

图 1 整体系统框图

Fig. 1 Overall system block diagram

## 2 硬件系统设计

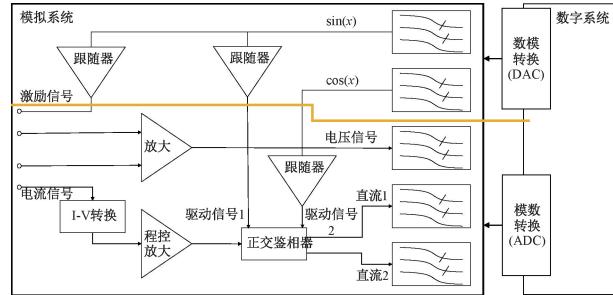

在模拟部分实现中,完成了硬件正交鉴相、仪表放大器、抗混叠滤波器等方案设计,通过一系列硬件电路对信号

进行降噪、放缩、以及鉴相等处理。最后通过微控制器本身的模数转换器(analog to digital conversion, ADC),再次将模拟信号转换为数字信号,送入单片机进行相关处理,系统结构如图 2 所示。

图 2 模拟前端结构

Fig. 2 Analog front circuit structure

### 1) 激励信号模块设计

正交鉴相的激励源同时需要两路信号,因此需要同时驱动两个数模转换器作为激励源,并且保证正交鉴相的两路激励源同频正交。为实现此目标,本文设计方案使用具有两个位数最高为 12 bit 的数模转换器(digital to analog, DAC)的微控制器 STM32F303RBT6,其带宽为 8 bit 位数,刷新速率为 4.5 Msps,能够在满足设计需求的同时尽量降低成本。

以常用的双通道 DDS(direct digital synthesizer, 直接频率合成器)激励信号源 AD9854 为例,其常见单片售价为 600 元。而选择具有双 DAC 通道型号的 STM32F3 系列作为主控制器,相比功能相对简单的 STM32F1 系列,仅增加了 7 元(其中 STM32F3 系列主控常见售价为 19 元,而 STM32F1 系列主控常见售价为 12 元)。并且相比 STM32F1 系列,STM32F3 系列具有更高的主频,在进行数据处理等运算任务时速度更快。综合比较下单片机 DAC 提供激励的方案更具优势。

为了保证两路数模转换器输出正弦波保持正交,在两路输出的阻容器件以及运算放大器的选择上保持了完全一致。同时为了保持流经两路阻容器件以及集成运放的信号尽可能保持对称与完整,在板级布线时尽可能采用了差分对布线设计。

本文的设计方案在相位测算上采用了矢量检测方式,因此需要保证测量信号与正交鉴相器之间的相位保持零相位差,因此在综合考量了可行度、成本以及执行难度后,决定使用跟随器引出正交激励中的一路作为阻抗测量激励,并在布线时对该路进行对应的优化。经过实际验证,此种方法是在不显著增加成本以及不大规模增添硬件设计的情况下,最适宜的解决方案。

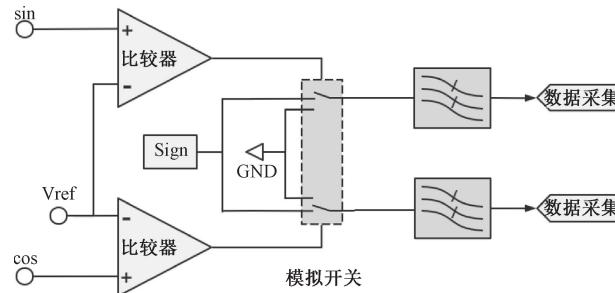

### 2) 正交鉴相模块设计

本设计为了避开传统鉴相器中乘法器会带来非线性失真和直流漂移等的问题,使用了模拟开关 TS5A23159DGSR

来代替通用乘法器,该模拟开关在室温 25℃ 并且 3.3 V 供电下工作时,导通时间与关断时间分别为 11 ns 与 5 ns,其保证方波信号边缘完整的极限频率约为 12.5 MHz,导通电阻为 1 Ω,总谐波失真(total harmonic distortion, THD)为 0.01%,能够实现 100 kHz 的测量需求。

使用了比较器 TLV3202AIDR, 将 DAC 产生的正交正弦波整形为正交方波, 用以驱动 TS5A23159DGSR 进行调制。该比较器传播延时为 40 ns, 输入阻抗典型值为  $10^{13} \Omega$ 。整体设计如图 3 所示。

图 3 正交鉴相结构

Fig. 3 Orthogonal phase detection structure

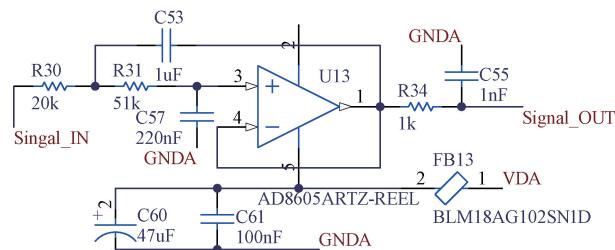

正交鉴相后级连接有源 Sallen-Key 低通滤波器 (Sallen-Key, SK), 滤波器相关阻容设置如图 4 所示, 该滤波器的截止频率  $f_{3db}$  为 100 Hz, 用于消除调制信号的非直流分量。再经过后级的数据采集系统进行采集以及数据计算, 即可达到硬件鉴相的效果。

图 4 SK 低通滤波器原理图设计

Fig. 4 SK low pass filter schematic design

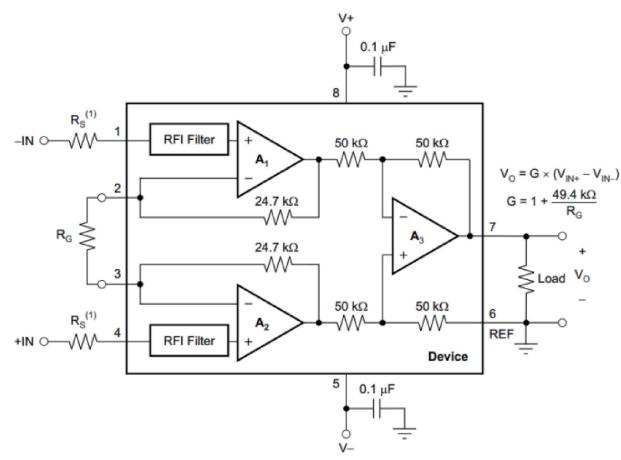

### 3) 仪表放大器模块设计

根据放大器原理可知三仪表放大器中的4个电阻的匹配度会严重影响该放大器的共模抑制比以及相关性能,因此为了保证仪表放大器中4个电阻的严格匹配<sup>[12]</sup>。设计采用了德州仪器公司的INA826,该芯片为典型的三仪表运算放大器,如图5所示,4个匹配电阻直接封装在芯片内部,在很大程度上避免了温度、寄生电容、寄生电阻等环境因素对这4个电阻的直接影响,保证了该仪表放大器的正常工作。

该运放的共模抑制比保持在  $10^4$  dB(在 Gain=10 时), 噪声在  $18 \text{ nV}/\sqrt{\text{Hz}}$ , 增益带宽积为 1 MHz, 拥有极其出色的共模抑制能力, 以及极低的噪声, 值得一提的是, 在该仪表运放的输入端集成了一个射频干扰滤波器 (radio-frequency interference filter)。

图 5 INA826 硬件结构

Fig. 5 INA826 hardware structure

frequency interference, RFI), 其截止频率  $f_c = 20$  MHz, 将强有力地削减带外的高频噪声, 进一步提高了工作性能。

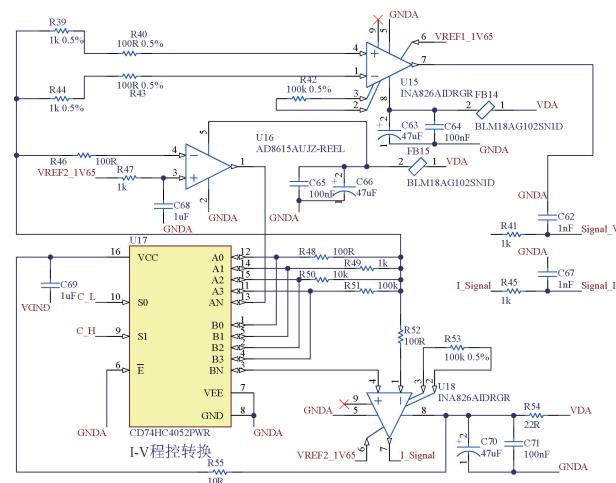

#### 4) I-V 转换电路模块设计

在本设计中,需要得知流经待测阻抗的电流,然而电流无法直接进行测量,所以引入了电流电压转换电路<sup>[13]</sup>(current-to-voltage,I-V),利用跨阻将电流转换为压差,然后经过仪表运放进行差模运算,得出压差,进而求出流经待测阻抗的电流。根据相关理论完成了相关原理图设计,如图6所示。

图 6 I-V 转换电路原理图设计

Fig. 6 I-V conversion circuit schematic design

### 5) 抗混叠滤波器模块设计

在本设计中同时使用了 AD 转换器与 DA 转换器。针对 DA 转换器而言, 目标是使最终输出波形的谐波分量达到要求。而对于 AD 转换器而言, 目标是避免通频带混叠入高频分量, 从而避免对采样结果产生影响。为了同时兼顾设计的便捷性与系统的稳定性, 设计采用最简单的阻容(resistance to capacitance, RC)滤波器进行抗混叠滤波器<sup>[14]</sup>的设计。经过实际测试该设计满足抗混叠滤波器的

基本设计要求。

两个抗混叠滤波器的区别在于截止频率。数模转换器的抗混叠滤波器采用的是  $R=5.1\text{ k}\Omega, C=220\text{ pF}$  的配比, 其截止频率为  $141.8\text{ kHz}$ 。模数转换器的抗混叠滤波器采用的是  $R=1\text{ k}\Omega, C=1\text{ nF}$  的配比, 其截止频率为  $159.1\text{ kHz}$ 。经过实际测试, 所设计的抗混叠滤波器达到了预期目标。

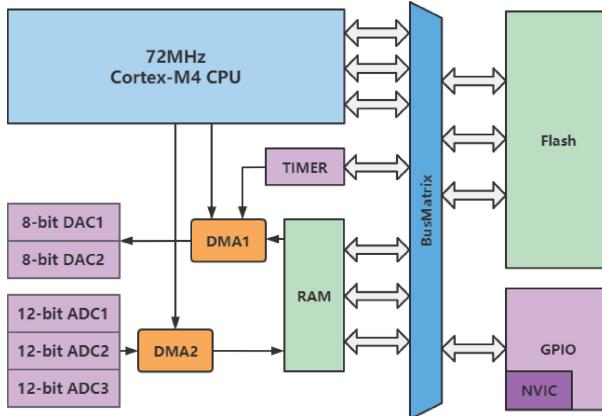

### 3 程序及算法设计

程序设计需要完成的功能有: 完成双路正交数据流计算与双通道数模转换器驱动、模数转换器驱动、数据采集与处理、屏幕驱动、数据存储与显示。因此在设计中共调用了以下几个外设: ADC、DAC、NVIC (nested vectored interrupt controller, 中断向量控制器)、DMA (direct memory access, 直接内存访问) 通道、IO(in out, 输入输出) 接口, 如图 7 所示。

图 7 微控制器外设控制结构

Fig. 7 Microcontroller peripheral control structure

程序与算法部分的具体的数据流为, 微控制器将准备好的正交数据字段送入双通道数模转换器, 在经过外部模拟电路后, 微控制器再次控制模数转换器采集经过硬件电路处理后的信号, 将其转变为数字信号。之后将采集来的信号送入数字滤波器, 对数字信号进行处理, 并在微控制器内进行计算, 并最终将计算结果传送至屏幕进行展示。

#### 3.1 激励信号产生

本系统所使用的是正交正弦激励源, 是由微控制器内置的双通道数模转换器产生。因此需要生成两路数模转换器所需的正弦数据流。本设计 DAC 数据刷新速率为  $3.5\text{ Msps}$ 。

由于是从实际的连续的正弦波到离散的若干个点, 并且数模转换器采用的为 8 bit 分辨率, 输出电压从  $0\sim V_{REF+}$ , 因此驱动数模转换器的离散数据是从  $0x00\sim 0xFF$  中间的任意确定值, 因此需要计算出合适的数字与电压的映射关系<sup>[15]</sup>。

公式推导如下:

$$y(x) = V_s \sin(\Omega n) + \frac{V_{REF+}}{2} \quad (1)$$

$$2V_s < V_{REF+} \quad (2)$$

其中,  $y(x)$  为原始正弦信号,  $V_s$  为信号幅值,  $\Omega$  为信号数字频率,  $n$  为采样点计数,  $V_{REF+}$  为参考电压。

引入数模转换器刷新频率作为变量, 则:

$$y(x) = V_s \sin(2\pi \frac{f_s}{f_c} n) + \frac{V_{REF+}}{2} \quad (3)$$

其中,  $f_s$  为模拟频率,  $f_c$  为数模转换器刷新频率。

通过实际的测试, 发现当一个周期的点数多于 32 个时, 所推出的波形在经过后级二阶无源滤波后的波形谐波分量才可以满足测量需求。

因此两者的关系为:

$$f_c > 32f_s \Rightarrow f_s < \frac{1}{32}f_c \quad (4)$$

同时为了保证产生的波形满足至少一个完整周期, 则:

$$\frac{f_s}{f_c} n_s \geq 1 \Rightarrow \frac{f_c}{n_s} \leq f_s \quad (5)$$

其中,  $n_s$  为总点数。

综合式(4)和式(5)可得:

$$\frac{f_c}{n_s} \leq f_s < \frac{1}{32}f_c \quad (6)$$

经过电压量化后得:

$$y_{sineDigital}(n) = \frac{V_s}{V_{REF+}}(0xFF + 1) \sin\left(2\pi \frac{f_s}{f_c} n\right) + \frac{(0xFF + 1)}{2} \quad (7)$$

其中,  $y_{sineDigital}(n)$  为正弦波的量化输出电压。

同理可知:

$$y_{cosineDigital}(n) = \frac{V_s}{V_{REF+}}(0xFF + 1) \cos\left(2\pi \frac{f_s}{f_c} n\right) + \frac{(0xFF + 1)}{2} \quad (8)$$

其中,  $y_{cosineDigital}(n)$  为余弦波的量化输出电压。

经过以上的线性转换后, 数字输入会转换为  $0\sim V_{REF+}$  之间的正弦/余弦波形, 幅度为  $V_s$ , 直流偏置为  $V_{REF+}/2$ , 信号频率为  $f_s$ 。

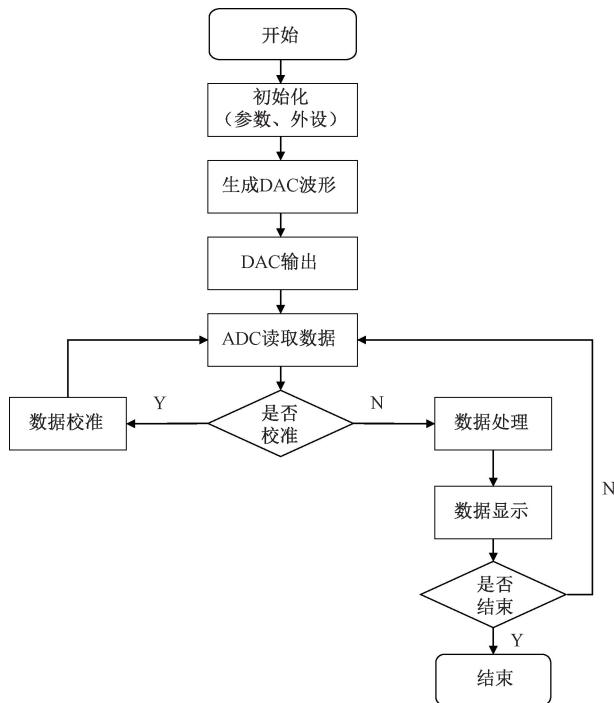

#### 3.2 整体流程程序设计

系统整体程序设计其主要流程如图 8 所示, 主要包括初始化相关外设及参数, DAC 生成两路用于鉴相的正交波形, ADC 对数据进行实时采集并由单片机进行处理后进行结果显示。

### 4 实物系统测试验证

本章节主要依据前述章节的设计思路完成相应的实物设计, 并对所形成的实物进行系统功能测试, 确保设计误差满足要求。

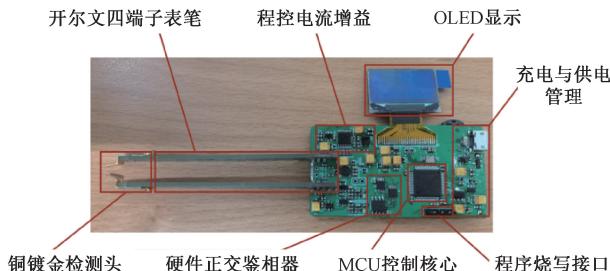

#### 4.1 实物展示

经过板级设计、元器件焊接、程序设计固化等步骤, 最后形成的实物设计如图 9 所示。

图 8 程序流程图

Fig. 8 Program flow chart

图 9 整机实物图

Fig. 9 Overall physical picture

#### 4.2 系统测试

系统测试部分主要分为关键模块测试与整机实物测试。对系统生成多频率下的两路激励信号的频率准确性进行测试,确保鉴相系统输入准确。对正交鉴相模块进行相位误差测试,确保矢量法计算阻抗的准确性。最终对整机实物进行测试,分别测量不同值的电阻及电容,并于标准电桥测量值做比对,了解系统最终性能,从而验证设计是否达到预期设计目标。其中实验所涉及的测试仪器如表 1 所示。

上述表 1 中的设备在实验使用前均需要进行校准。校准的主要方式为用户端自校准。首先开机预热 30 min 确保仪器稳定。然后断开仪器的输入探头,运行仪器控制面板中的自校准功能,经过 3~5 min 的自校准程序运行实现内部自校准。最后进行探头补偿,其中示波器通过探头连接其面板上自带的测试方波进行探头手动调整校准;数字

表 1 测试仪器信息

Table 1 Test instrument information

| 仪器设备          | 型号                | 相关信息             |

|---------------|-------------------|------------------|

| 示波器           | Tektronix DPO3054 | 500 MHz 2.5 GS/s |

| 数字万用表         | Tektronix DMM4020 | 五位半台式万用表         |

| 信号源           | RIGOL DG4202      | 任意信号发生源          |

| 专用鉴相仪         | Tektronix FCA3100 | 测量误差为±0.005°     |

| LCR 电桥<br>测试仪 | GWINSTEK LCR-829  | 高精度电桥            |

万用表通过连接探头后,对电压基准进行测量从而进行零点偏置调整;信号源则将输出端与校准好的示波器进行连接,通过调整信号源的输出,观察示波器的测试结果从而判断校准结果;鉴相仪需要进行输入阻抗校准,在连接检测探头后,分别使用标准终端负载( $50 \Omega/1 M\Omega$ )连接对应通道,并在通道设置中选择相应的阻抗进行阻抗校准;LCR 电桥测试仪的补偿较为复杂,由于其仪器易受到接触电阻、电感、并联电容等杂散成分影响,通常通过开路清零与短路清零的方式来消除测量夹具或测试端线路的杂散成分,从而保证测量的准确性。其中开路校准可以对高阻抗测量进行补偿,而短路校准适用于低阻抗的测量。

由于环境温度会影响阻容器件温漂、运放偏置电压、测试仪器指标等参数,通过查阅系统所使用的各类阻容、芯片的数据手册及测试仪器的说明手册中的标准测试温度为 25°C。为确保系统工作在标准状态,通过将实验室的恒温空调设置为 25°C,并间隔 10 min 进行一次实验环境温度测量,确保环境温度稳定在 25°C,误差不超过±0.5°C。

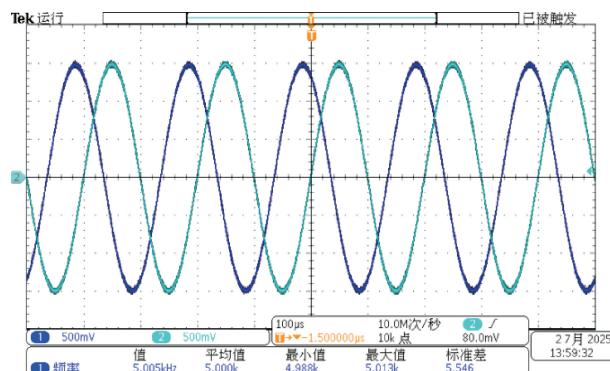

#### 1) 正交与频率测试

波形图抓取使用的是 Tektronix 公司的 DPO3054 示波器。抓取的 5 kHz 双路正交信号如图 10 所示。

图 10 5 kHz 双路正交信号

Fig. 10 5 kHz dual-channel quadrature signal

正交信号的相位以及频率测量共测试了 5、10、20、50、100 kHz 五个频点。频率以及相位测量结果如表 2 与表 3 所示。

#### 2) 正交鉴相测试

由于该部分直接测试存在不便,因此使用了正交鉴相

表 2 信号频率数据统计

Table 2 Signal frequency data statistics kHz

| 预设频率 | 仪器测量频率   | 相对误差     |

|------|----------|----------|

| 5    | 5.000 07 | 0.000 07 |

| 10   | 10.000 1 | 0.000 1  |

| 20   | 20.000 3 | 0.000 3  |

| 50   | 50.000 8 | 0.000 8  |

| 100  | 100.002  | 0.002    |

注:误差度数为两个结果的差值的绝对值,下同。

表 3 信号相位数据统计

Table 3 Signal phase data statistics (°)

| 预设频率/kHz | 仪器测量相位差 | 相对误差 |

|----------|---------|------|

| 5        | 90.15   | 0.15 |

| 10       | 89.38   | 0.62 |

| 20       | 89.28   | 0.72 |

| 50       | 88.20   | 1.8  |

| 100      | 86.83   | 3.17 |

先验模块进行测量。该模块上的比较器与多路选择器的型号与最终设计上所采用的器件型号保持一致。

鉴相频率选择了 1 kHz 与 10 kHz, 测试结果如表 4 与表 5 所示。

表 4 鉴相数据统计(1 kHz)

Table 4 Phase detection data statistics(1 kHz) (°)

| 仪器测量结果 | 实际测量结果 | 误差度数  |

|--------|--------|-------|

| 0°     | 0.857  | 0.857 |

| 10°    | 10.960 | 0.960 |

| 20°    | 20.687 | 0.687 |

| 30°    | 30.728 | 0.728 |

| 40°    | 40.197 | 0.197 |

表 5 鉴相数据统计(10 kHz)

Table 5 Phase detection data statistics(10 kHz) (°)

| 仪器测量结果 | 实际测量结果 | 误差度数  |

|--------|--------|-------|

| 0°     | 1.324  | 1.324 |

| 10°    | 11.542 | 1.542 |

| 20°    | 21.192 | 1.192 |

| 30°    | 30.710 | 0.710 |

| 40°    | 40.350 | 0.350 |

注:实际测量结果保留小数点后 3 位, 仪器测量误差为 ± 0.005°。

### 3) 整机测试

该部分针对电阻、电容的多种阻容值进行了测试。如表 6~9 所示, 表中所测试的器件的标称值为电阻本与电容本上标出的数值, 电桥值为采用 LCR 阻抗测量仪器测得

5 次数据的平均值。测量值为使用本文中设计系统完成的 5 次测量结果的平均值。

表 6 电阻测试 1

Table 6 Resistance test 1

| 标称值/<br>Ω | 电桥值<br>(平均)/Ω | 测量值<br>(平均)/Ω | 相对误差/<br>% |

|-----------|---------------|---------------|------------|

| 2         | 1.976 0       | 2.124 2       | 0.075      |

| 5.1       | 5.223 0       | 5.471 6       | 0.045 4    |

| 10        | 9.998 6       | 10.257        | 0.025 8    |

| 56        | 56.168        | 57.214        | 0.018 6    |

| 100       | 99.783        | 101.86        | 0.020 8    |

| 150       | 149.94        | 152.45        | 0.016 7    |

| 200       | 199.23        | 202.32        | 0.015 5    |

表 7 电阻测试 2

Table 7 Resistance test 2

| 标称值/<br>Ω | 电桥值<br>(平均)/Ω | 测量值<br>(平均)/Ω | 相对误差/<br>% |

|-----------|---------------|---------------|------------|

| 430       | 427.80        | 445.90        | 0.042 3    |

| 1 k       | 998.50        | 1 059.2       | 0.060 7    |

| 20 k      | 19.92 k       | 19.90 k       | 0.000 9    |

| 49.9 k    | 49.55 k       | 49.45 k       | 0.002 0    |

| 100 k     | 108.6 k       | 110.3 k       | 0.015 4    |

| 510 k     | 496.4 k       | 520.0 k       | 0.047 5    |

| 1 M       | 960.0 k       | 1 025.0 k     | 0.067 3    |

表 8 电容测试 1

Table 8 Capacitance test 1

| 标称值/<br>pF | 电桥值<br>(平均)/pF | 测量值<br>(平均)/pF | 相对误差/<br>% |

|------------|----------------|----------------|------------|

| 20         | 21.600 0       | 20.165 0       | 0.066 4    |

| 51         | 53.370 0       | 49.831 0       | 0.066 3    |

| 100        | 101.480        | 97.126 0       | 0.042 9    |

| 150        | 152.512        | 146.186        | 0.041 4    |

| 270        | 275.850        | 268.450        | 0.026 8    |

| 560        | 517.390        | 496.147        | 0.041 1    |

表 9 电容测试 2

Table 9 Capacitance test 2

| 标称值/<br>pF | 电桥值<br>(平均)/pF | 测量值<br>(平均)/pF | 相对误差/<br>% |

|------------|----------------|----------------|------------|

| 820        | 810.250 0      | 786.700 0      | 0.029 1    |

| 1 500      | 1 458.000      | 1 402.000      | 0.038 4    |

| 15 000     | 14 390.00      | 17 290.00      | 0.201 5    |

| 47 000     | 47 769.00      | 48 399.00      | 0.013 2    |

| 82 000     | 80 165.00      | 82 785.00      | 0.032 7    |

| 100 000    | 103 580.0      | 109 460.0      | 0.056 8    |

相对误差的计算方式为使用测量结果减去电桥测量结果,之后取差值的绝对值,并除以电桥值得出的结果。

对于系统测量速度方面,其中系统从开机到完成电阻、电容值测量并完成显示的时间,经过多次实际测量并取其平均时间约为4.5 s。事实上这4.5 s的时间主要消耗在系统开机后,激励模块与采集模块的稳定上。待系统从开机并完成初次测量后,后续进行的一系列测量基本实现“即测量即显示”,所消耗的时间与开机完成初次测量所消耗的时间相比基本可以忽略不计。

从表6~9可以看出,所设计的检测仪可以较好的识别并计算出其阻容值。对于电阻测量误差的均值为0.032 4%,对于电容测量误差的均值为0.054 7%,其测量误差最小可以达到0.000 9%,对于电容的测量精度略低于电阻的测量。对于电阻的测量范围为1~1 MΩ,对于电容的测量为20 pF~100 nF。该实物系统的测量误差较小,可以满足日常阻容测试的精度需求。

## 5 结 论

精密的阻抗测量是电子系统设计中必不可少的关键性技术,本文以矢量法为基础,设计了一套完整的精密阻抗测量方案,对信号激励、正交鉴相、I-V转换、仪表放大等关键模块进行设计论证,结合程序设计算法,实现了一套准确度高、结构简单的实物设计方案。相比于传统的数字鉴相,该设计使用硬件正交鉴相器进行鉴相,极大的减轻了单片机内浮点运算压力;使用电子开关来代替传统的模拟乘法器作为正交鉴相器的核心,有效规避了模拟乘法器由于谐波失真与前级直流漂移问题所带来的精度损失;通过使用单片机产生正弦信号从而代替DDS模块,在节约成本的同时大幅度缩小了整体体积,同时相关芯片采用小封装,并在布线时力争紧凑,最终使得设计高度集成化,体积小巧,便于携带。经过实际测试验证,实验结果表明:在1~1 MΩ的电阻测试范围,其测量误差的均值为0.032 4%;在20 pF~100 nF的电容测试范围,其测量误差的均值为0.054 7%。本文的阻抗测量设计方案在保证精确性的前提下,其便携性、低成本方面均做了相应平衡,为电阻、电容测量提供了一种新思路,但对于电感测量还未涉及,在后续的研究中会电感测量做系统性的分析与测试并将其集成在系统中,实现“电感-电容-电阻”的全阻抗测量覆盖。

## 参考文献

- [1] SPEAKMAN A, HITCHCOCK K, ROMANTIC E, et al. Least significant change with repeat bioelectrical impedance analysis measurements in children with metabolic dysfunction-associated steatotic liver disease: A descriptive cohort study[J]. Journal of Parenteral and Enteral Nutrition, 2024, 49(2): 200-206.

- [2] 金恩淑,胡晓晨,张双双,等.基于测量阻抗等值面积的柔性直流配电线单端量保护方案[J].电网与清洁能源,2025,41(2):51-59.

- [3] JIN EN SH, HU X CH, ZHANG SH SH, et al. A single-ended protection scheme for flexible DC distribution lines based on measuring impedance equivalent area[J]. Power System and Clean Energy, 2025,41(2):51-59.

- [4] 于思琦,牟宪民,陈希有,等.基于多点阻抗的锂离子电池健康状态在线快速诊断方法[J].电工电能新技术,2025,44(2):116-128.

- [5] YU S Q, MU X M, CHEN X Y, et al. An online rapid diagnosis method for the health status of lithium batteries based on multipoint impedance[J]. Advanced Technology of Electrical Engineering and Energy, 2025,44(2):116-128.

- [6] 马思远,刘旭,焦御坤,等.生物阻抗检测芯片设计综述[J].集成电路与嵌入式系统,2025,25(2):64-74.

- [7] MA S Y, LIU X, JIAO Y K, et al. Review of biological impedance detection chip design[J]. Integrated Circuits and Embedded Systems, 2025,25(2):64-74.

- [8] KARIME A, BATTISTEL A, MÖLLER K. Vector network analyzer (VNA) measurements for electrical impedance tomography [J]. Current Directions in Biomedical Engineering, 2024, 10(4): 360-364.

- [9] 梁贵谦,张旭,李雨微,等.嵌入式RLC参数测量系统的设计[J].声学技术,2022,46(7):115-118.

- [10] LIANG G Q, ZHANG X, LI Y W, et al. Design of embedded RLC parameter measurement system[J]. Audio Engineering, 2022, 46(7): 115-118.

- [11] 冯建,石雷兵,周碧红,等.阻抗电桥法测量交流分流器时间常数[J].计量学报,2025(1):75-79.

- [12] FENG J, SHI L B, ZHOU B H, et al. Time constant measurement of AC shunt by impedance bridge[J]. Acta Metrologica Sinica, 2025(1):75-79.

- [13] WANG X F, SU J J, YANG J H, et al. Modified homodyne laser interferometer based on phase modulation for simultaneously measuring displacement and angle [J]. Applied Optics, 2021, 60 (16): 4647-4653.

- [14] 王举光.基于相敏检波的太阳绝对辐射测量技术研究[D].长春:中国科学院大学:中国科学院长春光学精密机械与物理研究所,2024.

- [15] WANG J G. Research on solar absolute radiation measurement technology based on phase sensitive detection [D]. Changchun: Changchun Institute of Optics, Fine Mechanics and Physics, Chinese Academy of Sciences, 2024.

- [16] NI ZH P, XIA J, ZHOU X Y, et al. Design of a wideband symmetric large back-off range Doherty

- power amplifier based on impedance and phase hybrid optimization[J]. Frontiers of Information Technology & Electronic Engineering, 2024, 26(1):1-11.

- [11] 王宇, 郭柴旺, 王俊虹, 等.  $\Phi$ -OTDR 系统非对称光纤耦合器相位解调方法研究[J]. 电子测量与仪器学报, 2023, 37(1):149-156.

WANG Y, GUO CH W, WANG J H, et al. Study on phase demodulation method of asymmetric optical fiber coupler in  $\Phi$ -OTDR system[J]. Journal of Electronic Measurement and Instrumentation, 2023, 37 (1): 149-156.

- [12] 宿芷若, 陈雪峰, 李志远. 传感器模拟前端低噪声可变增益放大器的设计[J]. 黑龙江大学自然科学学报, 2024, 41(6):731-742.

SU ZH R, CHEN X F, LI ZH Y. Design of a low-noise variable gain amplifier for the analog front-ended of the sensor[J]. Journal of Natural Science of Heilongjiang University, 2024, 41(6):731-742.

- [13] 王彦凯, 赵宏强, 孙婧. 一种升流型电流/电压转换电路的建模与分析[J]. 舰船电子工程, 2023, 43(11):202-206.

WANG Y K, ZHAO H Q, SUN J. Modeling and analysis of an up-current current/voltage conversion circuit[J]. Ship Electronic Engineering, 2023, 43(11): 202-206.

- [14] 武媛媛, 徐克欣, 陈丹, 等. 一种 ADC 前端无源差分抗混叠滤波器设计[J]. 电子与封装, 2023, 23(4):46-50.

WU Y Y, XU K X, CHEN D, et al. Design of ADC front-ended passive differential anti-aliasing filter[J]. Electronics & Packaging, 2023, 23(4):46-50.

- [15] ZHAO Y J, KATOH K, KUWANA A, et al. Revisit to histogram method for ADC linearity test: Examination of input signal and ratio of input and sampling frequencies[J]. Journal of Electronic Testing, 2022, 38(1):1-18.

### 作者简介

李松凯(通信作者), 硕士, 中级工程师, 主要研究方向为嵌入式系统设计、保密管理与技术等。

E-mail: lisongkai@cse.neu.edu.cn

关贝贝, 本科, 主要研究方向为信号采集与处理。

E-mail: 2226739647@qq.com

刘金海, 博士, 教授, 主要研究方向为工业智能、智能机器人、电气系统监测与控制、数据驱动故障诊断理论与技术、电磁无损检测技术等。

E-mail: liujinbai@mail.neu.edu.cn