# Qt 协调国产 FPGA 的逻辑层动态调度图像系统<sup>\*</sup>

谢家兴<sup>1,2</sup> 李东峻<sup>1,2</sup> 周欣红<sup>1,2</sup> 莫汉东<sup>1,2</sup> 罗洋<sup>1,2</sup> 刘洪山<sup>1,2</sup>

(1. 华南农业大学电子工程学院 广州 510642; 2. 华南农业大学人工智能学院 广州 510642)

**摘要:** 针对图像处理系统灵活性不足与智能化水平待提升的问题,本研究致力于克服国产 FPGA 动态重构领域存在的技术瓶颈,提出了一个逻辑层动态调度图像系统。该系统基于上海安路科技公司 PH1A90 FPGA 芯片与 Qt 框架进行开发,基于逻辑层动态调度原理通过智能上位机控制模块可实现近似于 DPR 的全链路动态调度行为。实验结果表明,本研究实现了 Qt 上位机与 PH1A90 FPGA 的软硬件协同,完成了四接口异构输入、双传感器协同成像、算法处理链配置与 22 种 ISP 动态处理算法,并通过 HDMI 输出 1080P@60 fps 视频流,验证了接口、流程以及算法上的逻辑层动态调度能力与国产芯片的工业级可靠性,推动我国智能安防、工业检测等领域的自主可控进程。

**关键词:** 现场可编程门阵列;Qt 框架;图像处理技术;逻辑层动态调度;软硬件协同;人机交互

中图分类号: TN79; TN91 文献标识码: A 国家标准学科分类代码: 510.4

## Qt-coordinated LDS image processing system for domestic FPGA

Xie Jiaxing<sup>1,2</sup> Li Dongjun<sup>1,2</sup> Zhou Xinhong<sup>1,2</sup> Mo Handong<sup>1,2</sup> Luo Yang<sup>1,2</sup> Liu Hongshan<sup>1,2</sup>

(1. School of Electronic Engineering, South China Agricultural University, Guangzhou 510642, China;

2. School of Artificial Intelligence, South China Agricultural University, Guangzhou 510642, China)

**Abstract:** In response to the limitations in flexibility and the insufficient level of intelligence in existing image processing systems, this study addresses key technical challenges in the dynamic reconfiguration domain of domestic FPGAs by proposing a logic-level dynamically scheduled image processing system. The system is developed based on the PH1A90 FPGA chip from Shanghai Anlogic Technology Co., Ltd., integrated with a Qt-based host platform. By employing logic-level dynamic scheduling principles, the system achieves near-Dynamic Partial Reconfiguration (DPR)-level full-link dynamic scheduling under the control of an intelligent host module. Experimental validation demonstrates successful hardware-software co-design between the Qt host and the PH1A90 FPGA, achieving four-interface heterogeneous data acquisition, dual-sensor collaborative imaging, dynamic configuration of algorithmic processing chains, and real-time execution of twenty-two dynamic ISP algorithms. The system outputs 1080P@60 fps video streams via HDMI, validating its dynamic scheduling capabilities across interfaces, workflows, and algorithms at the logic level. Furthermore, the results confirm the industrial-grade reliability of domestic FPGA solutions, contributing to the advancement of independent and controllable technologies in fields such as intelligent security and industrial inspection.

**Keywords:** field programmable gate array; Qt framework; image processing technology; logic-level dynamic scheduling; hardware-software co-design; human-computer interaction

## 0 引言

实时视频图像处理技术要义在于对原图像进行图像信号处理(image signal processing, ISP)从而得到更高质量的视觉效果。随着智能安防、工业检测等领域对实时视频处理需求的爆发式增长,系统动态调度能力与多模态协同处

理效率已成为制约技术落地的核心瓶颈。尽管基于 FPGA 的加速架构已逐步替代传统 DSP/GPU 方案(如周倩等<sup>[1]</sup>基于 FPGA 提出了一种自适应平衡算法,李先友等<sup>[2]</sup>基于固定流水线架构设计了一种基于 Lattice FPGA 的实时图像采集与处理系统),但现有研究仍存在两大短板:其一,进口 FPGA 生态依赖性强,国产 FPGA 存在 DPR 支持不

足的生态痛点,安路科技 PH1A 系列 75% 的型号完全缺乏动态部分重配置(dynamic partial reconfiguration, DPR)支持,剩余型号仅提供实验性接口。这与主流商用 FPGA(如 Xilinx Artix-7 系列 100% 支持 DPR)形成鲜明对比,凸显国产芯片在动态重构领域的技术代差,Kechiche 等<sup>[3]</sup>在 Xilinx Zynq 基于 DPR 完成实时多视频系统的节能架构,郭彪等<sup>[4]</sup>基于 SDR 系统的软件通信体系架构,设计一种支持 FPGA 的 DPR 软件架构,而国产 FPGA 基本无法支持 DPR 方案;其二,图像处理领域研究缺乏全局协同性,田杰等<sup>[5]</sup>的高带宽设计仅解决吞吐量问题,研究缺乏对多传感器数据流、算法动态加载及资源约束的全局协同;其三,软硬件协同的动态调度大多局限于单一维度,赵子豪等<sup>[6]</sup>于 2022 年通过上位机对 FPGA 硬件模块参数的设置与对外设的命令传输,提出了通过上位机对图像处理系统动态调度方案,但由于上位机仅局限于算法层的调度,存在控制与硬件加速实时交互能力薄弱的问题。

鉴于上述情况,本文基于国产 FPGA 提出了一个逻辑层动态调度(logic-level dynamic scheduling, LDS)的智能图像处理系统。本文主要贡献如下:对本文提出的近似于 DPR 的 LDS 方案在国产 28 nm 级工艺的 PH1A90 FPGA 芯片完成验证,弥补在动态调度架构领域的国产技术代差;此外,基于 LDS 实现了接口、流程以及算法三维度动态调度,解决了传统方案中因固定架构导致的场景适应性不足以及调度层级单一的问题;最后,利用 Qt 的跨平台特性与模块化设计能力开发智能控制界面,实现了任意接口数据调度处理、算法处理链配置以及算法参数动态配置,将传统 FPGA 开发中需硬件重构的功能转化为软件可编程任务,显著缩短开发周期。

## 1 系统设计

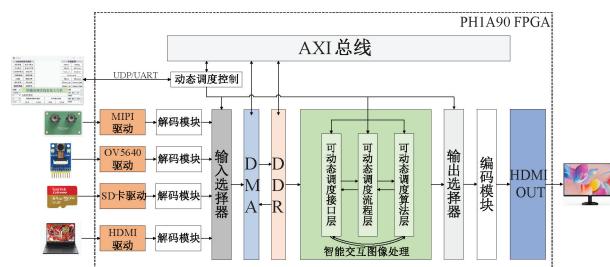

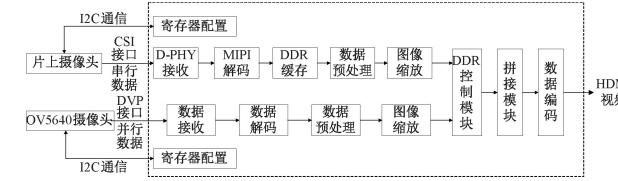

本智能图像处理系统采用 Anlogic PH1A90 FPGA 芯片构建并行处理四流水线任务,包括实时采集、数据流存取、智能交互图像处理以及驱动输出,并搭载众多外设,从接口层、流程层、算法层三维实现动态调度的智能图像处理功能,总体逻辑如图 1 所示。

图 1 系统总体逻辑功能设计图

Fig. 1 System overall logic function design diagram

实时采集任务中,本系统支持片上摄像头与 OV5640 摄像头双路摄像源、HDMI (high definition multimedia

interface) 驱动以及 SD 卡 (secure digital card) 驱动共 4 种输入源,其中片上摄像头与 OV5640 摄像头分别通过 MIPI CSI-2 (mobile industry processor interface camera serial interface 2) 的高速串行接口与 DVP (digital video port) 的并行接口向系统内部输入图像数据。数据存取任务中,AXI (advanced extensible interface) 总线下搭载的 DMA (direct memory access) 控制器在不占用 CPU 资源的情况下负责直接将解码处理完毕的数据传输到异步 DDR 中,按照指定的地址存储起来,等待后续高速实时处理。智能交互图像处理任务中,本系统通过搭载支持 UART (universal asynchronous receiver/transmitter) @ 115 200 bps 协议与 UDP (user datagram protocol) @ 1 000 Mbps 协议<sup>[7]</sup> 通信的 Qt 上位机,支持对四输入接口的数据流进行接口动态调度、对双模异构处理模式进行流程动态调度以及对 22 种硬件加速 ISP 算法进行算法动态调度。驱动输出任务中,本系统将处理完毕的数据流根据行场同步信号进行先进先出栈(first in first out, FIFO) 一级缓存后,满足输出接口时序匹配性,最后将数据流进行编码并通过 HDMI 输出。

## 2 逻辑层动态调度的图像处理任务实现

本研究中的智能交互图像处理任务基于 LDS 特性,将图像处理任务剖析为接口、流程、算法 3 个维度,Qt 上位机作为控制器实现三维度的调度行为,满足多场景下的应用需求。

### 2.1 逻辑层动态调度的原理

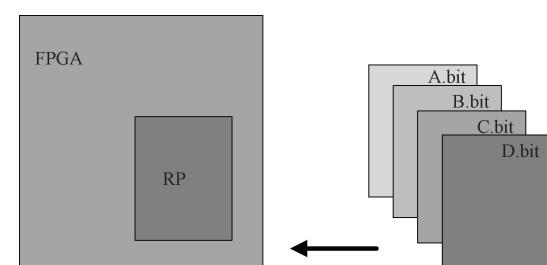

动态调度是一种根据实时系统状态、任务需求及环境变化的优化机制,其基础是系统状态的持续监控与反馈。传统动态调度(即 DPR)为物理层上动态调度,在 FPGA 开辟可重构分区(reconfigurable partition, RP)通过重写配置存储器改变物理电路结构,需要如图 2 所示可重构分区与部分重配置支持<sup>[8]</sup>,实现物理资源动态分配。

图 2 DPR 实现

Fig. 2 Implementation of DPR

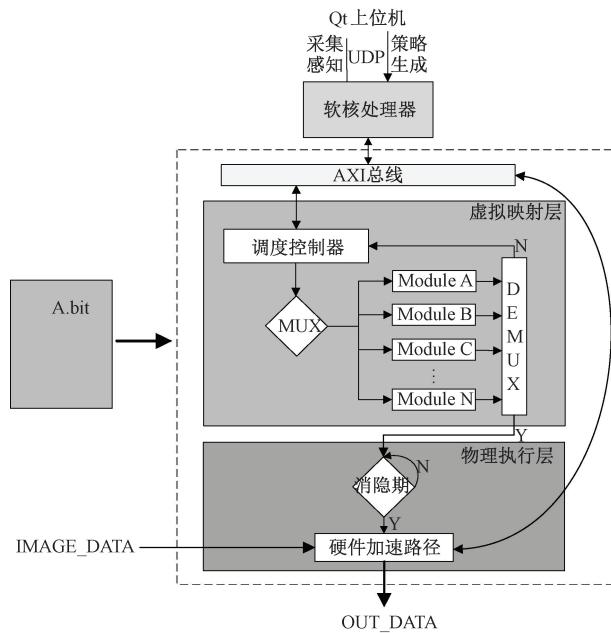

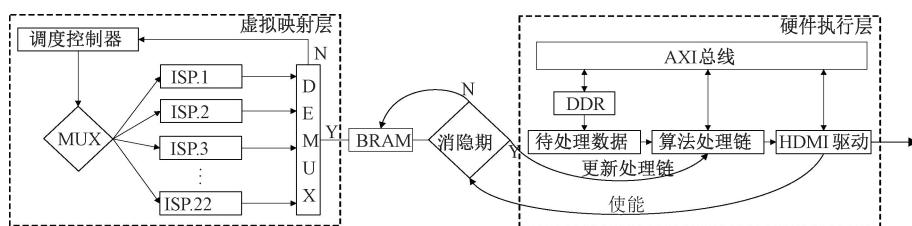

上文已论述 DPR 在国产 FPGA 的局限性与不易移植性,为了突破国产难以实现动态调度这一瓶颈,于是本研究提出一种如图 3 所示的 LDS 的动态调度方案。

LDS 方案仅需在单一比特流约束下,通过硬件资源分时复用与参数动态注入,将物理硬件资源抽象为虚拟资源池实现<sup>[9]</sup>。Qt 上位机充当决策作用,检测系统情况与用户

图 3 逻辑层动态调度实现

Fig. 3 Implementation of logic-level dynamic scheduling

指令生成调度决策, 传输至 AXI 总线下的调度控制器, 采用 MUX-DEMUX 结构完成对各模块的动态调度, 通过消隐期判断完成硬件加速路径的改变, 实现近似 DPR 的调度效果。

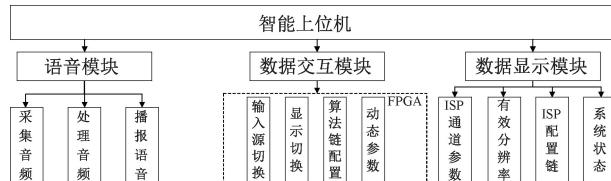

## 2.2 Qt 上位机实现

本上位机基于 Qt Creator 软件开发环境进行开发, 文献[10]中设计了基于串口通信的上位机, 完成姿态、位置等配置。本研究在此基础上完成以太网 UDP 通信, 并结合 LU-ASR01 语音芯片实现丰富的语音功能, 实现了实时性更强、人机交互性更高的特点。上位机整体框架如图 4 所示分为语音模块<sup>[11]</sup>、数据交互模块和数据显示模块, 支持 UDP@1 000 Mbps 与 UART@115 200 bps 双通道协议。UDP 通信主要用于与 FPGA 板卡数据互连, UART 通信主要用于与上位机的语音模块互连。语音模块采用 LU-ASR01 高精度语音识别芯片作为硬件支撑, 通过扩展子卡实现硬件级集成。上位机完成 32 条预设指令的按键/语音精准识别, 通过 UDP 数据包将控制指令传输至 FPGA, UI 界面显示操作结果, 完成软硬件协同。

图 4 上位机整体框架图

Fig. 4 Host computer overall framework diagram

设计完成的上位机 UI 界面如具备分区特性, 界面中心为反馈区, 用于反馈系统状态; 左侧为 ISP 算法选择区,

用于下文所述的可配置算法链模式; 界面右侧界面为算法参数配置区; 下方为模式选择区, 可以进行串口、以太网通信的参数设置, 各接口数据流动态调度等。

## 2.3 接口上动态调度实现

文献[3]所述 DPR 可通过切换比特流的重构方式实现多接口数据流调度, 而国产 FPGA 不支持 DPR 仅能完成单一或多接口并行输入, 本研究基于 LDS 搭载了四异构输入接口(片上 MIPI 摄像头、OV5640 摄像头、HDMI、SD 卡), 接口间支持硬件资源分时复用, 每个接口相当于一个 Module, MUX 完成任意接口数据流选择后进行后续图像处理任务, 并通过 HDMI 实现数据流输出。支持单一数据流输出的同时, 本研究实现双传感器协同成像, 此时若只有单一数据流 DEMUX 将会判断为 N, 返回调度控制器使能另一数据流, 同时向物理执行层输送双路数据, 从而实现如图 5 所示的双路拼接。

1) OV5640 摄像头(DVP 接口)2 592×1944@15 fps 高分辨率静态成像;

2) 片上摄像头(4-lane MIPI CSI-2 接口)1 280×720@60 fps 高速动态捕获。

图 5 双传感器协同成像设计

Fig. 5 Design of dual-sensor collaborative imaging

在工业质检等典型场景中, 两传感器形成动态-静态协同感知范式: OV5640 通过自动对焦(AF)获取微米级表面纹理特征, MIPI 模组则以低延迟追踪运动缺陷(如传送带上的工件形变), 双模数据经时空对齐后输入决策引擎, 能够实现检测准确率提升。

为解决多源分辨率归一化问题, 本系统采用双线性插值算法<sup>[12]</sup>, 公式如下:

$$f(P) = \frac{1}{(x_2 - x_1)(y_2 - y_1)} [x_2 - x \quad x - x_1] \begin{bmatrix} f(Q_{11}) & f(Q_{12}) \\ f(Q_{21}) & f(Q_{22}) \end{bmatrix} \begin{bmatrix} y_2 - y \\ y - y_1 \end{bmatrix} \quad (1)$$

其中,  $f(P)$  是待插值点的像素值,  $x_2 - x$  和  $x - x_1$  是水平方向的加权系数,  $y_2 - y$  和  $y - y_1$  是竖直方向的加权系数。对算法进行改进重建, 其像素重建公式为:

$$\sum P(x, y) = \frac{\sum_{i=0}^1 \sum_{j=0}^1 \omega_{ij} \cdot Q(x_i, y_j)}{\sum \omega_{ij}} \quad (2)$$

其中,  $\omega_{ij}$  为邻域像素权重系数, 基于 LDS 特性, 通过 Qt 上位机控制可配置寄存器, 配置缩放因子在  $0 \times 0 \sim 1 920 \times 1 080$  分辨率区间连续可调, 实现  $0.25x \sim 4x$  无极

缩放效果(步长  $0.01x$ ),上位机 UI 界面将实时采集并显示当前分辨率与帧率,以便用户做出下一步决策。

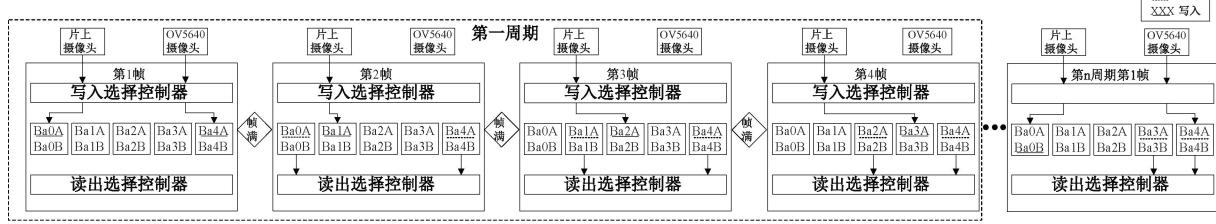

异构视频流拼接实现中,片上摄像头数据流经缩放模块生成  $960 \times 540 @ 60$  fps 子流,而 OV5640 摄像头数据流生成  $960 \times 540 @ 15$  fps 子流。为了解决帧率匹配问题,本研究通过如图 6 所示 AXI4-Stream 交叉开关分别将双路数据流写入 DDR Bank0-Bank3/Bank4(图 6 中 Bank 简写为 Ba),对每帧 OV5640 数据分配 4 个帧缓冲区,实现与片上摄像头数据帧率匹配。解码后的第一帧数据首先写入

Bank0A 与 Bank4A,当写满一帧时,进行移位操作,向 Bank1A 写入片上摄像头的第二帧数据流,以此类推完成一次奇周期(4 帧)的写入操作。进入偶周期,采用乒乓策略<sup>[13]</sup>,写入 Bank B 区间,并异步完成存储在 A 区间的数据流读出。最终同样采用乒乓策略通过 HDMI 驱动模块,在每帧消隐期同步在 DDR 中获取双路数据,按式(3)完成空间拼接。

$$I_{\text{out}}(x, y) = \begin{cases} I_{\text{MIPi}}(x, y), & x \in (0, 959) \\ I_{\text{OV5640}}(x, y), & x \in (960, 1919) \end{cases} \quad (3)$$

图 6 DDR 帧率匹配操作原理示意图

Fig. 6 Schematic diagram of DDR frame rate matching operation principle

## 2.4 流程上动态调度实现

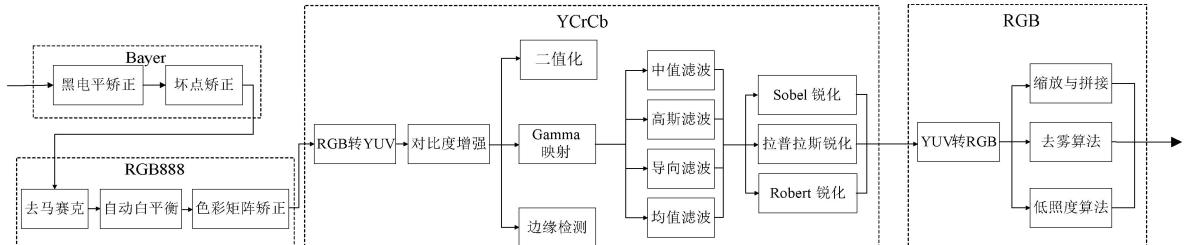

本研究在 ISP 处理流程上基于 LDS 构建双处理模式,通过上位机“图像处理模式切换”控件实现 ISP 全流程处理模式与可配置算法链模式的动态切换。

ISP 全流程处理模式是标准化的“刚性骨架”,按照设定的处理流程对原始数据流进行完整处理,处理流程如图 7 所示。处理期间,用户可以根据图像显示效果通过控件切换滤波算法以及锐化算法,达到更理想的处理效果。除此以外,本系统支持图像缩放、拼接、去雾等后续算法处理的操作。可配置算法链模式是定制化的“柔性扩展”,如图 8 所示系统支持多级算法动态叠加,用户可根据实际需求构建个性化处理链,具备算法自由组合、无需整体重构的

优势。首先在 AXI 总线中实例化最大数量的 ISP Module。然后模拟 DPR 重构电路特性在虚拟映射层构建 MUX-DEMUX 结构,实现 Module 的输入/输出端连接到任意 Module 或是处理输出端,从而构建个性化处理链,达到 DPR 下切换比特流的近似效果。最后,设计动态旁路机制,当模块未被选中时,数据直通,不消耗计算资源,待消隐区判断为 Y 时完成配置路径更新。本研究将文献[3]中 DPR 通过细粒度资源配置重构算法链硬件资源的方式转变在预设的硬件资源虚拟化分时复用的方式实现,通过信号切换和参数注入实现算法链动态调整,完成国产 FPGA 缺失 RP 的替代方案,且具备更强的实时性,无配置位翻转风险。

图 7 ISP 全流程处理模式流程图

Fig. 7 Flowchart of the ISP process processing mode

图 8 可配置算法链模式流程图

Fig. 8 Flowchart of configurable algorithm chain mode

## 2.5 算法上动态调度实现

在传统基于固定硬件逻辑的图像处理架构中,静态参数配置机制往往导致算法适应性受限,难以应对复杂多变的成像环境(如光照突变、传感器特性漂移等)。针对这一技术瓶颈,本研究基于 LDS 提出一种软硬件协同的动态参数优化方案,通过构建智能上位机与硬件处理单元的双向反馈通路,实现算法参数的在线优化。本文以色彩校正矩阵(color correction matrix, CCM)算法为研究对象,阐述该系统的实现机理与创新价值。

CCM 通过矩阵运算,将这些偏移矫正过来,恢复图像的真实色彩,从而最大还原人眼感知效果。以文献[14]中 CCM 算法实现机理为基础,即 CCM 表示为一个  $3 \times 3$  矩阵,该矩阵将输入 RGB 值  $(R_{in}, G_{in}, B_{in})$  纠正为输出 RGB 值  $(R_{out}, G_{out}, B_{out})$ ,公式如下:

$$\begin{bmatrix} R_{out} \\ G_{out} \\ B_{out} \end{bmatrix} = \begin{bmatrix} rr & gr & br \\ rg & gg & bg \\ rb & gb & bb \end{bmatrix} \begin{bmatrix} R_{in} \\ G_{in} \\ B_{in} \end{bmatrix} \quad (4)$$

其中,  $r_r, g_g, b_b$  为 RGB 三通道的饱和度;  $r_g, r_b$  为 R 通道的绿、蓝色比例;  $g_r, g_b$  为 G 通道的红、蓝色比例;  $b_r, b_g$  为 B 通道的红、绿色比例。

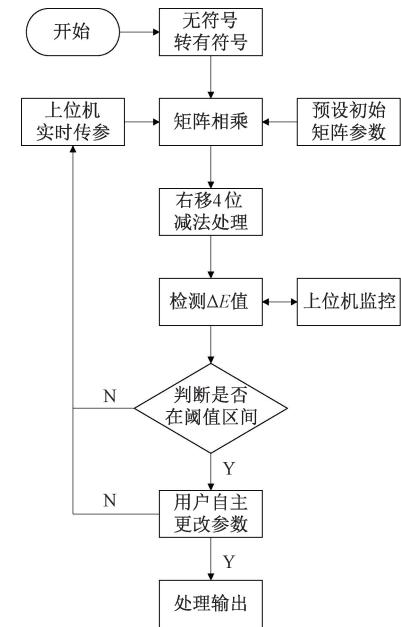

本研究针对传统 CCM 算法进行如图 9 所示的创新动态协同优化架构设计。首先,在图像处理通道中搭建文献[14]所述 CCM 算法的硬件加速模块,实现预定矩阵系数的处理效果。接着新增闭环反馈机制,上位机持续监控输出图像的色度统计特征(本研究选取  $\Delta E$  值<sup>[15]</sup>进行式(5)~(9)计算),构建基于人眼视觉特性<sup>[16]</sup>的动态评价体系。最终搭建动态参数接口,在 FPGA 设计矩阵系数影子寄存器组,支持上位机微秒级系数热更新。

$$\Delta E_{00} = \sqrt{\left(\frac{\Delta L'}{k_L S_L}\right)^2 + \left(\frac{\Delta C'}{k_C S_C}\right)^2 + \left(\frac{\Delta H'}{k_H S_H}\right)^2} + R_T \frac{\Delta C' \Delta H'}{S_C S_H} \quad (5)$$

$$S_L = 1 + \frac{0.015(\bar{L}' - 50)^2}{\sqrt{20 + (\bar{L}' - 50)^2}} \quad (6)$$

$$S_C = 1 + 0.045\bar{C}' \quad (7)$$

$$S_H = 1 + 0.015\bar{C}'T \quad (8)$$

$$R_T = -2\sin(2\Delta\theta) \sqrt{\frac{\bar{C}^{\prime 2}}{\bar{C}^{\prime 2} + 25^2}} \quad (9)$$

其中,式(5)基于 CIELAB 颜色空间,  $\Delta L', \Delta C', \Delta H'$  分别是给定颜色值间的亮度差、彩度差、色调差,  $k_L, k_C, k_H$  为参数化权重因子,  $S_L, S_C, S_H$  为式(6)~(8)所示关于三参数平均差值的权重函数,式(9)中  $R_T$  为旋转函数,  $\Delta E_{00}$  值越小越好,表明颜色准确性越高,用户自主改变 24 通道参数减少  $\Delta E_{00}$  值,进一步还原图像真实色彩。

## 3 实验分析与应用

为验证 LDS 在图像处理中的实际效果,本研究在

图 9 LDS 下动态 CCM 算法实现

Fig. 9 Implementation of the dynamic CCM algorithm under LDS

Anlogic PH1A90 FPGA 上搭建系统,通过 TD 软件与 Qt 上位机通过 UDP 协议完成软硬件协同。其中,片上 MIPI 模组摄像头、SD 卡及 HDMI 完成  $1280 \times 720 @ 60$  fps 数据流输入,OV5640 摄像头完成  $2592 \times 1944 @ 15$  fps 数据流输入,对任意通路采集的视频进行动态算法链处理,显示屏通过 HDMI 输出  $1080P @ 60$  fps 数据流,实验过程通过 Anlogic TD 软件 ChipWatcher 功能实时采集波形。

### 3.1 LDS 功能验证

对接口、流程、算法三维度分别进行 LDS 功能验证。

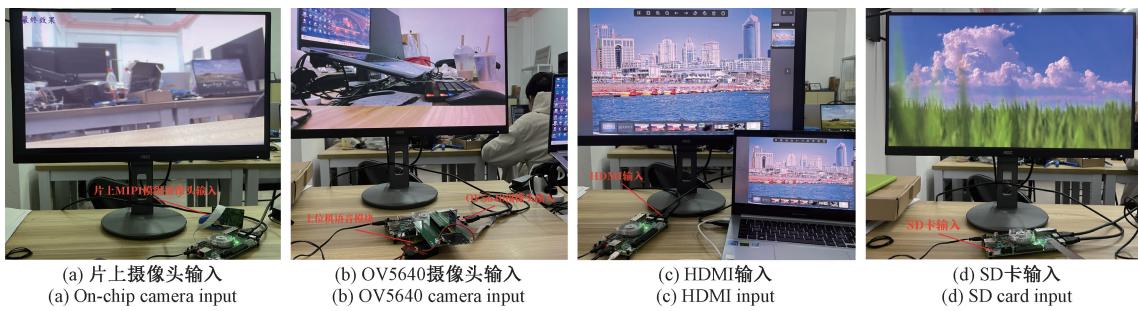

#### 1) 接口上实验验证

接口维度上,实验支持四异构接口输入,片上摄像头通过 MIPI 协议完成采集、OV5640 摄像头通过 DVP 协议完成采集、笔记本电脑视频源通过 HDMI 完成输入、SD 卡内置视频通过 SDIO 协议完成读取,基于 LDS 选择一通道进行图像处理,结果通过 HDMI 输出到显示屏,并通过 Qt 上位机完成如图 10 所示的异构接口动态切换。

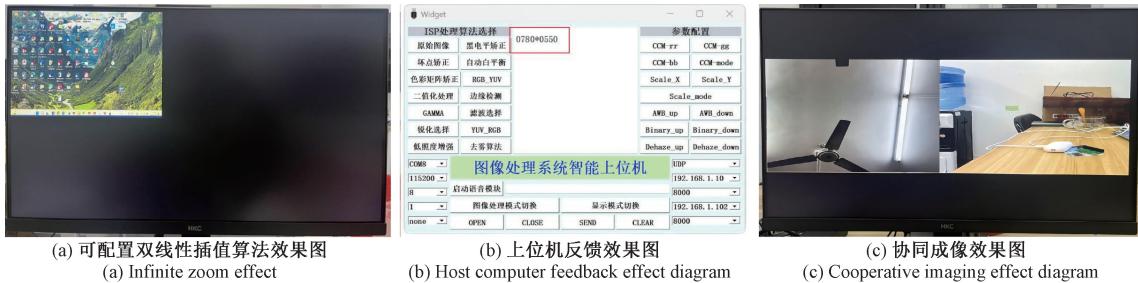

接着,完成双传感器拼接效果验证。实验路径上,首先验证如图 11(a)所示可配置双线性插值算法效果,上位机 UI 界面及其能接收到的分辨率反馈效果如图 11(b)所示,在  $1080P @ 60$  fps 输出的实验场景下,可配置双线性插值算法时延  $\leq 1.2$  ms, 峰值噪声比<sup>[17]</sup>  $\geq 38$  dB。然后通过上位机控件调度片上 MIPI 模组摄像头与 OV5640 摄像头双接口完成缩放、帧率匹配与拼接操作,最后输出如图 11(c)所示的  $1920 \times 540 @ 60$  fps 协同成像效果。

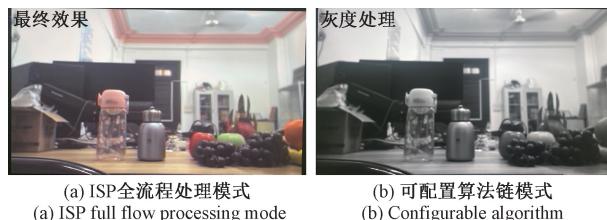

#### 2) 流程上实验验证

通过上位机完成两种处理流程的调度。ISP 全流程处理模式下,实验通过上位机控件选择 MIPI 摄像头作为输

图 10 四输入源切换显示效果图

Fig. 10 Four-input source switching display effect diagram

图 11 双传感器协同成像效果

Fig. 11 Collaborative imaging effect of dual sensors

入源,并在 UI 界面选择“全流程处理”操作,图 12(a)处理实验效果很大程度上还原场景的真实色彩;在可配置算法链模式下,实验通过上位机控件配置算法链,图 12(b)的算法链仅配置了灰度处理算法,完成效果验证。

图 12 动态处理流程效果验证

Fig. 12 Effectiveness verification of dynamic processing workflow

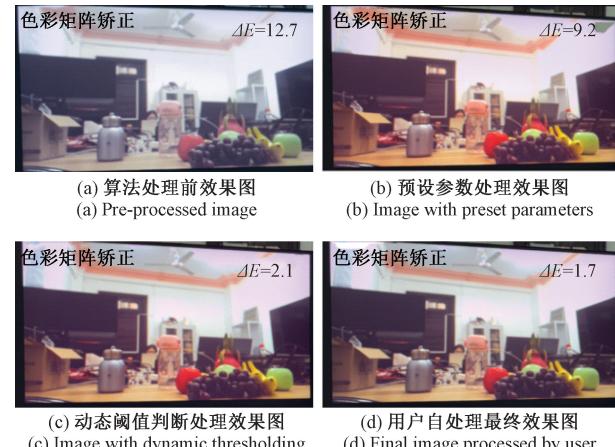

### 3) 算法上实验验证

实验对本研究基于 LDS 实现的动态参数优化 CCM 算法进行验证,图 13(a)原始图像平均色差  $\Delta E$  为 12.7,预设参数处理的  $\Delta E$  为图 13(b)的 9.2,通过动态阈值判断机制处理结果的  $\Delta E$  降至图 13(c)的 2.1(阈值设定为国际标准 ISO 17321 的  $\Delta E < 5$ )。动态阈值判断后,实验者根据人眼响应进行参数微调得到图 13(d), $\Delta E$  为 1.7,完成优异的动态处理效果。

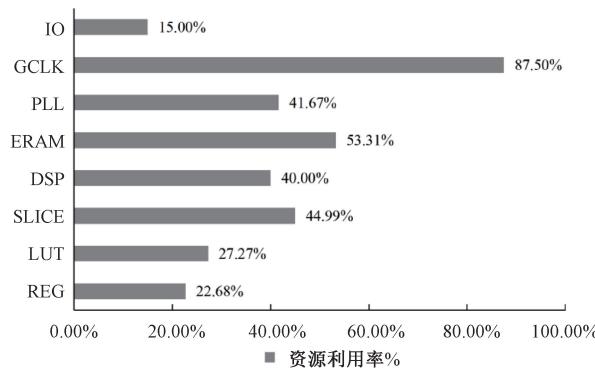

## 3.2 性能指标测试

采用 Anlogic 公司 SALPHOENIX<sup>®</sup> 1A 系列芯片,型号为 PH1A90,该芯片含 128 640 个 REG,115 776 个 LUT,64 320 个 SLICE,240 个 DSP,272 个 20 Kb 的 ERAM,12 个 PLL,32 个 GCLK 和 280 个 IO 等硬件资源,

图 13 动态优化算法效果验证

Fig. 13 Effectiveness verification of dynamic optimization algorithm

在 TD 6.0 上对本系统架构综合实现,其硬件资源占用率如图 14 所示,足以满足系统设计需求,且具备极大的拓展性。

文献[6]使用 Microblaze 软核完成硬件模块参数的初始化配置、实现流程复杂但计算量少的离焦量计算及与外设间的串口通信等功能,使用硬件资源完成具有大量重复运算的光斑定位算法、高速通信等功能,该软硬件协同方案与纯 Microblaze 软核方案对同样 5 幅图像进行处理速度对比,提高近 1 700 倍,可见前者具备实时优越性。但文献[6]仅通过软硬件协同的方式完成参数配置,本文将软硬件协同思想融入到 LDS 中,将传统 FPGA 开发中需硬

图 14 FPGA 硬件综合结果

Fig. 14 FPGA hardware synthesis results

件重构的功能转化为软件可编程任务,在软件端完成算法上参数动态控制、流程上处理链动态配置及接口上异构源动态调度任务,增强软硬件协同的应用性。

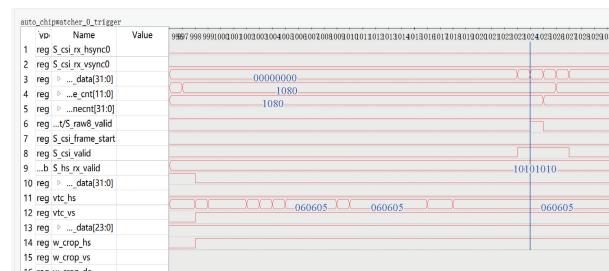

为了得到系统在软硬件协同下开发效率相关指标,分别对软硬件协同下的 UI 界面按键模式(后表述为模式 1)与语音识别模式(后表述为模式 2)及纯硬件实现下的 FPGA 片上按钮模式(后表述为模式 3)进行指令测试,随机进行 100 次操作判断系统是否准确响应及其处理速度(平均时延),接着通过 ChipWatcher 功能检测运行时如图 15 所示的波形变换测出响应时延,最终完成如表 1 所示实验结果统计。由表 1 可知,前两种模式的平均时延均  $\leq 20$  ms,而模式 3 的平均时延将近 2 000 ms。模式 1、2 均能完成 32 条指令,模式 3 由于按键数有限仅能支持 9 条指令,存在开发局限性问题。实验表明,软硬件协同的 LDS 方案(模式 1、2)能同时支持更多指令,进而更大程度地提升系统开发效率;此外,相较于纯硬件方案(模式 3),本文提出的方案能够在进行相同指令测试时最高提升 217 倍的处理速度,提升了整体系统的实时性;最后,选择软件端完成动态调度,使系统具备灵活性高、调试方便的特点,具备优异的人机交互感。

### 3.3 性能参数对比

本研究 LDS 方案与全静态集成方案、DPR 方案进行性能参数对比。选择 TD 6.0 软件在该板卡构建文献[2]全静态集成方案下支持 22 种 ISP 算法的可配置算法链,该方案下需要将所有可能的算法链静态搭建,运行时仅通过外部信号选择处理链。若需满足所有可能,组合将形成如

(a) 输入接口信号抓取

(a) Input interface signal capture

(b) 输出接口信号抓取

(b) Output interface signal capture

图 15 ChipWatcher 实时抓取波形图

Fig. 15 Real-time acquisition of waveforms using ChipWatcher

表 1 三控制形式的指标对比

Table 1 Comparison of three control forms indicators

| 控制模式  | 完成指令数 | 平均时延/ms  | 成功/总次数  |

|-------|-------|----------|---------|

| UI 按键 | 32    | 8.72     | 100/100 |

| 语音识别  | 32    | 19.08    | 96/100  |

| 片上按钮  | 9     | 1 889.64 | 100/100 |

式(10)所示 4 194 303 条算法链,其需要的 LUT 资源 FPGA 必然无法满足。为完成方案对比,实验设定每条算法链长度为 21,则共需要搭建 22 条算法链。接着,选择 Vivado 2020.2 软件在 XC7A50T FPGA 实现上述算法链的 DPR 方案,参考文献[3]的实现形式,利用 FPGA 中 DPR 技术重构粒度更小的特点以及允许每个重构区域根据功能需要动态加载和切换配置文件的特性,将 FPGA 划分为 4 个重构子区域,各区域分别执行接口驱动、图像处理、数据缓存以及参数配置的任务,每个重构区域支持细粒度的资源配置,根据不同算法链及参数配置的情况实时更改重构子区域的大小,通过 ICAP 控制器选择不同比特流文件完成动态调度效果,最终 3 种方案得到表 2 所示的可配置算法链部分的性能参数对比情况。

$$\sum_{k=1}^{22} C(22, k) = 2^{22} - 1 = 41\,943\,094 \quad (10)$$

表 2 实现可配置算法链的 3 种方案性能参数对比

Table 2 Comparison of three control forms indicators

| 实现方案         | 硬件资源          |               |               |            |            |

|--------------|---------------|---------------|---------------|------------|------------|

|              | REG           | LUT           | SLICE         | DSP        | ERAM       |

| 全静态集成        | 11 547        | 11 789        | 12 343        | 71         | 237        |

| DPR(全静态集成占比) | 3 978(34.45%) | 4 568(38.75%) | 4 967(40.24%) | 49(69.01%) | 79(33.33%) |

| LDS(全静态集成占比) | 4 168(36.10%) | 6 326(53.66%) | 5 988(48.51%) | 62(87.32%) | 90(37.98%) |

由表 2 可知,本实验以全静态集成方案为标准,算出 DPR/LDS 与该方案之间的资源消耗占比,最终算出各资源的占比平均数,DPR 为 43.16%,LDS 为 52.71%。相比于传统的全静态集成方案,DPR/LDS 方案均能大幅度减少硬件资源消耗量,且 LDS 方案仅高于 DPR 方案 9.55%,验证了本研究提出方案的资源可行性,具有良好的性能参数特性。因此,国产 FPGA 可以选择 LDS 方案避免 DPR 不兼容问题从而实现良好的动态调度效果。

## 4 结 论

本文基于安路科技公司的国产 FPGA 开发平台以及 Qt 框架,提出一个基于 LDS 的智能图像处理系统。该方案充分考虑到国产 FPGA 在图像处理领域开发程度不足的问题以及图像处理系统的集成度,采用 TD 6.0 作为 FPGA 的开发平台完成四接口异构输入、双传感器协同成像、算法处理链配置与 22 种 ISP 动态处理算法。同时,该方案还充分考虑到图像处理系统的智能性,采用 Qt 框架设计智能交互上位机,通过双通信协议实现上位机与 FPGA 板卡的互联,支持 UI 按键与语音双模进行系统控制与反馈,实现算法参数动态优化、显示模式切换等功能。与以往的图像处理系统相比,该方案为用户带来更完备的图像处理功能以及更优秀的人机交互性能,满足更高的实时视频处理需求,成功验证了接口、流程以及算法上的逻辑层动态调度能力与国产芯片的工业级可靠性。

## 参考文献

- [1] 周倩,李建伟,裴浩东.基于 FPGA 的自适应白平衡算法实现[J].电子测量技术,2025,48(3):35-42.

ZHOU Q, LI J W, PEI H D. Implementation of adaptive white balance algorithm based on FPGA[J]. Electronic Measurement Technology, 2025, 48 (3): 35-42.

- [2] 李先友,赵曙光,段永成,等.基于 FPGA 的实时 MIPI CSI-2 图像采集与处理系统[J].电子技术应用,2019,45(1):97-100.

LI X Y, ZHAO SH G, DUAN Y CH, et al. Real-time MIPI CSI-2 image acquisition and processing system based on FPGA[J]. Application of Electronic Technique, 2019, 45(1): 97-100.

- [3] KECHICHE L, TOUIL L, JEMAI M, et al. A power-aware real-time system for multi-video treatment on FPGA with dynamic partial reconfiguration and voltage scaling[J]. Engineering, Technology & Applied Science Research, 2022, 12(4): 8996-9004.

- [4] 郭彪,唐麒,文智敏,等.面向 SCA 的 DPR 软件架构设计与调度技术[J].计算机工程,2021,47 (12): 221-229.

- [5] GUO B, TANG Q, WEN ZH M, et al. Design and scheduling technology of DPR software architecture oriented to SCA[J]. Computer Engineering, 2021, 47(12): 221-229.

- [6] 田杰,王广龙,乔中涛,等.基于 FPGA 高速视频图像实时采集与处理系统设计[J].电子器件,2016,39(3): 623-627.

TIAN J, WANG G L, QIAO ZH T, et al. Design of a high-speed real-time video image acquisition and processing system based on FPGA [J]. Electronic Devices, 2016, 39(3): 623-627.

- [7] 赵子豪,骆冬根,路美娜,等.基于 SOPC 的检焦图像实时处理系统设计[J].电子测量技术,2022,45(9): 31-37.

ZHAO Z H, LUO D G, LU M N, et al. Design of real-time focus detection image processing system based on SOPC [J]. Electronic Measurement Technology, 2022, 45(9): 31-37.

- [8] 张萌,王镇,张文博,等.基于 ZYNQ 的千兆以太网数据传输系统设计[J].计算机与网络,2025,51(1): 32-38.

ZHANG M, WANG ZH, ZHANG W B, et al. Design of gigabit ethernet data transmission system based on ZYNQ[J]. Computer and Network, 2025, 51(1): 32-38.

- [9] 訾晶,张旭欣,金婕.基于 FPGA 动态重构的快速车牌识别系统[J].传感器与微系统,2019,38(12):69-72.

ZI J, ZHANG X X, JIN J. Fast license plate recognition system based on FPGA dynamic reconfiguration[J]. Sensors and Microsystems, 2019, 38(12): 69-72.

- [10] 张万才,张楠,杨文清,等.基于虚拟化的 GPU 异构资源池平台架构设计、关键技术及应用研究[J].电信科学,2024,40(9):162-175.

ZHANG W C, ZHANG N, YANG W Q, et al. Design, key technologies, and application research of a virtualization-based GPU heterogeneous resource pool platform architecture[J]. Telecommunication Science, 2024, 40(9): 162-175.

- [11] 张浩,武斌,曲睿杰.基于 Qt 的船模自主航行试验数据采集上位机软件设计[C].第二十一届中国航空测控技术年会论文集,2024:3.

ZHANG H, WU B, QU R J. Design of upper computer software for ship model autonomous navigation test data acquisition based on Qt[C]. 21st China Aviation Measurement and Control Technology Annual Conference, 2024: 3.

- [12] 何侃,田亚清,李强,等.基于 LD3320 的语音识别智能垃

- 圾桶设计[J].国外电子测量技术,2015,34(6):85-88.

- HE K, TIAN Y Q, LI Q, et al. Design of voice recognition intelligent trash bin based on LD3320[J]. Foreign Electronic Measurement Technology, 2015, 34(6): 85-88.

- [12] 王轶楷. 实时视频图像缩放系统的 FPGA 硬件实现[D]. 太原: 中北大学, 2023.

- WANG Y K. FPGA hardware implementation of real-time video image scaling system[D]. Taiyuan: North University of China, 2023.

- [13] 郑慧捷, 吕庆丰, 朱志行, 等. 基于 FPGA 的多接口视频编解码系统[J]. 电子测量技术, 2024, 47(18): 89-99.

- ZHENG H J, LYU Q F, ZHU ZH X, et al. Multi-interface video codec system based on FPGA[J]. Electronic Measurement Technology, 2024, 47(18):89-99.

- [14] KIM D, AFIFI M, KIM D, et al. CCMNet: Leveraging calibrated color correction matrices for cross-camera color constancy [J]. ArXiv preprint arXiv: 2504.07959, 2025.

- [15] 郎中亮, 张帆, 吴柄萱, 等. 皮肤肿瘤智能远程会诊系统研究[J]. 中国激光, 2024, 51(9):271-280.

- LANG ZH L, ZHANG F, WU B X, et al. Research on an intelligent remote consultation system for skin tumors[J]. Chinese Journal of Lasers, 2024, 51(9): 271-280.

- [16] 姚军财. 人眼亮度和色度对比敏感视觉特性的测量及其模型研究[J]. 应用光学, 2016, 37(6):880-886.

- YAO J C. Measurement of human eye's brightness and chromaticity contrast sensitivity visual characteristics and research on its model[J]. Applied Optics, 2016, 37(6): 880-886.

- [17] 刘玉红, 刘树英, 付福祥. 基于卷积神经网络的压缩感知重构算法优化[J]. 计算机科学, 2020, 47(3): 143-148.

- LIU Y H, LIU SH Y, FU F X. Optimization of compressed sensing reconstruction algorithm based on convolutional neural network[J]. Computer Science, 2020, 47(3): 143-148.

### 作者简介

谢家兴,博士,副教授,主要研究方向为物联网技术、电子技术在农业上的应用等。

E-mail: xjx1998@scau.edu.cn

李东峻,本科,主要研究方向为 FPGA 图像处理等。

E-mail: damjan84@163.com

周欣红,本科,主要研究方向为数字集成电路设计等。

E-mail: 2560166914@qq.com

莫汉东,本科,主要研究方向为数字集成电路设计等。

E-mail: mohandong@foxmail.com

罗洋,本科,主要研究方向为智能监测与评估等。

E-mail: luoyang1002@stu.scau.edu.cn

刘洪山(通信作者),博士,副教授,主要研究方向为智能检测与控制技术等。

E-mail: hugoliu@scau.edu.cn