# 基于 ZYNQ 的单目面结构光三维测量系统设计 \*

万基茂 张乾坤 周哲海 王福森 班正将

(北京信息科技大学仪器科学与光电工程学院 北京 100192)

**摘要:** 针对基于嵌入式平台的结构光三维测量系统普遍存在算法不完整、实现复杂的问题,设计了一种基于 ZYNQ 的单目面结构光三维测量系统。该系统结合 FPGA 与 ARM 处理器,利用 Vitis HLS 技术实现了基于互补格雷码结合相移算法的高速解码与重建。首先,设计了 FPGA 图像采集模块,并对结构光图像进行灰度化和中值滤波预处理。随后,利用 Vitis HLS 实现了结构光图像二值化、相位计算和三维点云求解。最后,基于 ARM 处理器开发了 CMOS 相机和图像处理的控制程序,实现了系统模块控制以及灵活的系统参数标定,标定重投影误差低至 0.0921 pixel。实验结果表明,系统对复杂物体表面具有高鲁棒性,标准球测量的直径拟合均方根误差低至 0.1037 mm,解码与重建耗时仅为 112.67 ms,速度接近 CPU 的 31.5 倍,与集成 GPU 相当,ZYNQ 平台功耗仅为 2.696 W,验证了系统的可行性和有效性。

**关键词:** 三维测量;面结构光;ZYNQ;Vitis HLS

中图分类号: TP391.41; TN29 文献标识码: A 国家标准学科分类代码: 510.20

## Design of a monocular surface structured light 3D measurement system based on ZYNQ

Wan Jimao Zhang Qiankun Zhou Zhehai Wang Fusen Ban Zhengjiang

(School of Instrument Science and Opto-electronics Engineering, Beijing Information Science and Technology

University, Beijing 100192, China)

**Abstract:** Aiming at the common problems of incomplete algorithms and complex implementation in structured light 3D measurement systems based on embedded platforms, a monocular surface structured light 3D measurement system based on ZYNQ was designed. This system combines FPGA and ARM processors, utilizing Vitis HLS technology to achieve high-speed decoding and reconstruction based on complementary Gray code combined with phase-shifting algorithms. First, an FPGA image acquisition module was designed, and the structured light images were preprocessed through grayscale conversion and median filtering. Subsequently, Vitis HLS was used to implement structured light image binarization, phase calculation, and 3D point cloud solving. Finally, a control program for the CMOS camera and image processing was developed based on the ARM processor, enabling system module control and flexible system parameter calibration, with a reprojection error as low as 0.0921 pixels. Experimental results show that the system exhibits high robustness for complex object surfaces, with a root mean square error of diameter fitting for standard sphere measurements as low as 0.1037 mm. The decoding and reconstruction time is only 112.67 ms, approaching 31.5 times the speed of a CPU and comparable to an integrated GPU, while the power consumption of the ZYNQ platform is only 2.696 W, verifying the feasibility and effectiveness of the system.

**Keywords:** 3D measurement; surface structured light; ZYNQ; Vitis HLS

## 0 引言

结构光三维测量技术因其精度高、速度快、非接触等优势在工业生产<sup>[1]</sup>、文化遗产保护<sup>[2]</sup>、医学成像<sup>[3]</sup>等领域的应

用日益广泛。面结构光也称为编码结构光,利用投影仪投射带有编码信息的结构光图案至被测物体表面,在另一角度利用相机拍摄变形图案,通过解调变形图案,最终获取物体的三维形貌信息<sup>[4]</sup>。条纹投影轮廓术(fringe projection

profilometry, FPP) 作为面结构光三维测量技术中最具代表性的方法<sup>[5]</sup>, 为提高其测量实时性,许多研究人员在相位计算、相位展开以及三维重建方面取得了很大的进展。然而,传统面结构光三维测量系统由投影仪、工业相机以及计算机组成,存在便携性较差、功耗高的问题,制约了其在嵌入式设备上的实时应用。

为实现基于嵌入式平台的结构光三维测量,有学者开始研究基于现场可编程门阵列(field-programmable gate array, FPGA)、ZYNQ 等处理芯片的结构光三维测量算法实现方法。Junger 等<sup>[6]</sup>基于 Xilinx ZYNQ 7020 SoC 提出了一种基于立体相位测量轮廓术(phase measurement profilometry, PMP)系统的 FPGA 加速镜头去畸变和校正算法,占用内存负载仅为 OpenCV 库算法的 1/4。Lyu 等<sup>[7]</sup>基于 Xilinx ZYNQ UltraScale SoC 提出了一种用于 PMP 算法的 FPGA 架构,并设计了用于工业应用的高速光学三维测量传感器。Liu 等<sup>[8]</sup>基于 Xilinx spartan 3 FPGA 平台提出了一种用于 PMP 算法的高速、高精度 FPGA 架构,该系统使用 12 幅正弦条纹来实现三维形貌测量,并校正投影仪的反相位以提高测量精度。Chen 等<sup>[9]</sup>提出了一种基于 Xilinx ZYNQ 7100 SoC 的高速相位结构光集成架构,该架构实现了三频四步相移硬件算法及高精度的实时三维形貌测量,解码速度达到 40.15 fps。虽然这些研究极大地促进了结构光三维测量系统的集成化,但普遍还存在结构光算法不完整、实现复杂的问题。

针对上述问题,本文旨在设计一种基于嵌入式平台的结构光三维测量系统,在实现完整结构光算法的同时降低设计难度并保证测量精度及速度。所设计的系统基于 Xilinx ZYNQ 7100 SoC, 利用高层次综合(high-level synthesis, HLS)技术实现了互补格雷码结合相移的结构光算法,仅需投影 9 张图案即能实现三维重建。此外,通过设计结构光图像预处理模块和系统控制程序,增强了系统功能。实验结果表明该系统同时具有较高的鲁棒性和优秀的性能,能够满足基于嵌入式平台实现结构光三维测量的需求。

## 1 单面结构光三维测量系统原理

### 1.1 系统基本结构与参数标定

单面结构光三维测量系统采用单一相机与数字投影仪的紧凑结构,将结构光编码技术与单目视觉几何相结合,具有结构简单、成本低廉、实时性强等优势。

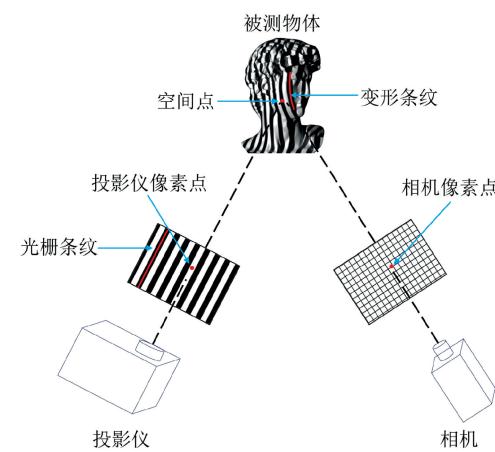

如图 1 所示为单面结构光三维测量系统的基本结构<sup>[10]</sup>,由一个投影仪和一个工业相机组成。首先进行系统标定获得相机和投影仪的内外参数以及畸变系数,然后将预先设计的编码图案投射至被测物体,同时相机从不同的视点捕获变形图案,经过相位计算、相位展开、三维点云求解等操作后获得物体的三维坐标信息,从而实现对物体尺寸的精确测量。

图 1 单面结构光三维测量系统基本结构

Fig. 1 Basic structure of monocular surface structured light 3D measurement system

系统参数标定作为三维测量的前置工作,标定精度直接影响到系统三维测量的精度和有效性。系统参数标定包括相机标定和投影仪标定,本文采用基于局部单应性矩阵的结构光系统标定方法<sup>[11]</sup>对系统进行标定。通过局部单应性矩阵算法将图像平面根据角点坐标划分为不同的矩形区域,对每个区域单独计算其单应性矩阵,从而将投影仪标定转化为相机标定。该方法考虑了相机和投影仪镜头的非线性畸变,极大提高了系统标定的精度。

### 1.2 互补格雷码结合相移的结构光算法

基于相移法<sup>[12]</sup>的结构光三维测量技术通过计算投影条纹、被测物体表面和相机像平面之间对应点的三角关系来实现物体三维形貌的测量。本文采用四步相移法求取物体的相位信息,相移方程如式(1)所示。

$$\begin{aligned} I_1(x, y) &= A(x, y) + B(x, y) \cos[\varphi(x, y)] \\ I_2(x, y) &= A(x, y) + B(x, y) \cos[\varphi(x, y) + \frac{\pi}{2}] \\ I_3(x, y) &= A(x, y) + B(x, y) \cos[\varphi(x, y) + \pi] \\ I_4(x, y) &= A(x, y) + B(x, y) \cos[\varphi(x, y) + \frac{3\pi}{2}] \end{aligned} \quad (1)$$

其中,  $I_n(x, y)$  为变形条纹光强分布,  $A(x, y)$  为背景光强,  $B(x, y)$  为强度调制参数,  $\varphi(x, y)$  为待求解的包裹相位,根据式(1)联立方程组可得到包裹相位求解公式:

$$\varphi(x, y) = \arctan \frac{I_4(x, y) - I_2(x, y)}{I_1(x, y) - I_3(x, y)} \quad (2)$$

由于包裹相位存在跳变,导致相位不连续。为确保后续三维点云求解的准确性,需要对包裹相位进行展开,从而获得连续的绝对相位。包裹相位展开公式如下:

$$\phi(x, y) = \varphi(x, y) + 2\pi n(x, y) \quad (3)$$

其中,  $\phi(x, y)$  为所求的绝对相位,  $n(x, y)$  为像素点对应的条纹级次,通过求解条纹级次实现包裹相位的展开,继而得到连续的绝对相位。由于包裹相位被截断在  $(-\pi, \pi]$ ,

$\pi$ )之间,为了更好地求取条纹级次,本文采用互补格雷码<sup>[13]</sup>作为辅助编解码方法,通过格雷码标记条纹级次辅助展开包裹相位。编码 4 位格雷码以及 1 位具有正弦条纹宽度 1/2 周期的互补格雷码,利用前 4 张格雷码图案得到条纹级次  $n_1$ ,全部 5 张格雷码图案得到条纹级次  $n_2$ , $n_1$  和  $n_2$  的条纹级次边沿恰好错开。在非边沿处使用  $n_1$  而在边沿处使用  $n_2$  进行相位展开,从而消除了包裹相位求解时边沿处的跳变误差,具体实现原理如式(4)所示。

$$\varphi(x, y) = \begin{cases} \varphi(x, y) + 2\pi n_2(x, y), & \varphi(x, y) \leq -\pi/2 \\ \varphi(x, y) + 2\pi n_2(x, y), & -\pi/2 < \varphi(x, y) < \pi/2 \\ \varphi(x, y) + 2\pi n_2(x, y) - 2\pi, & \varphi(x, y) \geq \pi/2 \end{cases} \quad (4)$$

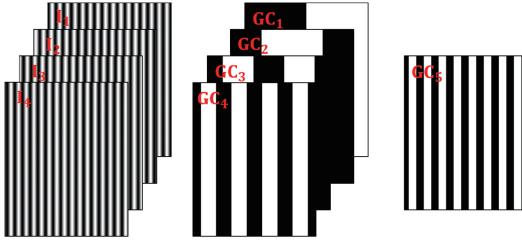

本文的编码方案如图 2 所示,编码图案分辨率为 912 pixels  $\times$  1 140 pixels,其中  $I_1 \sim I_4$  为四步相移图案,  $GC_1 \sim GC_4$  为普通格雷码图案,  $GC_5$  为互补格雷码图案。

图 2 互补格雷码结合相移编码方案

Fig. 2 Complementary gray code combined with phase-shifting encoding scheme

获得绝对相位后,基于三角立体模型,将投影仪作为逆相机替换双目立体视觉<sup>[14]</sup>中的左相机,结合系统标定获得的相机和投影仪内外参数,构建相机和投影仪的投影矩阵,解关于投影矩阵的方程组实现三维重建。三维点云求解方程组如式(5)所示。

$$\begin{bmatrix} x_w \\ y_w \\ z_w \end{bmatrix} = \begin{bmatrix} p_{11}^c - p_{31}^c x & p_{12}^c - p_{32}^c x & p_{13}^c - p_{33}^c x \\ p_{21}^c - p_{31}^c y & p_{22}^c - p_{32}^c y & p_{23}^c - p_{33}^c y \\ p_{21}^p - p_{31}^p x_p & p_{22}^p - p_{32}^p x_p & p_{23}^p - p_{33}^p x_p \end{bmatrix}^{-1} \begin{bmatrix} p_{14}^c - p_{34}^c x \\ p_{24}^c - p_{34}^c y \\ p_{24}^p - p_{34}^p x_p \end{bmatrix} \quad (5)$$

其中,  $x_w, y_w, z_w$  为物体点云的世界坐标,  $(x, y)^T$  为相机像素坐标,  $x_p$  为投影仪水平坐标,  $p_{11}^c \sim p_{34}^c$  为相机投影矩阵元素,  $p_{21}^p, p_{31}^p, p_{22}^p, p_{32}^p$  为投影仪投影矩阵元素。

## 2 系统设计与实现

### 2.1 系统总体设计框架与工作原理

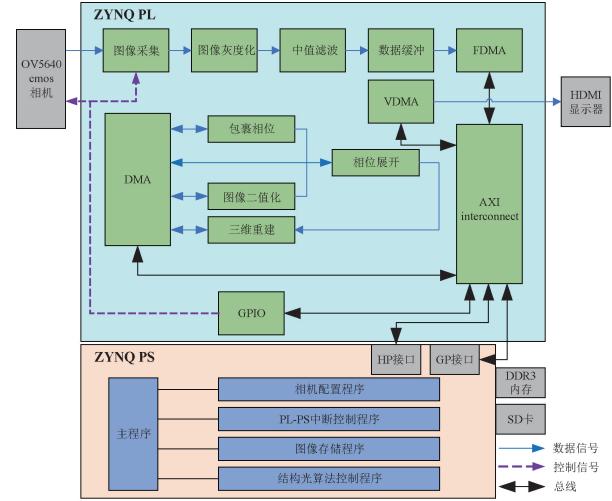

传统单目面结构光三维测量系统采用计算机作为投影控制和数据处理设备,相机为工业相机。本文将数据处理任务转移至 ZYNQ 平台而仅保留计算机的投影控制功能,使用与 ZYNQ 平台直接相连的 OV5640 CMOS 相机作为

图像采集设备,采集图像分辨率为 1 280 pixel  $\times$  720 pixel,相机捕获完成条纹图案后即可利用 ZYNQ 平台实现完整的结构光三维测量。ZYNQ 芯片由基于 FPGA 的可编程逻辑(programmable logic, PL)以及基于 ARM 处理器的处理系统(processing system, PS)构成。系统在 PL 端实现图像采集、结构光图像预处理以及结构光解码和三维重建,在 PS 端对相机的配置参数、图像采集与预处理模块以及结构光算法模块进行控制,从而实现完整的系统功能。系统的总体设计框架如图 3 所示。

图 3 系统总体设计框架

Fig. 3 Overall design framework of the system

系统的工作原理如下:首先,PS 端相机配置程序初始化并配置 OV5640 相机参数,由通用输入输出(general-purpose input/output, GPIO)进行控制。随后,PS 控制 PL 端相机捕获变形条纹,通过图像灰度化模块将原始 RGB 图片转为灰度图并由中值滤波模块对图像进行滤波处理。接着,利用数据缓冲知识产权核(intellectual property core, IP)和快速直接内存访问(fast direct memory access, FDMA)IP 对图像数据执行多帧缓冲后写入 DDR3 内存,同时使用视频直接内存访问(video direct memory access, VDMA)IP 从 DDR3 内存中读取数据至 HDMI 显示器进行实时查看,并通过 PS 控制 PL-PS 中断控制程序和图像存储程序将图像存储至 SD 卡。最后,通过 PS 控制结构光算法模块实现图像二值化、包裹相位计算、相位展开以及三维重建,三维坐标以文本格式写出,整个结构光解码与三维重建过程通过直接内存访问(direct memory access, DMA)IP 进行数据的读写操作。PL 和 PS 之间的通信通过高级可扩展接口(advanced extensible interface, AXI)链接实现。

### 2.2 结构光图像采集与预处理模块

系统通过软硬件协同设计的方式实现结构光图像的采集与预处理。软件端使用相机配置程序对 OV5640 相机进行寄存器配置,并实现串行相机控制总线(serial camera control bus, SCCB)协议的数据通信,包括时钟配置、复位、

数据传输控制以及相机参数设置,如曝光控制和镜头补偿等。通过配置 PL-PS 中断,设计了图像自动存储程序,每 5 s 定时存储一次图像,从而实现与投影仪投射图像的同步采集。BMP 图像存储程序通过调用外部库提供的函数,进行文件的打开、读取和写入操作,将显存中的图像数据以 BMP 格式保存至 SD 卡中。硬件端图像采集模块主要由 OV5640 IP、数据缓冲 IP、FDMA IP 和 VDMA IP 组成。OV5640 IP 负责视频图像的采集,而数据缓冲 IP、FDMA IP 和 VDMA IP 则实现数据的多帧缓冲与传输,以确保高质量的图像采集。结构光图像预处理模块包括图像灰度化 IP 和中值滤波 IP,实现了图像的灰度化处理和中值滤波操作。

为方便后续对格雷码图像进行二值化,需对相机采集到的结构光图像进行灰度化<sup>[15]</sup>预处理。系统采用最流行的加权均值法作为图像灰度化处理方法,具体实现原理如式(6)所示。

$$I(x, y) = 0.299 \times R(x, y) + 0.587 \times G(x, y) + 0.114 \times B(x, y) \quad (6)$$

其中,  $I(x, y)$  表示灰度值,  $R(x, y)$ 、 $G(x, y)$ 、 $B(x, y)$  分别为彩色图像 R、G、B 通道的像素值。0.299、0.587、0.114 分别表示人眼对红色、绿色和蓝色的感知权重系数。

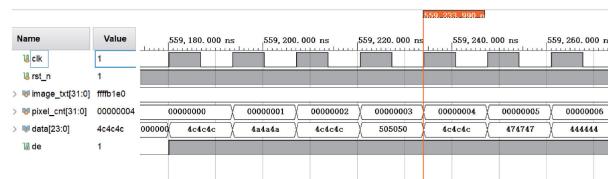

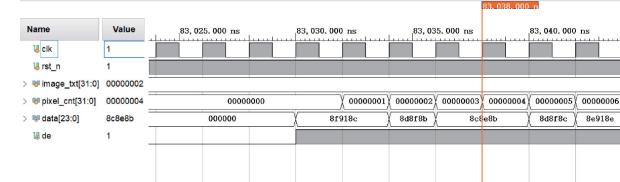

使用 Verilog 硬件描述语言实现基于 FPGA 的图像灰度化算法。算法采用两级流水线设计,第一级完成 RGB 分量的乘法运算,第二级进行加法求和。仿真时,将 1 280 pixel  $\times$  720 pixel 分辨率的测试图像转换为文本格式输入,经灰度化处理后输出结果数据。仿真验证通过后,将算法封装为 IP,以便集成和复用。如图 4 所示为使用 Vivado XSIM 仿真工具得到的算法仿真波形。由仿真波形可知,算法成功实现了彩色图像的灰度化。

图 4 图像灰度化算法仿真波形

Fig. 4 Simulation waveform of the image grayscale algorithm

为抑制结构光图像的噪声,系统采用中值滤波算法<sup>[16]</sup>进行滤波预处理操作。中值滤波算法的核心原理是将图像中某一点的像素值替换为其邻域内所有像素值的中值,从而有效消除噪声点并保留边缘细节,通过二维滑动模板对邻域像素值排序,输出序列的中值作为滤波结果。具体实现原理如式(7)所示。

$$g(x, y) = \text{med}(f(x - k, y - l), (k, l \in W)) \quad (7)$$

其中,  $f(x, y)$ 、 $g(x, y)$  分别为原始图像和中值滤波处理后图像,  $W$  为中值滤波中定义的邻域模板,用于确定中值计算的像素范围。基于 FPGA 的中值滤波算法采用四级流水线设计,第一级获取  $3 \times 3$  窗口的 RGB 数据,第二

级对每一行的 3 个像素进行排序,第三级对行排序结果进行行列排序,第四级从排序结果中选取中值,最终输出中值滤波后结果。如图 5 所示为所设计中值滤波算法的 Vivado XSIM 仿真波形。由仿真波形可知,算法成功对图像数据进行了中值滤波处理。

图 5 中值滤波算法仿真波形

Fig. 5 Simulation waveform of the median filter algorithm

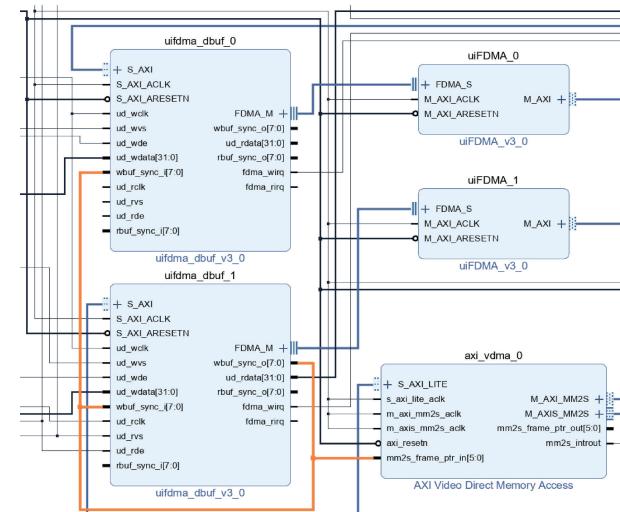

为消除或减少图像显示中的闪烁、撕裂等问题,并降低图像显示的延迟,系统采用双 uifdma\_dbuf IP 及 FDMA IP 实现图像数据的缓冲与传输操作。首先将缓冲帧数设置为 3, uifdma\_dbuf\_0 IP 仅使能写数据通道,通过 AXI 总线将预处理后的结构光图像数据经多帧缓冲后由 FDMA 写入 DDR。uifdma\_dbuf\_1 IP 使能读和写数据通道,通过 AXI 总线从 DDR 中读取图像数据,经多帧缓冲后由 FDMA 再次写入 DDR,并利用 VDMA IP 获取图像数据进行实时显示。为避免图像撕裂,uifdma\_dbuf\_1 IP 的写输出帧同步信号与 uifdma\_dbuf\_1 IP 的写输入帧同步信号、uifdma\_dbuf\_0 IP 的写输入帧同步信号以及 VDMA IP 的帧指针信号相连接。为提高设计效率,使用 Vivado 2020.2 FPGA 开发平台对模块进行图形化设计,如图 6 所示为数据缓冲与传输 IP 的图形化设计方案。

图 6 数据缓冲与传输 IP 图形化设计方案

Fig. 6 Graphical design scheme of data buffering and transmission IP

## 2.3 结构光算法模块的 Vitis HLS 实现

鉴于传统基于 FPGA 的结构光算法实现难度较高、开发周期长,为降低设计难度,本文提出了一种基于 Vitis HLS 的系统实现方案。Vitis HLS 是由 Xilinx 公司开发的

一款工具,旨在简化 FPGA 设计流程。它允许设计者使用高级编程语言(如 C、C++)进行硬件设计,进而生成硬件描述语言(如 Verilog、VHDL),这大大降低了设计的复杂性,缩短了开发时间<sup>[17]</sup>。本文采用 C++作为高级编程语言,通过 Vitis HLS 将其转化为 Verilog 语言进行设计,经过 C 综合、C 仿真、C/RTL 联合仿真后将所设计的模块封装为 IP,最后在 PS 中进行调用。

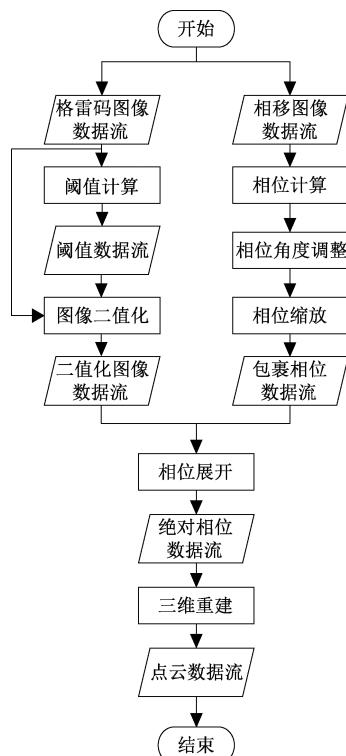

基于互补格雷码结合相移的结构光算法实现包括图像二值化、包裹相位计算、包裹相位展开以及三维重建。图像二值化模块将采集的 5 张格雷码图案进行二值化,以减少数据处理量、提高阈值计算精度。首先输入格雷码图像数据流,经阈值计算后输出阈值数据流,将格雷码图像数据与阈值数据进行比较得到二值化结果。包裹相位计算模块首先从 4 个相移图像数据流读取四步相移数据,根据式(2)进行相位计算。然后经过相位角度调整将负相位值转换为正值,接着将相位缩放至 0~255 范围内,以便输出和显示,最后将相位值写出输出流数据。包裹相位展开模块首先获取前级模块输出的二值化图像以及包裹相位,然后根据式(4)进行相位展开计算,最后输出获得的绝对相位。三维重建模块以获得的绝对相位作为输入数据流,根据式(5)进行三维点云求解,以文本的形式输出点云坐标数据流并保存至 SD 卡。如图 7 所示为结构光算法模块的 Vitis HLS 设计流程。

图 7 结构光算法模块 Vitis HLS 设计流程

Fig. 7 Vitis HLS design flow of the structured light algorithm module

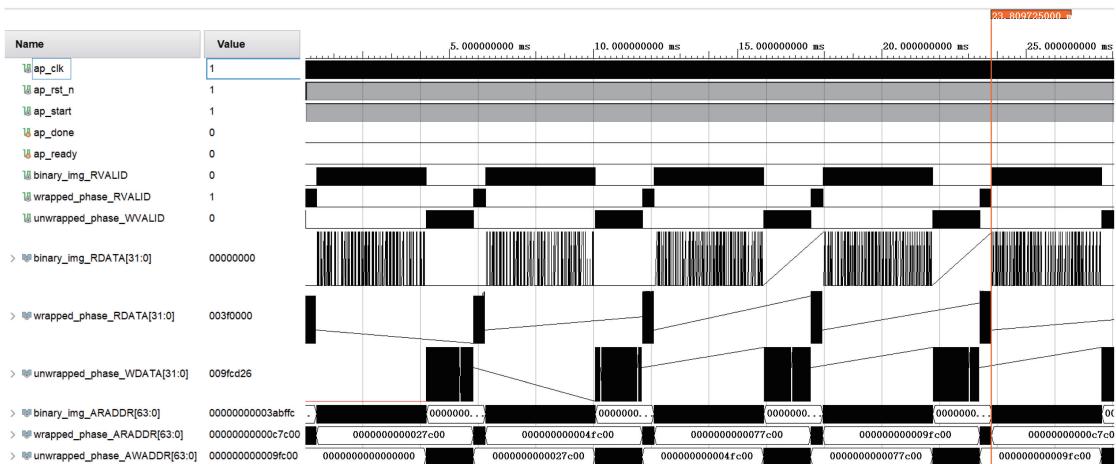

为验证模块的有效性,对设计的模块进行了 C 仿真以及 C/RTL 联合仿真。如图 8、9 所示为分别 C 仿真结果以及使用 Vivado XSIM 仿真工具对包裹相位展开模块进行 C/RTL 联合仿真得到的仿真波形。由 C 仿真结果及联合仿真波形可知,所设计的 Vitis HLS C++ 程序以及综合后的 RTL Verilog 程序成功实现了结构光解码功能,满足设计要求。

图 8 结构光算法模块 C 仿真结果

Fig. 8 C imulation results of the structured light algorithm module

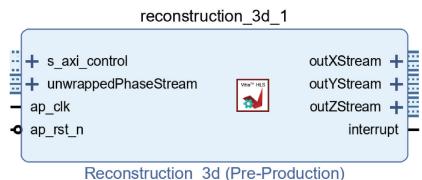

完成模块的功能仿真验证后,需将 Verilog 代码封装为 IP,以便后续的图形化设计调用。如图 10 所示为三维重建模块的 IP 封装图,其中 s\_axi\_control 为 AXI 接口控制信号,unwrappedPhaseStream 为读取的绝对相位输入数据流,ap\_clk 为时钟信号,ap\_rst\_n 为复位信号,outXStream、outYStream 和 outZStream 分别为重建点云的 X、Y 和 Z 坐标输出数据流,interrupt 为模块的中断控制信号。

## 2.4 系统图形化设计及模块调用

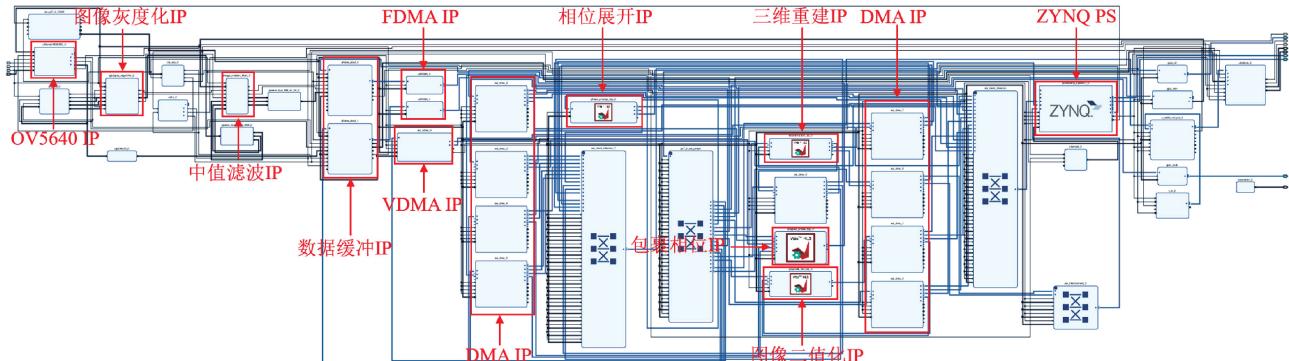

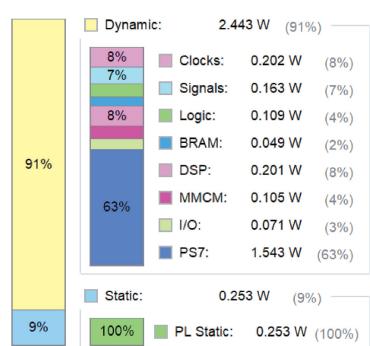

使用 Vivado 2020.2 FPGA 开发平台将所有 IP 的数据信号、控制信号以及总线相连接,得到如图 11 所示的系统图形化设计工程图。系统硬件资源使用情况和功耗分别如表 1、图 12 所示。可见 ZYNQ 平台完全满足系统的硬件资源要求,系统功耗仅为 2.696 W,满足低功耗要求。

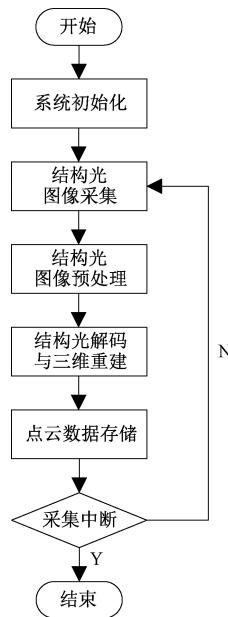

全部模块的调用通过 PS 端的主程序进行控制,利用 Vitis 2020.2 软件开发平台进行 ARM 程序的开发。经过 IP 初始化、DMA 初始化、IP 参数配置等流程进行系统初始化,然后依次调用结构光算法模块 IP 实现结构光图像解码与三维重建,结合结构光图像采集与预处理模块实现完整的结构光三维测量系统功能。设计流程如图 13 所示。

## 3 三维测量实验与结果分析

### 3.1 实验系统搭建与系统参数标定

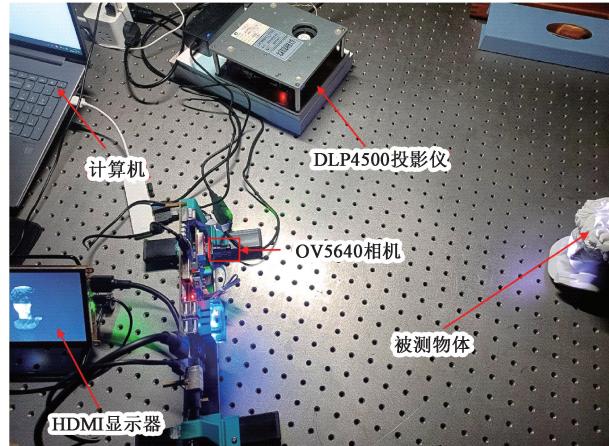

本文采用安华光公司的 DLP LightCrafter 4500 作

图 9 包裹相位展开模块 C/RTL 联合仿真波形

Fig. 9 C/RTL co-simulation waveform of the phase unwrapping module

图 10 三维重建模块封装 IP

Fig. 10 Encapsulated IP of the 3D reconstruction module

为投影设备, 投影图案分辨率为 1 140 pixel  $\times$  912 pixel。ZYNQ 平台型号为米联客公司的 MZ7100FA, 其核心芯片为 Xilinx ZYNQ 7100 SoC, 搭建的实验系统如图 14 所示。通过图像采集模块完成了测量系统的系统参数标定前置任务, 采用文献[11]提供的 scan3d-capture 软件实现系统标定。结果显示相机标定重投影误差为 0.059 9 pixel、投影仪标定重投影误差为 0.114 4 pixel, 相机-投影仪联合标

图 11 系统图形化设计工程图

Fig. 11 Graphical design engineering diagram of the system

表 1 系统硬件资源使用情况

Table 1 Hardware resources utilization status of the system

| 硬件资源   | 使用量    | 总量      | 百分比/% |

|--------|--------|---------|-------|

| LUT    | 57 032 | 277 400 | 20.56 |

| LUTRAM | 4 151  | 108 200 | 3.84  |

| FF     | 69 635 | 554 800 | 12.55 |

| BRAM   | 42.50  | 755     | 5.63  |

| DSP    | 286    | 2 020   | 14.16 |

| IO     | 25     | 362     | 6.91  |

| MMCM   | 1      | 8       | 12.50 |

图 12 系统功耗

Fig. 12 Power consumption of the system

图 13 PS 端主程序设计流程

Fig. 13 Design flow of the main program on the PS side

图 14 实验系统

Fig. 14 Experimental system

定重投影误差为 0.092 1 pixel, 这些误差值均低于通常可接受的 0.5 pixel 上限, 表明系统的标定精度较高。

### 3.2 三维测量实验与分析

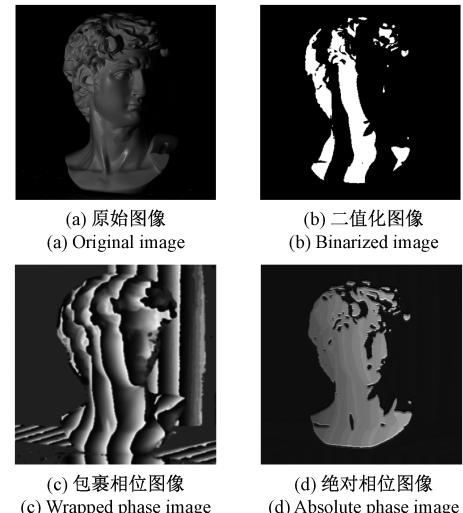

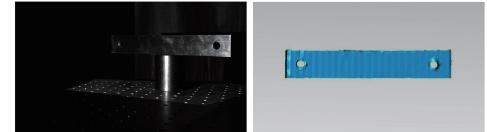

为验证系统的可行性并评估系统对复杂物体的测量能力, 结合获取的系统标定参数, 利用设计的系统分别对人像模型、陶瓷罐、规则金属工件以及不规则金属工件开展了三维测量实验。采用 Geomagic Studio 2013 软件对生成的点云数据进行三维表面重建及可视化<sup>[18]</sup>, 如图 15 所示为人像模型、陶瓷罐、规则金属工件以及不规则金属工件的三维重建结果。

由图 15 可知, 设计的系统能够很好地对具有复杂深度信息且表面光滑的人像模型、具有复杂表面颜色变化且表面粗糙的陶瓷罐以及表面具有高反射特性的规则或不

(a) 人像模型及其三维重建结果

(a) The portrait model and its 3D reconstruction result

(b) 陶瓷罐及其三维重建结果

(b) The ceramic jar and its 3D reconstruction result

(c) 规则金属工件及其三维重建结果

(c) The regular metal workpiece and its 3D reconstruction result

(d) 不规则金属工件及其三维重建结果

(d) The irregular metal workpiece and its 3D reconstruction result

图 15 复杂物体三维重建结果

Fig. 15 3D reconstruction results of complex objects

规则金属工件进行三维形貌测量。表明设计的系统对被测物体物体表面的复杂程度、粗糙程度以及反射特性具有较强的鲁棒性, 能够满足不同场景的测量需求。

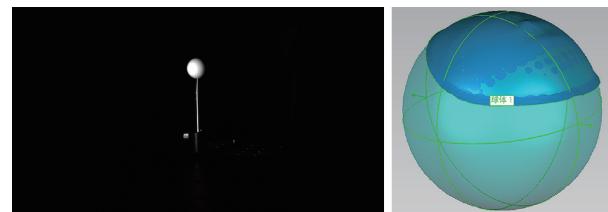

为更好地对系统的三维测量精度进行定量分析, 对 30 mm 直径标准球重建表面进行了球体拟合, 分析直径拟合误差从而评估系统的测量精度, 拟合效果如图 16 所示。

图 16 标准球及其重建表面球体拟合效果

Fig. 16 The standard sphere and the fitting effect of its reconstructed surface sphere

为评估系统性能, 开展了基于 PC 平台的结构光三维测量对比实验, 并与文献[8]中基于 FPGA 的倍频相移算法面结构光三维测量系统进行对比分析。PC 平台 CPU 为 AMD R7 8845HS (3.8 GHz), GPU 为集成 GPU (Radeon 780 M Graphics), 使用 Python 进行基于 CPU 的三维测量实验, 使用 Visual Studio 2019 + OpenCV 4.8.0 进行基于集成 GPU 的三维测量实验。以标准球 10 次测

量直径拟合的均方根误差<sup>[19]</sup>作为测量精度评价指标,不同平台的拟合结果如表 2 所示。由表可知,本文设计的系统与文献[8]中 FPGA 平台的误差为 0.053 mm,与集成 GPU 的误差为 0.0331 mm,与 CPU 的误差仅为 0.0239 mm,三维测量精度较高。

表 2 不同平台标准球直径拟合结果对比

Table 2 Comparison of standard sphere diameter fitting results on different platforms

| 评估参数  | CPU    | 集成 GPU | 文献[8]  | 本文系统   | mm |

|-------|--------|--------|--------|--------|----|

|       |        |        | (FPGA) | (ZYNQ) |    |

| 均方根误差 | 0.0798 | 0.0706 | 0.0507 | 0.1037 |    |

以标准球 10 次测量的包裹相位、相位展开以及三维测量模块的平均运行所需时间作为测量速度评价指标,不同平台的运行耗时情况如表 3 所示。结果表明本文设计的系统各模块运行总耗时仅为 112.67 ms,相比于 CPU 的 3 541.22 ms、集成 GPU 的 112.30 ms,速度接近 CPU 的 31.5 倍,同时与集成 GPU 基本持平,实现了高速三维测量。

表 3 不同平台运行耗时情况对比

Table 3 Comparison of running time on different platforms

| 评估参数 | CPU      | 集成 GPU | 文献[8]  | 本文系统   | ms |

|------|----------|--------|--------|--------|----|

|      |          |        | (FPGA) | (ZYNQ) |    |

| 包裹相位 | 1 173.36 | 8.64   | —      | 9.22   |    |

| 相位展开 | 1 303.48 | 96.47  | —      | 94.23  |    |

| 三维重建 | 1 064.38 | 7.19   | —      | 9.22   |    |

| 总共   | 3 541.22 | 112.30 | 30.72  | 112.67 |    |

实验结果表明,本文设计的单目面结构光三维测量系统在保证较高鲁棒性的同时,兼具高测量精度和快速测量能力。系统的测量速度主要受结构光编解码算法的实现方式影响。相比于 FPGA 平台,ZYNQ 平台开发难度较低,但基于 ZYNQ 平台的 Vitis HLS 技术在资源利用、时序性能和逻辑控制上逊色于 FPGA,导致测量速度略低。

而系统的测量精度受多种因素影响,主要包括相机分辨率、系统标定精度、结构光编解码算法以及三维重建算法等。首先是相机分辨率,本文采用的 CMOS 相机集成度较高,但分辨率较低,限制了标定、解码和重建的精度,采用更高分辨率的相机是提高测量精度的有效途径。为适应高分辨率成像设备,需进一步对系统的集成化设计进行优化,提升图像数据的传输与处理能力,以满足基于嵌入式平台的高速、高精度测量需求。此外,系统标定精度的优化依赖于标定算法的改进以及高精度成像设备和标定物的选择。最后,通过对结构光编解码和三维重建算法进

行流水线优化、循环展开优化以及数据流优化等 Vitis HLS 优化,可进一步提高系统的整体测量精度与效率。

## 4 结 论

本文设计了一种基于 ZYNQ 的单目面结构光三维测量系统,解决了目前基于嵌入式平台实现结构光三维测量普遍存在算法不完整和实现复杂的问题。利用 Vitis HLS 技术实现结构光三维测量算法大大降低了开发难度、缩短了开发周期。实验结果表明,系统能够实现从系统参数标定到三维重建的全流程三维测量。对复杂物体的测量结果反映出系统具有良好的鲁棒性,通过进行结构光三维测量实验表明系统测量精度达到亚毫米级,测量速度超越了传统基于 CPU 的 PC 平台,展现出系统的优秀性能。此外,ZYNQ 平台功耗仅为 2.696 W,满足嵌入式平台的低功耗要求。以上结果表明本文设计的系统具有算法实现完整、开发难度低、性能优越、低功耗的优点,能够满足基于嵌入式平台实现结构光三维测量的要求。然而,系统在精度和集成度方面仍有提升空间,未来可考虑使用更高分辨率的成像设备并研究系统的进一步集成化以及算法优化方法,最终将系统实际应用到工业检测等领域,以提高测量效率。

## 参考文献

- [1] HALEEM A, JAVAID M, SINGH R P, et al. Exploring the potential of 3D scanning in Industry 4.0: An overview [J]. International Journal of Cognitive Computing in Engineering, 2022, 3: 161-171.

- [2] MONTUSIEWICZ J, MIŁOSZ M, KESIK J, et al. Structured-light 3D scanning of exhibited historical clothing—A first-ever methodical trial and its results[J]. Heritage Science, 2021, 9(1): 74.

- [3] MAJOR M, MÉSZÁROS B, WÜRSCHING T, et al. Evaluation of a structured light scanner for 3D facial imaging: A comparative study with direct anthropometry[J]. Sensors, 2024, 24(16): 5286.

- [4] 张启灿, 吴周杰. 基于格雷码图案投影的结构光三维成像技术[J]. 红外与激光工程, 2020, 49(3): 78-90. ZHANG Q C, WU ZH J. Three-dimensional imaging technique based on Gray-coded structured illumination[J]. Infrared and Laser Engineering, 2020, 49(3): 78-90.

- [5] 左超, 张晓磊, 胡岩, 等. 3D 真的来了吗? —— 三维结构光传感器漫谈[J]. 红外与激光工程, 2020, 49(3): 9-53. ZUO CH, ZHANG X L, HU Y, et al. Is 3D really here? — A discussion on structured light 3D sensors[J]. Infrared and Laser Engineering, 2020, 49(3): 9-53.

- [6] JUNGER C, HESS A, ROSENBERGER M, et al.

- FPGA-accelerated phase rectification for a stereo-based phase measuring profilometry system [C]. Journal of Physics: Conference Series. IOP Publishing, 2018, 1065(3): 032017.

- [7] LYU C Y, LI P, WANG D CH, et al. High-speed optical 3D measurement sensor for industrial application [J]. IEEE Sensors Journal, 2020, 21(10): 11253-11261.

- [8] LIU D M, PAN Y F, LU R SH. FPGA-assisted high-precision, high-speed 3D shape measurement [J]. Sensors and Actuators A: Physical, 2020, 315: 112366.

- [9] CHEN ZH, HU T L, HAO Y Y, et al. High-speed phase structured light integrated architecture on FPGA [J]. IEEE Transactions on Industrial Electronics, 2023, 71(1): 1017-1027.

- [10] FENG SH, ZUO CH, ZHANG L, et al. Calibration of fringe projection profilometry: A comparative review [J]. Optics and Lasers in Engineering, 2021, 143: 106622.

- [11] MORENO D, TAUBIN G. Simple, accurate, and robust projector-camera calibration [C]. 2012 Second International Conference on 3D Imaging, Modeling, Processing, Visualization & Transmission. IEEE, 2012: 464-471.

- [12] 曹毅, 陈星飒, 吴翔, 等. 基于局部光栅补全的反光物体三维重建 [J]. 电子测量技术, 2023, 46(4): 91-98.

- CAO Y, CHEN X S, WU X, et al. 3D reconstruction of reflective objects based on local grating completion [J]. Electronic Measurement Technology, 2023, 46(4): 91-98.

- [13] 韩叔桓, 杨延西, 张新雨, 等. 互补格雷码双 N 步相移的彩色编码光栅投影轮廓术 [J]. 仪器仪表学报, 2023, 44(2): 42-49.

- HAN SH H, YANG Y X, ZHANG X Y, et al. Color coded grating projection complementary gray code double N-step phase shift profilometry [J]. Chinese Journal of Scientific Instrument, 2023, 44(2): 42-49.

- [14] ZHENG H, DUAN F J, LI T Y, et al. A stable, efficient, and high-precision non-coplanar calibration method: applied for multi-camera-based stereo vision measurements [J]. Sensors, 2023, 23(20): 8466.

- [15] KANAN C, COTTRELL G W. Color-to-grayscale: Does the method matter in image recognition? [J]. PloS One, 2012, 7(1): e29740.

- [16] SHAH A, BANGASH J I, KHAN A W, et al. Comparative analysis of median filter and its variants for removal of impulse noise from gray scale images [J]. Journal of King Saud University-Computer and Information Sciences, 2022, 34(3): 505-519.

- [17] CONG J, LAU J, LIU G, et al. FPGA HLS today: Successes, challenges, and opportunities [J]. ACM Transactions on Reconfigurable Technology and Systems (TRETS), 2022, 15(4): 1-42.

- [18] 刘端茂. 相位测量轮廓术算法 FPGA 加速技术研究 [D]. 合肥: 合肥工业大学, 2021.

- LIU D M. Research on FPGA acceleration technology for phase measurement profilometry algorithm [D]. Hefei: Hefei University of Technology, 2021.

- [19] HODSON T O. Root mean square error (RMSE) or mean absolute error (MAE): When to use them or not [J]. Geoscientific Model Development, 2022, 15(14): 5481-5487.

### 作者简介

万基茂, 硕士研究生, 主要研究方向光电视觉测量。

E-mail: wanjimao@bistu.edu.cn

张乾坤(通信作者), 博士, 副教授, 硕士生导师, 主要研究方向低维纳米电子、柔性电子器件、纳米光子学。

E-mail: qkzhang@bistu.edu.cn