# 1553B 总线仿真与测试的 PXIE 模块设计

李景晨 陈健 何理波

(上海大学特种光纤与光接入网重点实验室 上海 200444)

**摘要:** 针对于检验星上载荷单机的 1553B 接口功能是否正常的要求,提出一种基于 FPGA 的 3U PXIE 外设模块的软硬件设计方案。PXIE 控制模块可通过 PXIE 总线对 1553B 模块进行配置,并能控制与传输载荷 1553B 信号的仿真与测试数据。该设计完全模拟某卫星星务计算机 1553B 接口的真实电路以及电气特性,按需求实现了总线 BC,BM 功能,通过 B-6131 总线协议芯片,配置出上述功能的两路 1553B 总线接口线路,高度贴合实际应用场景。通过星载平台测试软件的操作,工作在 BC 模式下的一路 1553B 通道可进行自定义消息发送,也可以开启一段时间广播,长抱环测试等半自动化测试,实现自适应总线测试功能。所有出现在 1553B 总线上的消息都会被另一个工作在 BM 模式下的总线通道捕获到,从而实现所有总线数据的监视存储功能。

**关键词:** PXIE;1553B;总线协议仿真;可靠性

中图分类号: TN911 文献标识码: A 国家标准学科分类代码: 510.99

## Design of PXI Express module used for 1533B bus simulation and test

Li Jingchen Chen Jian He Libo

(Key Laboratory of Specialty Fiber and Optics Access Networks, Shanghai University, Shanghai 200444, China)

**Abstract:** To meet the requirement of testing whether the 1553B interface function of the single machine of the on-board payload is normal, a software and hardware design scheme of a 3U PXIE peripheral module based on FPGA is proposed. The PXIE control module can configure the 1553B module through the PXIE bus and control and transmit the simulation and test data of the 1553B signal of the payload. This design fully simulates the real circuit and electrical characteristics of the 1553B interface of a certain satellite's on-board computer, and realizes the BC and BM functions of the bus as required. Through the B-6131 bus protocol chip, two 1553B bus interface lines with the above functions are configured, which are highly consistent with the actual application scenarios. Through the operation of the on-board platform test software, one 1553B channel working in BC mode can send custom messages, and can also start a period of broadcasting, long loopback test and other semi-automated tests to achieve adaptive bus testing. All messages appearing on the 1553B bus will be captured by another bus channel working in BM mode, thereby realizing the monitoring and storage function of all bus data.

**Keywords:** PXIE;1553B;bus protocol emulation;reliability

## 0 引言

近些年,随着中国航天事业的蓬勃发展,技术的日益成熟,卫星的未来的发展趋势也会向小型化和低轨化靠近。这就会导致卫星的制造周期会大大缩短,发射需求不断增加。在面对总线接口功能各不相同的星上载荷单机时,便会有快速、高效、便捷的验证星务计算机和卫星载荷之间通信总线接口功能的需求。目前,国内航天器主要采用 1553B 总线进行通信<sup>[1]</sup>,因此采用 1553B 总线接口的星上载荷单机的数量会越来越多,为保证其在太空中能正常实

现总线接口功能,地面仿真测试这一环节是必不可少的。

而对于 1553B 总线通信设计的研究,目前主要集中应用在航空领域。如任勇峰等<sup>[2]</sup>在 2021 年提出的一款基于 DSP EMIF + LHB155304 的远程终端(remote terminal, RT)设计与实现中,仅仅是作为 RT 设备应用在大气传感器解算装置上,同样黄敬涛等<sup>[3]</sup>在 2015 年提出的某型红外探测系统中 1553B 总线通信设计与实现也是作为 RT 设备应用在飞控系统中。在航空领域上,刘佳昕等<sup>[4]</sup>提出的一种自适应 1553B 总线通信功能系统级测试方法设计仅是在软件层面上实现星上载荷单机的总线通信功能,无法满足

硬件上模拟星务计算机的要求。

本文设计是基于某卫星星务计算机总线功能仿真测试与验证项目。任务要求在硬件设计上完全符合真实的星务计算机 1553B 总线接口的电路设计以及电气要求。在软件上实现 1553B 总线的总线控制器(bus controller, BC)和总线监控器(bus monitor, BM)功能,完成对星上载荷单机 1553B 总线接口的自适应测试并实时记录下测试数据等功能。在测试操作方面要求实现通用化操作,便于携带测试设备,简化操作步骤。而根据上文所述,现阶段针对此要求以及功能的 1553B 仿真卡设备研究较少。

对此,本文提出了 1553B 总线仿真与测试的 PXIE 模块设计,通过此设计可以在硬件上符合某卫星星务计算机 1553B 总线接口电路状态以及电气特性,在软件上可以实现 1553B 总线的 BC 和 BM 功能,完成总线自适应测试以及总线数据监视功能。填补 1553B 总线在卫星载荷单机方向上仿真设计的不足,提高验证卫星载荷单机 1553B 总线通信功能的效率。通过星载平台软件界面完成对整体测试的控制与监测,采用的 PXIE 模块设计也便于测试人员操作和携带。

## 1 1533B PXIE 外设模块总体设计

1553B 总线接口板卡负责精确复现卫星通信链路中的 1553B 信号特性,实现对卫星关键 1553B 通信信号的深度捕获与精细化分析,使得研发团队能够在项目初期就针对 1553B 信号节点的功能性能进行仿真评估,并有效验证星载平台软件与负载软件之间的 1553B 信号互操作性。

在设计方案上相较于采用单独机箱堆叠方式实现 1553B 总线仿真与测试功能的测试仪器,采用 PXIE 体系构建测试仪器的方式节约了设计成本,简化了仪器接口冗余度,更有利于集成与维护,对于硬件的更新升级也节约了成本<sup>[5-7]</sup>。其采用 PCI Express 串行通信接口进行数据交互,这比传统的 PXI 使用的并行总线技术提供了更高的数据传输速率和更大的带宽,能够更好地提高系统的稳定性,支持大数据量的传输,更加切合星务计算机在实际应用上的场景。

目前实现 1553B 总线协议的方案总体上分为两类,第一是使用 FPGA 编写 1553B 总线协议来实现 1553B 的 BC、RT、BM 等功能<sup>[8]</sup>;第二是使用专用的 1553B 总线协议芯片来实现远程终端和总线控制器等功能。相较于前一种方式,后一种方式更有利于缩短开发周期,提高产品可靠性。经过调研发现,北京微电子所在国内对于 1533B 总线协议芯片的研发已经相当成熟,在 2023 年前已经研发了 4 代 1553B 总线系列产品。其中第 1 代 1553B 总线控制器(B61580S3)采用多芯片二次集成设计,5 V 供电,内部集成 4 K×16 bit 静态存储器;第 2 代(B64843、B64703)等芯片相较与上一代产品,采用 3.3 V 供电在完整的继承上一代芯片功能的基础上实现了芯片体积减小 1/2,重量减小 2/3

的突破;第 3 代(B64843NBC)则在其芯片内部集成了数字协议电路和模拟收发器等模块;第 4 代高集成度 1553B 总线(B6131)属于高集成的 1553B 总线协议芯片,将数字协议电路、模拟收发器单片集成,可以在配置实现 BC、RT 和 BM 功能的同时还可以完成双 RT 热备份<sup>[9-10]</sup>。根据目前选择的 3U PXIE 体系架构的方案以及研发周期考虑,最终选择第 4 代高集成 1553B 总线协议芯片,在节约了硬件布局面积的基础上还集成了上述各类模块功能。考虑到控制 1553B 协议芯片需要 SPI 控制器,加上采用 PXIE 体系架构需要 PCIe 控制器,所以采用 Xilinx ZYNQ 系列芯片作为此 PXIE 外设模块的总控制器,该系列芯片不仅在 PS 端集成各类接口控制器,如 I2C、SPI、CAN 等,而且还拥有 PCIe 内核的集成模块,这种全集成的设计方式,简化了硬件设计,便于软件编程,降低了设计成本。

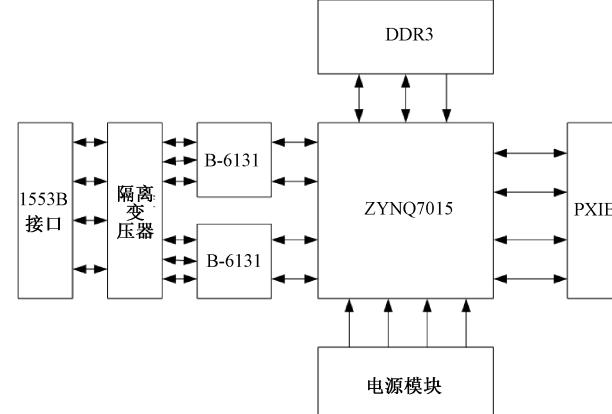

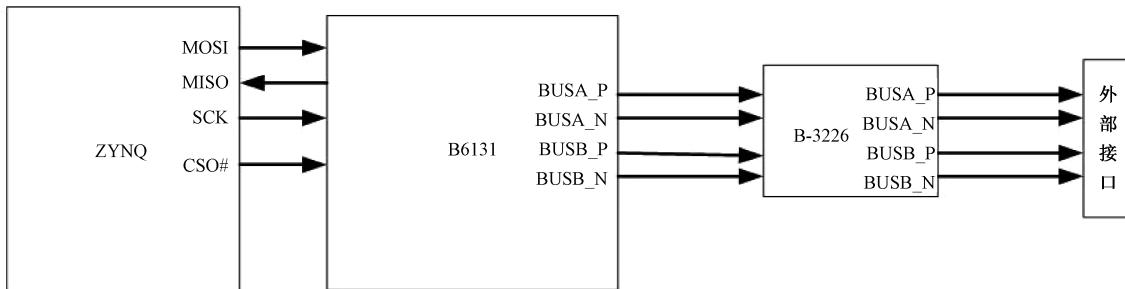

图 1 所示为 1553B 总线接口板卡的硬件设计框图。

图 1 硬件设计框图

Fig. 1 Hardware design diagram

从图 1 可以看出 1553B 总线接口板卡集成了电源模块、DDR3 存储模块、PXIE 通信接口及 1553B 接口模块。板卡供电由 PXIE 插槽输入的 12 V 电压提供,再经过电源保护电路,滤波电路和电压管理芯片后,输出板卡各个模块所需要的工作电压。FPGA 外接 1 Gbit 大小的 DDR3 存储器,用来对 1553B 总线上传输数据的存储。在大数据,长时间工作时起到缓冲数据作用,也可以通过特定开辟的地址空间起到与星载平台软件进行人机交互的操作,同时连接一个 QSPI FLASH 芯片用于板卡程序的烧录与启动。FPGA 的 PL 端高速串行收发器用于构成 PXIE 通信模块,1553B 通信采集数据经机箱背板传输至 PXIE 主控器,再由运行在 Windows 系统上 C# 编写的星载测试平台软件显示。

1553B 接口模块选用专用协议芯片 B-6131,将此芯片的通信控制引脚信号连接到 FPGA 的 PS 端,通过 PS 端集成的 SPI 控制器对 B-6131 进行读写控制操作,从而输入或输出 1553B 信号,这些信号经过 B-3226 变压器耦合隔离,保护被测星载单机电路。

## 2 1533B PXIE 外设模块硬件设计

### 2.1 电源模块

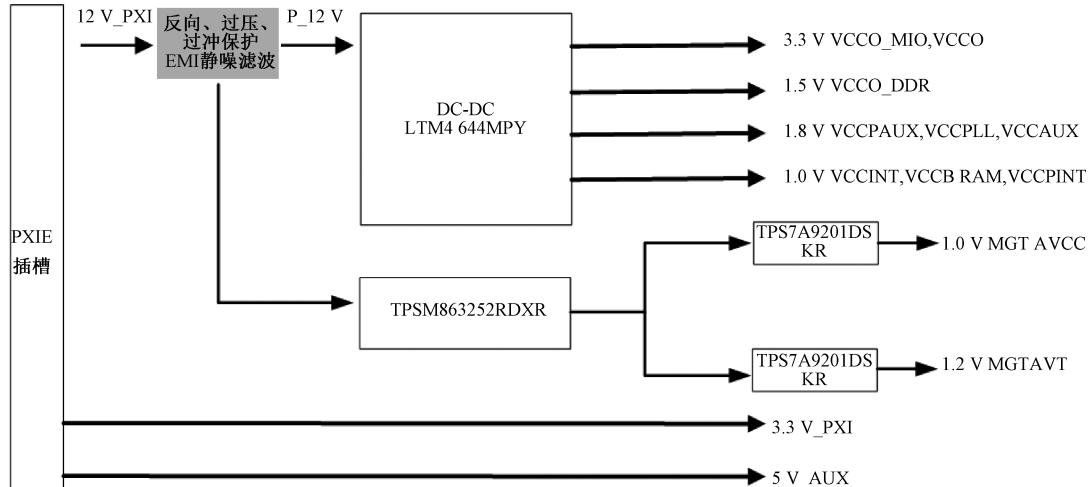

此板卡的供电来自于 3U PXIE 机箱背板的 12 V 电源, 板卡上需要的各种电压如图 2 的电源树所示。

根据 PXIE 协议, 背板通过 XJ4 连接器, 提供 12 V 以及 3.3 V 三种电源。其中 5 V 用于 PXIE 热插拔等相关信号, 而 3.3 V 电源最高提供电流 9 A, 12 V 电压最高提供电流 6 A。本板卡所需功率经测算估计在 30 W 左右, 因此采用 PXIE 背板插座提供的 12 V 作为输入电源。该 12 V 电源经过一个由 TPS259541DSG 芯片构成的滤波, 保护电路后, 输入到 LTM4644 MPY 芯片, 此芯片支持 4~14 V 电

图 2 电源分配图

Fig. 2 Power distribution diagram

而 PS 端上电顺序为:

VCCPINT(1.0 V)→VCCPAUX, VCCPLL(1.8 V)→VCCO\_DDR(1.5 V)、VCCO\_MIO(1.8 V, 3.3 V)

通过 DC-DC 和 LDO 芯片的 EN 使能和 PG 电源正常引脚的适当连接可以实现 PS 和 PL 端的上电顺序。

### 2.2 DDR3 存储模块

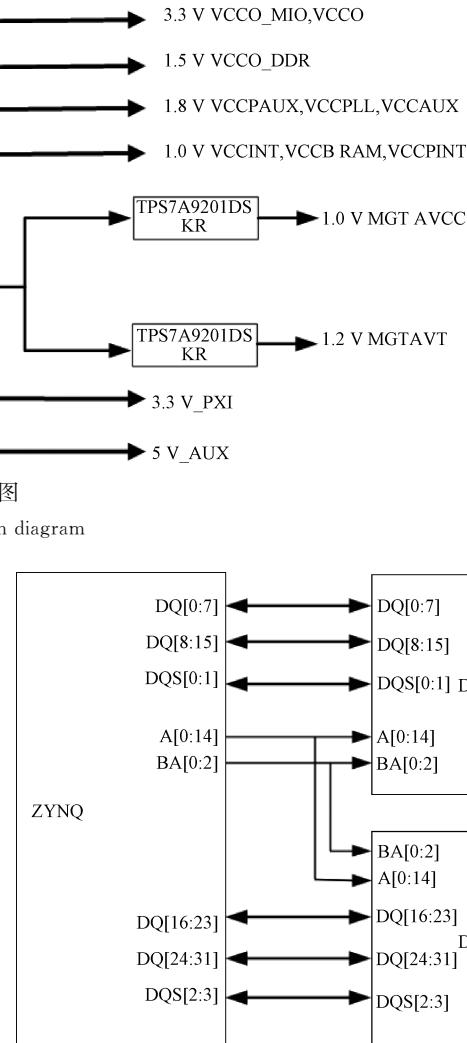

ZYNQ-7015 芯片外接型号为 IS43TR16256BL-125KBLI 的 DDR3 内存颗粒芯片, 该芯片为 ISSI 公司制造, 容量大小为 256 M, 数据位宽为 16 位, 单片 DDR3 芯片大小为 4 Gb, 根据板卡需求, 安装两片, 使得数据位宽变为 32 位, 存储容量大小为 8 Gb<sup>[11]</sup>。ZYNQ 与传统 FPGA 并不相同, DDR 专门连接到 PS 端的 Bank502, 如图 3 所示。

BA[0:1]信号为两个芯片的公共信号线, 决定数据将在哪个 bank 进行读写操作。DQ[0:31]为两个 DDR 的数据总线, DQS[0:3]为数据选通信号线, 实现了 32 位数据位宽的存储方式。为保证 1 333 Mbps 的读写信号质量, 需要在绘制 PCB 时设置相应的阻抗要求, 每组数据总线内部走线长度误差不超过 20 mil, 对于差分信号线, 要求差分阻抗为 85 Ω, 差分线对内长度误差小于 5 mil。对 4 组数据总线

压输入, 最高可提供 4 个 4 A 电流输出的 DC-DC 降压通道。由图 2 可知 12 V 经过降压得到 3.3、1.5、1.8 和 1.0 V 等直流电压, 为板卡上的各个主要芯片, 如 ZYNQ-7015、B-6131 和 DDR3 等芯片提供相应工作电压。此外, 由于 FPGA 高速串行收发器供电需要 1.2 V 和 1 V 等电压, 由 12 V\_PXI 单独经过 DC-DC 芯片 TPSM863252RDXR 获得 1.4 V 电压, 再由 LDO 芯片 TPS7A9201DSKR 降压得到较小纹波的 FPGA 串行收发器用电压。此外, 还要按照 ZYNQ 硬件手册要求设计上电时序, 以达到最小的系统上电浪涌规定, 其 PL 端上电顺序为:

VCCINT, VCCBRAM, VMGTAVCC (1.0 V) → VMGTAVT (1.2 V) → VCCAUX(1.8 V)、VCCO(1.8 V, 3.3 V)

图 3 DDR 连接图

Fig. 3 DDR connection diagram

长度误差要保证在 1 inch 以内。

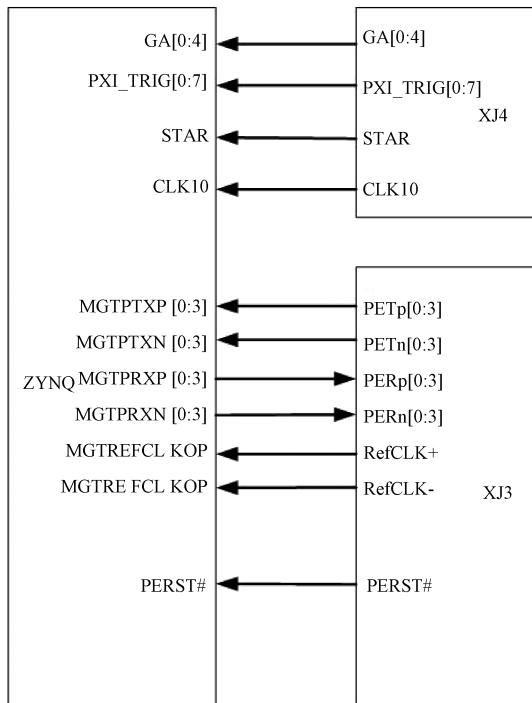

### 2.3 PXIE 通信接口模块

根据 PXIE 协议规定, 3U 外设板卡有 XJ3 和 XJ4 两个连接器用于 PXIE 板卡与 PXIE 背板之间的连接, 如图 4 所示。

图 4 PXIE 外设板卡信号

Fig. 4 PXIE peripheral board signal diagram

图 5 1553B 接口电路

Fig. 5 1553B interface circuit

外提供两路 1553B 接口,两块 B-6131 芯片均采用 SPI 接口与 ZYNQ 通信。由于 ZYNQ 的 PS 端已经集成了 SPI 硬件控制器,所以将两路 SPI 信号共用一个 SPI 控制器,通过 CS 片选信号分别对两路 1553B 总线芯片进行选通配置。

考虑到在 PS 端进行配置,所以将 B-6131 其余信号接入 PS 端的 MIO 脚上便于后续程序编写。由于 1553B 输出的 BUSA 和 BUSB 信号可能会达到 12~27 V,所以需要采取航天总线专用隔离变压器 B-3226,对整个接口电路进行隔离保护,减少高压信号对设备造成的故障。1553B 对外耦合方式分为两种,一种是直接耦合连接,另一种为变压器耦合连接,考虑到 1553B 整体线路连接安全性,采用变压器耦合方式与外部 RT 设备连接,所以要在总线 A、B 接口的差分管脚中并联一个  $70\Omega$  负载。

### 3 1533B PXIE 外设模块软件设计

考虑到软件功能主要包含配置 1553B 消息帧、发送各

其中,XJ3 连接器主要用于 PCIe 高速数据传输以及时钟同步信号传输,而 XJ4 则是用于提供板卡工作电压以及一些 PCIe 机箱所需要用到的仪器信号。

在外设模块中主要用到的信号有 1PETp[0:3]、1PETn[0:3]、1PERp[0:3]、1PERn[0:3]、1RefCLK+、1RefCLK-、PERST# 等,这些信号为高速数据传输所必备的信号,其中 PET 和 PER 信号用于接收和发送高速串行数据传输,采用差分信号线模式,用于提高数据传输的稳定性,减少信号串扰影响。RefCLK 信号为高速数据传输的同步时钟,同样采用差分信号线。此外对于 PET 和 RefCLK 信号这些从发送端输出的信号,需要在发送端串联  $0.1\mu F$  电容实现信号交流耦合,提高信号质量。为进一步提高上述高速差分信号的信号质量,需要在 PCB 绘制时实现阻抗匹配,对于差分对内的 P/N 线的长度要求也要严格控制在 3 mil 以内。注意,PCIe 的差分线对间没有规定等长要求,一般不会超出 1 英尺。

#### 2.4 1553B 接口模块

为了最真实地模拟星务计算机 1553B 接口电路的物理层特征,本研究采用 B-6131 芯片,此芯片为 1553B 总线专用芯片,可以配置 BC、BM 和 RT 三种模式,可满足总线仿真与测试的所有要求,如图 5 所示,本 PXIE 外设模块对

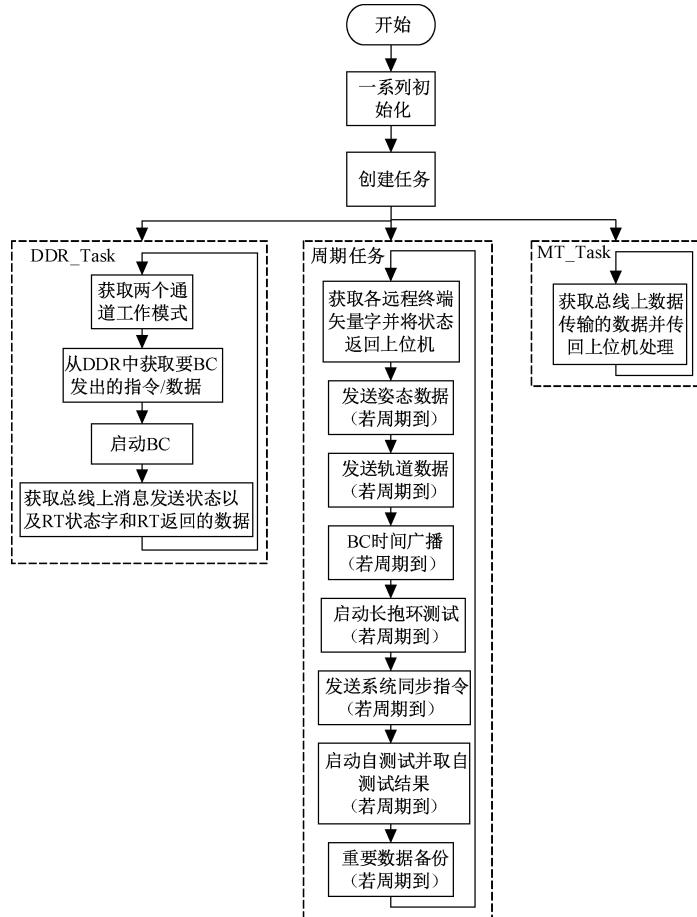

类周期消息广播以及 MT 监视总线数据等 3 类并发任务,单纯在 ZYNQ 中的 ARM A9 硬处理器中裸机开发程序会增加软件复杂度,且有多任务调度困难等缺点,因此需要采用 RTOS。相较于其他 RTOS,FreeRTOS 系统作为开源的轻量级实时系统,有着很好的移植性和丰富的 API 函数,其支持的多任务调度的能力满足本设备在设计使用过程中所需要的调试以及测试功能<sup>[12]</sup>。目前根据需求,设置了 3 个任务,分别为 DDR\_TASK、周期任务和 BM\_TASK。

如图 6 所示,ZYNQ-7015 的 PS 端通过内部集成的 SPI 控制器对 1553B 协议芯片 B-6131 进行控制。

##### 1) DDR\_TASK

该任务负责本设备与星载平台软件的联调,使得测试人员可以在 BC 模式下单独地配置和发送 1553B 消息。测试人员在星载平台软件进行相关操作后,关于 1553B 消息的相关配置内容,如状态字,返回数据等将会被存入 DDR3 中的相应自定义地址中。DDR\_TASK 在检测到所

配置消息完成的 FLAG 标识后,开始提取相应地址内的数据,并通过 SPI 接口对 B-6131 发布指令,对系统界面需

要发送的消息进行配置,最后启动 BC 完成 1553B 消息帧的发送。

图 6 软件设计总体框图

Fig. 6 Block diagram of software design

## 2) 周期任务

该任务负责星务计算机被测单机长期可持续测试用的相应周期任务,完成对星上载荷单机的自适应测试。开启任务后,系统将会经 1553B 总线轮流向各个测试单机发送矢量字,通过单机返回的矢量字和状态来判断被测试单机是否有服务请求。同时,根据测试单机相应要求,设置了姿态广播、轨道广播以及时间广播,此 3 个广播通过调用 FreeRTOS 内部定时器,周期性对各个单机进行广播发送相关卫星姿态,轨道数据以及时间信息。为保证各个单机发送数据的可靠性和稳定性,需获取各被测单机的故障信息,在该任务中设置 3 个定时器,分别用于自测试、长抱环测试和系统同步指令。其中自测试是星务计算机对被测单机发送自测试指令后,被测单机接收指令后完成单机内部测试并返回自测试状态数据供星务计算机查看被测单机自测试完成情况。长抱环测试是由本设备对总线控制器的 A、B 通道周期性发送测试数据字,被测单机在接收到数据后再取反返回给总线控制器。总线控制器将发送和接收的数据字进行比较,如果相符,则判定该次测试成

功。否则判定该次测试失败,并采取相应的故障处理措施。系统同步是星务计算机作为总线控制器在每个总线通讯周期根据各远程终端的需求,安排数据传输,同时周期性地提供系统同步消息。

## 3) BM\_TASK.

该任务为该设备第 2 个 1553B 通道设置的 BM 模式。第 2 个 1553B 通道中的 B-6131 在上电时便会被设置为 BM 模式。在该模式下,将 BC 模式下的通道一和通道二连接到外部同一耦合线路中,在开启 BM 模式后便会检测到 1553B 线路上的所有消息内容,并储存到相应 DDR 地址中。星载平台软件在开启通道 BM 模式后便会将相应 1553B 总线消息数据从 DDR 中取出,最终通过 PCIe 传输到星载平台软件显示出来。

## 4 板卡的可靠性测试

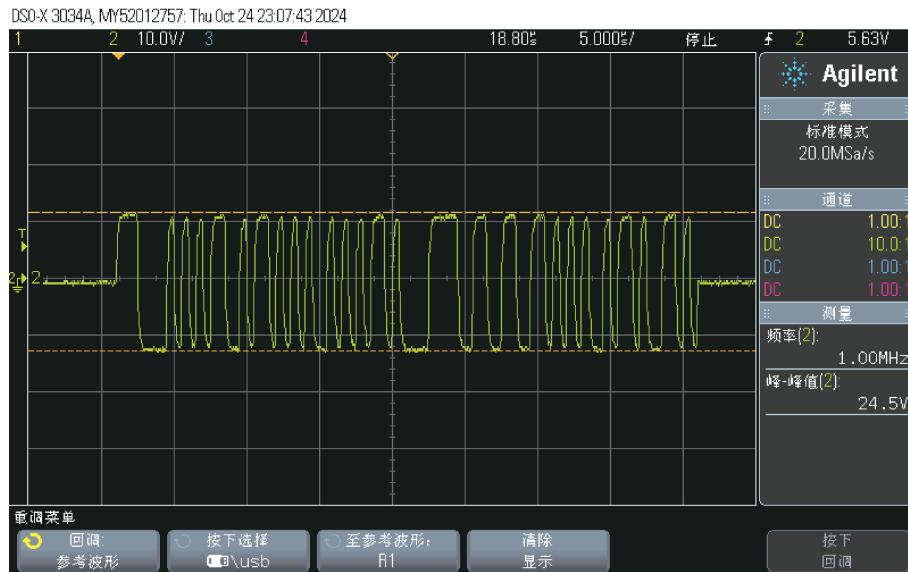

### 4.1 1553B 消息传输电平测试

为验证本设计 1553B 接口输出电平符合总线协议要求,使用示波器对 1553B 的 BUS 接口 PN 引脚进行电平检

测,测试结果图如图 7 所示。

由测试结果图可知,1553B 总线速率稳定在 1 Mbps,符合软件设置结果。其 BUS 差分对之间的电平在

24.5 V,其结果在 B-6131 数据手册规定的输出电平差 12~27 V 之间,所以 1553B 接口电路在物理层上的消息传输是可靠稳定的。

图 7 1533B 消息电平测试图

Fig. 7 1533B message level test diagram

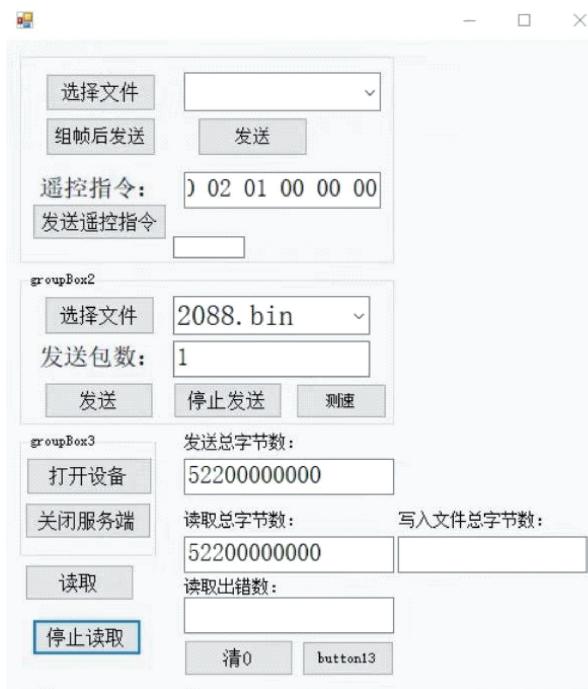

## 4.2 PCIe 数据传输性能测试

本设计采用 XDMA(DMA/Bridge Subsystem for PCI Express)实现 PCIe 数据传输及与系统界面的交互操作。该 IP 相较于 Xilinx 提供的其他两个 PCIe IP 核,不仅实现了 PCIe 协议的物理层、数据链路层和事务层功能,而且实现了一个高性能、可配置的分散聚集式 DMA<sup>[13-14]</sup>引擎。由于本设计需要对 DDR 缓存的数据进行传输。所以将 XDMA 配置为 AXI4 接口的 DMA 传输,它保证了大规模高速数据传输的可靠性。如图 8 所示,测试人员在星载平台软件配置一条消息大小为 2 088 字节的消息帧,先通过 XDMA 直接对 DDR 进行数据写入,然后将该测试数据读回,通过比较数据测试 PCIe 数据传输过程的准确性与可靠性。

连续写入和读回 2 088 字节数据帧 25 000 000 次,总数据量约为 48.6 GB 大小,发送与读取数据相符,传输的误码数量为 0,充分验证了所设计的 PCIe 数据传输的软、硬件可靠性。

## 4.3 1553B 接口数据传输性能测试

为了检验被设备的长时间可靠运行情况,本研究对设备进行长时间大数据的测试,如图 9 所示。

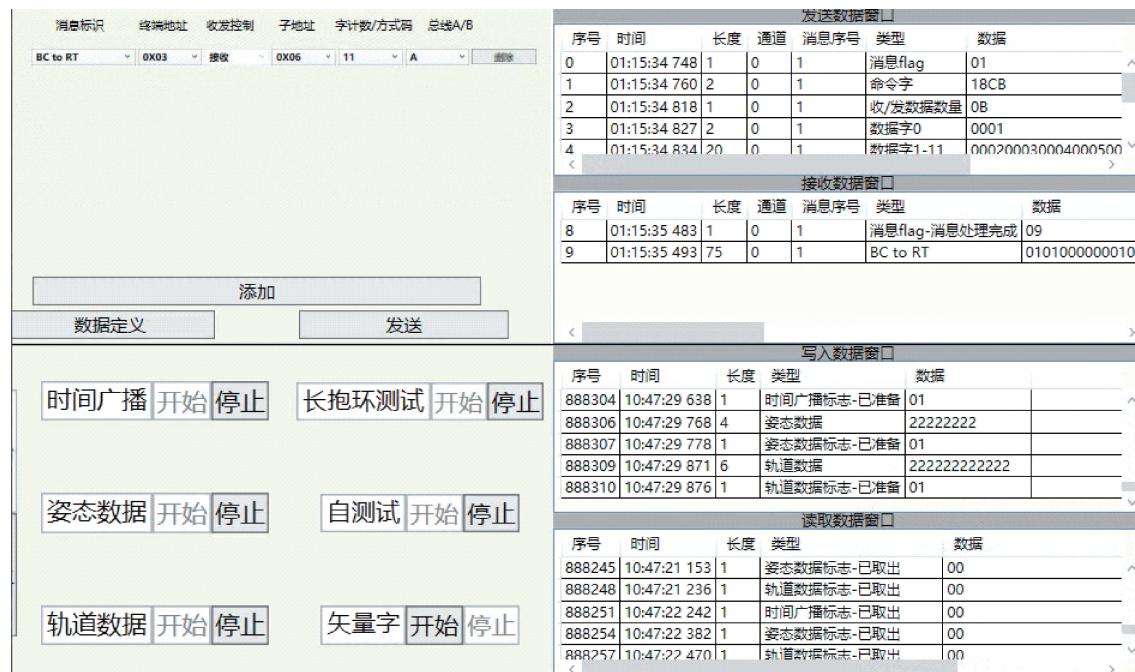

首先在星载平台软件界面打开 BC 模式,在 1553B 消息配置界面对要发送的消息进行配置如消息标识,终端地址等内容。在点击发送后,右侧星载平台软件界面显示发送的 1553B 消息的相关信息,其中包括数据字以及自定义的 Flag 标识用于判断配置是否完成。该星载平台软件可以支持添加配置多条消息内容来满足测试人员相关测试

图 8 PCIe 回环测试

Fig. 8 PCIe loopback test

需求,实现自动化测试。

在该界面左下方是相关周期消息的测试,测试人员点击开始后,该设备可同时发起姿态广播、轨道广播、时间广播、自测试、长抱环测试和矢量字等相应周期消息,在界面右下方区域可显示发送和接受的相关 RT 消息信息,经测

试该设备可保持一周 24 h, 每秒一次的不间断测试, 支持长时间的 1553B 接口性能测试。

界面系统的 BM 功能可以刷新 1553B 总线上的数

图 9 1553B 接口测试界面

Fig. 9 1553B interface testing interface

## 5 结 论

本文描述了一个基于 PXIE 协议的 1533B 总线外设模块的软、硬件设计。该 PXIE 外设模块拥有两路 1553B 接口, 分别拥有 A、B 两条总线, 实现了 1553B 协议中的 BC 和 BM 功能。为保证此设计的灵活性与可靠性, 硬件上采用 ZYNQ 芯片 PS 端控制 1553B 专用协议芯片, 并利用航天总线专用变压器进行设备隔离。在软件上采用 Xilinx 成熟的 XDMA IP 核的方式实现了主机与 PXIE 外设模块之间的高速数据传输。采用 FreeRTOS 操作系统保证了 1553B 总线消息调试, 周期消息广播和故障排除等星上载荷的测试任务, 用户可以根据实际需求, 配置相关测试方案, 为星上载荷测试基于 1553B 协议的通信功能提供了稳定可靠的测试设备。

## 参考文献

- [1] 朱晓辉, 吕德东, 张阁. 基于分级处理的星载数据总线综合测试方法[J]. 航天器工程, 2015, 24(5): 137-143.

- ZHU X H, LYU D D, ZHANG G. A method of integrated test for on-board data bus based on leveled data processing[J]. Spacecraft Engineering, 2015, 24 (5): 137-143.

- [2] 任勇峰, 吕文强, 关瑞云, 等. 基于 DSP EMIF + LHB155304 的 RT 终端设计与实现[J]. 电子测量技

- 据, 显示数据传输时间、消息类型、传输总线等内容<sup>[15]</sup>, 并将这些消息数据保存在本地硬盘中, 供测试人员回溯查看。

- 术, 2021, 44(3): 165-169.

- REN Y F, LYU W Q, GUAN R Y, et al. Design and implementation of RT terminal based on DSP EMIF + LHB155304[J]. Electronic Measurement Technology, 2021, 44(3): 165-169.

- [3] 黄敬涛, 李丙玉, 王晓东, 等. 某型红外探测系统中 1553B 总线通信设计与实现[J]. 电子测量技术, 2015, 38(9): 143-146.

- HUANG J T, LI B Y, WANG X D, et al. Design and realization of 1553B bus communication in an infrared detection system[J]. Electronic Measurement Technology, 2015, 38(9): 143-146.

- [4] 刘佳昕, 赵欣博, 高洪宇, 等. 自适应 1553B 总线通信功能系统级测试方法设计[J]. 遥测遥控, 2022, 43 (3): 37-43.

- LIU J X, ZHAO X B, GAO H Y, et al. Testing method research based on communication of self-adaptive 1553B bus [J]. Telemetry and Remote Control, 2022, 43(3): 37-43.

- [5] 郭楹, 张奇荣, 熊开利, 等. 一种单片 1553RT、BM、BC 接口芯片的设计[J]. 集成电路应用, 2022, 39 (10): 17-19.

- GUO Y, ZHANG Q R, XIONG K L, et al. Design of a single-chip 1553B RT, MT, BC interface [J].

- Integrated Circuit Applications, 2022, 39 (10): 17-19.

- [6] 卢俊杰, 罗哉, 郑永军, 等. 基于 PXIE 的 EPS 试验台多通道数据采集系统设计[J]. 仪表技术与传感器, 2022(9): 57-61.

LU J J, LUO Z, ZHENG Y J, et al. Design of multi channel data acquisition system for EPS test bench based on PXIE [J]. Instrument Technology and Sensors, 2022(9): 57-61.

- [7] 黄燕, 黄光明. 基于 PXIE 高速 DAQ 性能提升的关键技术研究[J]. 电子测量技术, 2019, 42(2): 130-134.

HUANG Y, HUANG G M. Research on key technologies to improve the performance of high-speed DAQ based on PXIE [J]. Electronic Measurement Technology, 2019, 42(2): 130-134.

- [8] 陈秉军, 张贺, 王子君, 等. 基于 FPGA 的终端一体化 1553B 总线协议测试系统[J]. 海军航空工程学院学报, 2024, 39(3): 389-394.

CHEN B J, ZHANG H, WANG Z J, et al. Terminal integration 1553B bus protocol test system based on FPGA [J]. Journal of Naval Aviation Engineering College, 2024, 39(3): 389-394.

- [9] 王越涛, 赵冬青, 武慧军. 基于 FPGA 和 B61580S3 的 1553B 总线 RT/MT 功能的设计与验证[J]. 电子设计工程, 2023, 31(2): 179-183.

WANG Y T, ZHAO D Q, WU H J. Design and verification of 1553B bus RT/MT function based on FPGA and B61580S3 [J]. Electronic Design Engineering, 2023, 31(2): 179-183.

- [10] 付存文, 张震. 基于 PXIE 总线的中频采集模块设计[J]. 电子制作, 2024, 32(11): 3-5.

FU C W, ZHANG ZH. design of intermediate frequency acquisition module based on PXIE bus [J]. Electronic Manufacturing, 2024, 32(11): 3-5.

- [11] 旷立强. 基于 FPGA 的 DDR3 设计与实现[D]. 长沙: 国防科学技术大学, 2014.

KUANG L Q. DDR3 design and implementation based on FPGA [D]. Changsha: National University of Defense Technology, 2014.

- [12] 易文博, 陈国平, 管春. FreeRTOS 在 ZYNQ 实时液晶显示系统中的应用[J]. 现代电子技术, 2020, 43(22): 15-18, 22.

YI W B, CHEN G P, GUAN CH. Application of FreeRTOS in real-time LCD system based on ZYNQ [J]. Modern Electronic Technology, 2020, 43(22): 15-18, 22.

- [13] 高伟. 基于 PCIe 的 SpaceFibre 测试系统的研究与实现[D]. 北京: 中国科学院大学, 2021.

GAO W. Research and implementation of SpaceFibre test system based on PCIe [D]. Beijing: University of Chinese Academy of Sciences, 2021.

- [14] 金璐. 基于 ZYNQ 平台的 XDMA IP 核性能研究[J]. 科技资讯, 2023, 21(4): 15-18.

JIN L. Research on the performance of XDMA IP cores based on the ZYNQ platform [J]. Science and Technology Information, 2023, 21(4): 15-18.

- [15] 陆园, 马俊韬. 基于 DSP320F28335 实现 1553B 总线 MT 模式的技术研究[C]. 2015 第二届中国航空科学技术大会论文集, 2015: 636-639.

LU Y, MA J T. Technology research on 1553B bus of MT mode based on DSP320F28335 [C]. 2015 Second China Aviation Science and Technology Conference Proceedings, 2015: 636-639.

### 作者简介

李景晨(通信作者), 硕士研究生, 主要研究方向为高速硬件电路设计和嵌入式软件设计等。

E-mail: 1971751793@qq.com

陈健, 研究员, 主要研究方向为高速硬件电路设计。

E-mail: chenjian@shu.edu.cn

何理波, 硕士研究生, 主要研究方向为嵌入式系统技术、高速通信测试。

E-mail: helibo@shu.edu.cn