DOI:10.19651/j.cnki.emt.2416967

# 卫星高性能存储数传一体化系统关键技术及应用

朱彦铭 刘文重 吕雨桦 张俊杰 张倩武

(上海大学特种光纤与光接入网重点实验室 上海 200444)

**摘要:** 随着我国遥感卫星技术的迅速发展,执行的空间任务日益复杂,传统星载存储与数传系统面临高度定制化和高昂移植成本的挑战。本研究旨在开发一种高性能存储数传一体化系统,以解决这些问题。基于现场可编程逻辑门阵列(FPGA)的高灵活性,该系统设计了 SATA III 固态硬盘的读写访问及文件系统、带有数据合路控制的多通道 DDR 控制器和支持中频调制的数传功能。在设备和软件搭载数量最少的情况下,该系统实现了 900 Mbit/s 的最高数传下行带宽和最丰富的数传功能。该系统成功应用于吉天星某型号任务中,地面测试表明载荷存盘链路带宽长期稳定在 2.8 Gbit/s 以上,峰值带宽达到 3.69 Gbit/s,存储和数传业务均实现长期零误码运行;在轨验证证实了载荷图像下传清晰完整。该系统充分满足遥感卫星对稳定性和可靠性的严格要求,在遥感卫星领域具有重要的应用价值。

**关键词:** 遥感卫星;星载系统;FPGA;存储数传一体化

中图分类号: TN927 文献标识码: A 国家标准学科分类代码: 510.5015

## Key technologies and applications of integrated high-performance storage and data transmission system for satellites

Zhu Yanming Liu Wenzhong Lyu Yuhua Zhang Junjie Zhang Qianwu

(Key Laboratory of Specialty Fiber and Optics Access Networks, Shanghai University, Shanghai 200444, China)

**Abstract:** With the rapid advancement of remote sensing satellite technology in China, space missions are becoming increasingly complex, posing challenges to traditional spaceborne storage and data transmission systems in terms of high customization and costly migration. This study aims to develop an integrated high-performance storage and data transmission system to address these issues. Leveraging the high flexibility of field-programmable gate arrays (FPGAs), the system design incorporates SATA III solid-state drive read/write access with a file system, multi-channel DDR controllers with data multiplexing control, and data transmission functionality supporting intermediate frequency modulation. With minimal device and software deployment, the system achieves a maximum downlink bandwidth of 900 Megabits per second and offers the most diverse data transmission capabilities. The system has been successfully implemented in a specific Jitian satellite model mission. Ground tests demonstrate that the payload storage link bandwidth remains consistently stable above 2.8 Gigabits per second, with peak bandwidth reaching 3.69 Gigabits per second. Both storage and data transmission operations achieve long-term zero-error code performance. On-orbit verification confirms clear and complete transmission of payload images. The system fully meets the stringent stability and reliability requirements of remote sensing satellites, demonstrating significant application value in the field of remote sensing satellite technology.

**Keywords:** remote sensing satellite; spaceborne system; FPGA; integrated storage and data transmission

## 0 引言

现代遥感技术起源于 20 世纪 60 年代,以数字化成像为核心特征,是衡量国家科技发展水平的重要标志<sup>[1]</sup>。经过半个多世纪的发展,空间任务和载荷类型日益复杂多样,遥感卫星的设计理念已转变为以载荷为中心的整星一体化

联合优化方式<sup>[2-4]</sup>。另一方面,当前遥感卫星任务呈现出载荷多样化、协议多样化、速率多样化等航天业务需求,这使得单一系统难以有效复用<sup>[5-6]</sup>。如何在短时间内快速实现星载存储与数传系统,成为我国遥感卫星领域亟待解决的关键难题。

现有星载系统中,文献[7]提出的星载多通道图像采集

与处理系统,基于 FPGA 和片外双倍速率同步动态随机存储器(double data rate synchronous dynamic random-access memory,DDR)实现多通道 TLK2711 载荷顺序缓存,并通过 aurora 总线转发缓存数据。系统采用 5 片 DDR 并行接收采集数据。尽管该设计避免了多通道数据同时访问 DDR 造成的冲突问题,并易于完成数据合路控制,但是 5 片 DDR 所包含的物理引脚占用了过多的 FPGA I/O 资源,并且该合路控制算法要求各载荷传输对齐且数据帧长度一致,该 DDR 控制设计和合路控制算法面临通用性的挑战。

文献[8]在北京三号 A/B 卫星中设计了卫星数传智能处理器,以总线路由的方式将多通道载荷灵活路由至固存单元或数传单元,实现载荷存盘带宽 9.3 Gbit/s,数传下行带宽 450 Mbit/s。该系统由 11 台设备组成,共装载 17 个软件,但系统复杂度和成本成为制约该系统广泛应用的瓶颈。

文献[5]提出了一种通用化星载存储系统架构,采用模块化理念集成中央处理器(central processing unit,CPU)通信板、FPGA 主系统和数传分系统,降低了设计复杂度。该系统存储业务依赖 CPU 通信板实现存储介质的读写指令调度和地址管理;数传业务考虑到数字上变频工作受限于 FPGA 工作时钟频率,未能通过 FPGA 实现脉冲成型、中频调制等工作。该架构未考虑采用 FPGA 解决这些业务设计上的难点,在降低系统复杂度方面仍有改进空间。

针对上述问题,本文提出了一种星载高性能存储数传一体化系统,将传统设计中需要多设备、多软件实现的功能整合于单一 FPGA 平台。该系统以纯逻辑实现的方式完成了串行 ATA(serial ATA,SATA)接口固态硬盘的读写访问、地址管理和指令调度,链路峰值带宽可达 3.69 Gbit/s;引入了 DDR 多通道控制器,实现了仲裁分发功能并在数据写入和数据读出 DDR 的过程中设计了新的数据合路算法,节省了片上缓存资源的开销,该控制器带宽高达 48.1 Gbit/s;基于国际空间数据系统咨询委员会(consultative committee for space data systems,CCSDS)制定的高级在轨系统建议书<sup>[8]</sup>(advanced orbiting systems,AOS)在传统设计基础上<sup>[3,7]</sup>增加了脉冲成型、滤波器矩阵等设计,并设计了一种中频等效载波生成算法实现了中频载波调制。该系统已成功搭载于吉天星某型号任务中,通过了在轨验证,为未来类似任务选用本系统提供可靠支撑。

## 1 总体方案设计

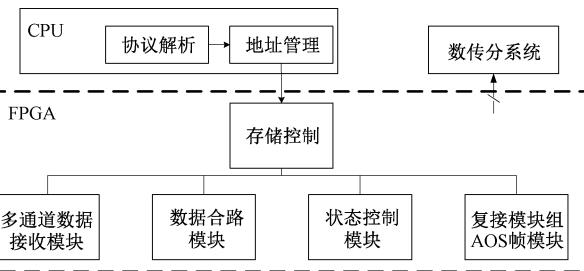

通用化星载存储系统架构<sup>[5]</sup>如图 1 所示,系统由 3 台设备组成,其中 FPGA 实现了 5 个功能:存储控制、多通道数据接收、数据合路、状态控制以及复接和 AOS 帧组装。系统要求高兼容性,具体表现为通过架构内 CPU 核心板对任务指令进行协议解析,以地址管理的方式控制 FPGA 中存储控制模块,从而实现对多种类载荷数据的并行存储支持。

图 1 通用化星载存储系统架构框图

Fig. 1 Block diagram of generalized on-board storage system architecture

数传功能设计方面,FPGA 实现 AOS 帧的组装,复接模块完成虚拟信道标识符的配置,随后按照正交相移键控(quadrature phase shift keying,QPSK)调制格式划分 I、Q 路符号数据。后续其他信号处理由数传分系统完成。该系统的性能指标包括:单载荷最大处理速率为 1.6 Gbit/s,存储链路带宽为 4 Gbit/s。

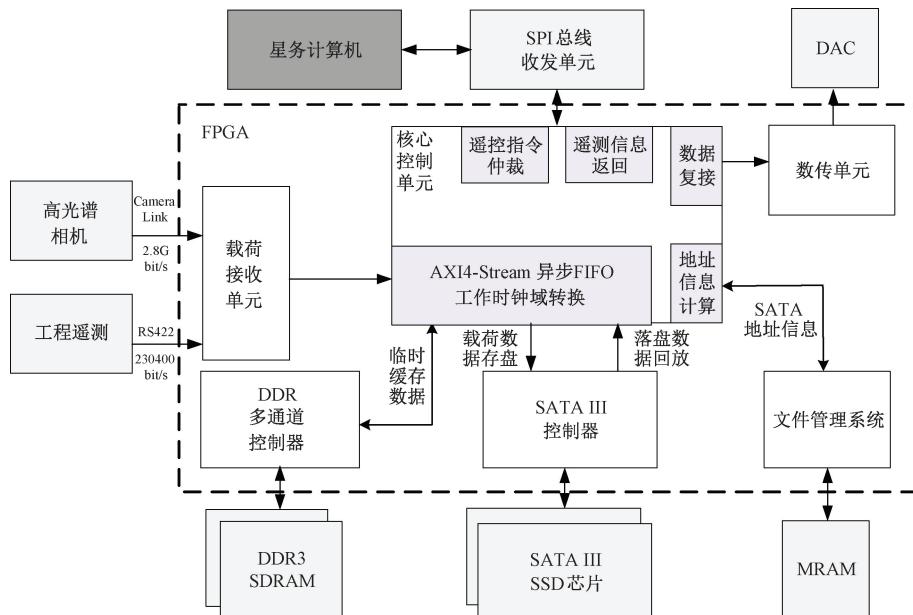

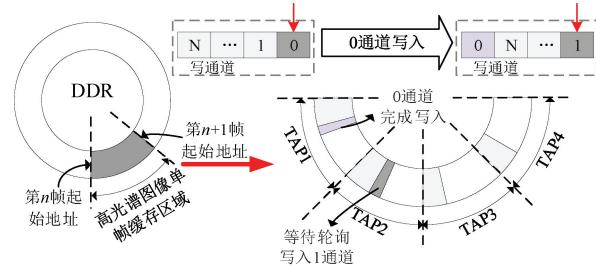

相较于上述架构,本研究提出的星载高性能存储数传一体化系统在性能提升和功能集成方面实现了显著改进。基于吉天星某型号任务中外围载荷为高光谱相机和工程遥测的架构如图 2 所示,通过模块化设计理念,重新构建了系统架构和 FPGA 功能,主要改进包括:

1)核心处理单元:在 FPGA 内通过遥控指令仲裁,遥测信息返回以及地址信息计算,实现了协议解析和地址管理功能。考虑载荷多样性的实际需求,异步工作时钟域转换均封装在核心控制单元内,并基于 AXI4-Stream 协议进行传输,适用于多工作时钟域的数据流传输,便于外围载荷变动后系统的快速移植。

2)SATA III 控制器:以纯逻辑实现方式完成 SATA III 固态存储读写控制器,并提供用户接口直接进行读写指令调用。结合基于 MRAM 的文件管理系统和核心控制单元,替代了传统系统中的 CPU 通信板功能,有效降低设备开销。此外,通过配备两片 2 Tbit 容量的 SATA III 接口固态硬盘(solid state disk,SSD)实现了主备盘切换功能,提高了数据存储的可靠性,并延长了在轨应用时间。

3)DDR 多通道控制器:实现了 AXI-Full 向 AXI4-Stream 接口协议的转换,设置了与核心处理单元匹配的对外用户接口;在数据写入和读出 DDR 过程中设计了新的数据合路算法,减少了片上缓存资源开销;设计了仲裁分发功能,使 DDR 能兼容载荷存盘上行链路和落盘数据下行链路的中间级缓存,支持多链路、多用户同时访问。

4)数传单元:整合了数据复接、AOS 帧组装功能,同时基于 FPGA 工作时钟、数模转换器(digital-to-analog converter,DAC)采样速率和符号速率间的关系,以 12 通道并行的方式完成了符号分散、星座映射等信号处理;设计了一种新的多相插值滤波运算方法,降低了矩阵运算时所需的计算资源;基于奈奎斯特采样定律,提出了一种新的中频

图2 星载存储数传一体化系统架构框图

Fig. 2 Block diagram of integrated high-performance storage and data transmission system architecture

等效载波生成算法,以多通道 DDS 并行采样中频载波,中频载波频率遥控可变。在节省了设备、软件开销情况下,提高了数传速率,QPSK 峰值带宽提升至 600 Mbit/s,8PSK 峰值速率可达 900 Mbit/s,并丰富了数传功能。

## 2 关键技术

### 2.1 SATA III 控制器设计

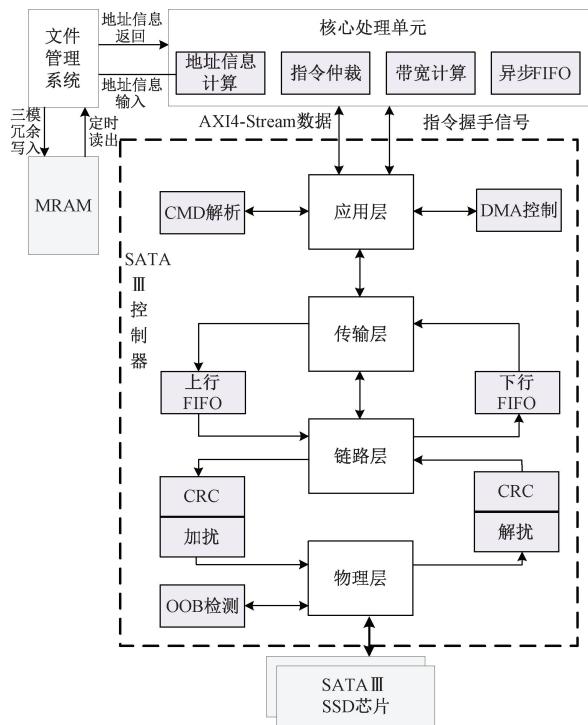

SATA III 协议将理论传输速率提升到了 6.0 Gbit/s,协议上基于 OSI 七层标准架构进行简化,包含四个层级:应用层、传输层、链路层和物理层<sup>[9-11]</sup>。

SATA III 控制器的纯逻辑访问设计流程如图 3 所示,通过对原有的应用层和命令层简化,应用层对外直接提供读写用户命令接口;应用层内采用直接存储器访问(direct memory access,DMA)控制器,将大块数据拆分为多次小量突发访问,提高对多个扇区读写操作的传输效率和资源利用率;传输层作为链路层和应用层之间的介质,通过 FIFO 将 FPGA 和设备之间传递的数据封装为数据帧或完成解封装;链路层从上下行 FIFO 中提取或写入数据,以 CRC-32 校验确保可靠传输;物理层完成 8B/10B 编码、串并转换、K28.5 字符和 OOB 检测、时序控制和校正<sup>[12]</sup>。

由于 SATA 固态硬盘在启动读写数据前包含启动时间,单次读写数据量过小会导致带宽浪费,单次操作数据量过大则会开销较多缓存资源。该控制器单次读写不同数据量时的读写速率如表 1、2 所示。

控制器选用载荷存盘上行链路单次写入 64 KByte,落盘数据回放下行链路单次读出 4 MByte,以达到最好的读写效率。此外,核心处理单元根据控制器返回的握手信号进行带宽与地址信息计算,计算的地址信息以三模冗余的

图3 SATA III 控制器设计流程图

Fig. 3 SATA III controller design flowchart

表1 SATA III 控制器写速率测试

Table 1 SATA III controller write rate test

| 单次写数据量   | 花费时间    | 写计算速率       |

|----------|---------|-------------|

| 64 KByte | 132 μs  | 473 MByte/s |

| 4 MByte  | 9.2 ms  | 434 MByte/s |

| 32 MByte | 77.9 ms | 410 MByte/s |

表 2 SATA III 控制器读速率测试

Table 2 SATA III controller read rate test

| 单次读数据量   | 花费时间        | 读计算速率       |

|----------|-------------|-------------|

| 64 KByte | 578 $\mu$ s | 108 MByte/s |

| 4 MByte  | 9.7 ms      | 410 MByte/s |

| 32 MByte | 71.9 ms     | 435 MByte/s |

方式定时写入 MRAM。指令仲裁模块在读写操作中动态调整读写任务的优先级顺序, 实现上行、下行链路并行执行。

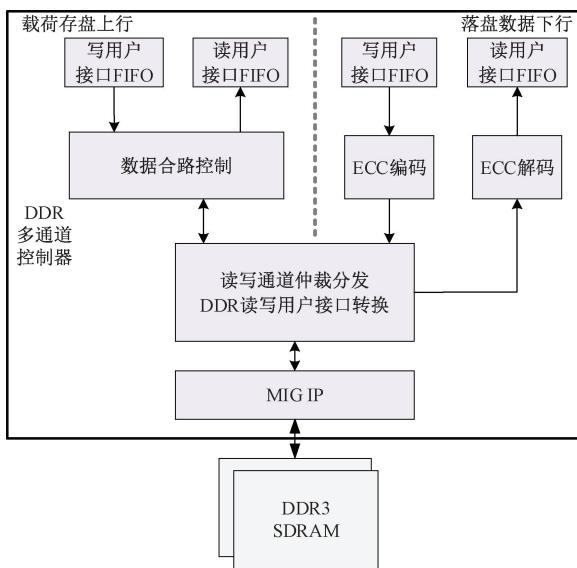

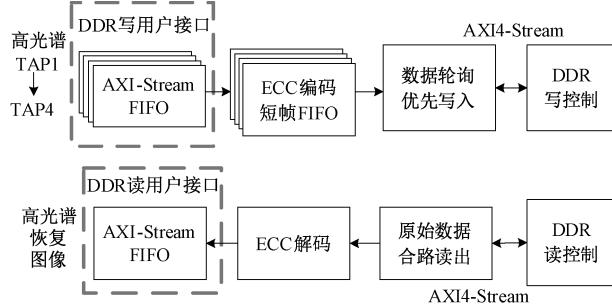

## 2.2 DDR 多通道控制器设计

新型载荷分辨率更高, 单帧图像传输数据量更大。如图 2 所示的在轨工作场景, 高光谱开窗 20 个光谱成像区, 在保证传输质量和相机速率的前提下势必要对单帧图像进行拆分以并行传输, 以分 4 通道(TAP)为例, 单通道最大速率可达 700 Mbit/s。如图 4 所示, 数据经过载荷接收单元和核心控制单元处理, 最终通过控制器写用户接口访问 DDR。对于数据合路以及写入 DDR 的方案, 文献<sup>[5]</sup>提及的数据合路模块采取片上 FIFO 资源对整帧数据进行缓存, 再通过轮询的方式实现图像恢复, 在短帧情况下, 该设计实现清晰简单, 但是一旦单通道速率、帧长上升或轮询通道数增多, 势必会增加 FIFO 溢出风险, 存在数据丢包或链路数据传输卡死的情况。

图 4 DDR 多通道控制器设计流程图

Fig. 4 DDR multi-channel controller design flowchart

本系统针对合路过程中片上缓存溢出或链路卡死的风险点, 设计了新的数据合路控制算法。算法将数据合路功能穿插在数据写入和读出 DDR 的过程当中, 省去了大量片上 FIFO 资源的开销。并且该控制器集成了读写通道仲裁分发, 多链路访问仲裁以及用户接口配置功能, 支持多用户同时访问, 上行、下行链路同时访问 DDR。

数据合路控制算法具体实现如图 5 所示。合路控制实现过程中为确保星上数据传输的可靠性, 避免原始图像在 DDR 缓存后出现位翻转(bitflip), 算法引入了纠错编码(error correcting code, ECC)的机制<sup>[13]</sup>。此外, 考虑到 AXI4 协议对突发传输地址边界(4 KByte)的限制<sup>[14]</sup>, ECC 编码后的通道数据在 DDR 读写通道仲裁分发前被预先切分为 4 KByte 小帧, 并在后续 DDR 写入任务中以单通道单次 4 KByte 的方式, 按照轮询优先级控制写入顺序。

图 5 高光谱相机载荷数据合路控制实现流程图

Fig. 5 Hyperspectral camera load data merge control implementation flowchart

合路控制算法中, 数据轮询优先写入原理实现如图 6 所示, 控制器以环形缓冲池的方式访问外部 DDR, 每帧高光谱图像数据均拥有独立的起始地址和存储空间, 控制器对单帧图像缓存区域进行拆分设计, 每个 TAP 拥有各自的起始地址。

图 6 轮询优先工作原理

Fig. 6 Polling priority working principle in merge control algorithm

数据写入过程中, 控制器采用轮询优先机制, 通过循环移位寄存器的方式对工作通道进行仲裁。例如, TAP1 数据写入完成后, 下次轮询通道将切换至 TAP2, 等待控制器进行仲裁和分发。4 通道 AXI4-Stream FIFO 中的帧结束标识符信号用于指示该帧图像数据最后一次写入环形缓冲池。

数据读取过程中, 控制器根据该帧起始地址以及 4 个 TAP 的起始地址, 按照单 TAP 数据量顺序读取, 实现编码后数据的合路输出, 避免了数据链路卡死或 FIFO 溢出的风险。读取的数据经过 ECC 解码模块进行检错和纠正, 最终由 DDR 读用户接口将原始图像数据传输至后级模块。

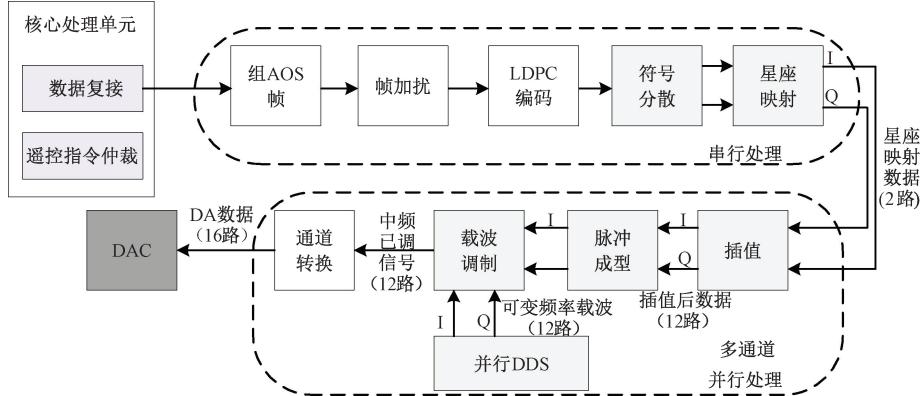

### 2.3 数传单元设计

在星上发射机的数字电路设计中,一般采用“FPGA + DAC + 信道方式”架构,数传功能涵盖基带数字信号处理和中频调制<sup>[15]</sup>。随着中频输出频率越来越高,受限于 FPGA 器件工作时钟频率,成型滤波器和中频载波实现较为困难。因此,文献[5-6]中提出的星载系统直接转发原始基带数据,避免在 FPGA 中实现后续信号处理;文献[3,7]虽然实现了编码和加

扰等功能,但是其中频信号处理需额外硬件支持。这些传统设计方案在数传功能上仅支持固定的编码、调制、符号速率,数传功能往往不支持星务计算机控制,灵活性不足。

为实现遥控可变的星载数传单元,基于 CCSDS 推荐的 AOS 标准实现了基带信号和中频信号的综合处理,其设计架构如图 7 所示,其中数传单元的工作时钟为 150 MHz,DAC 采样率为 1.8 GHz。

图 7 数传单元设计架构

Fig. 7 Digital transmission unit design architecture

为了充分阐述系统的工作原理,以下详细介绍各关键功能单元及其实现原理:

1) 符号分散单元根据每次星座映射所需的比特数量  $n$ ,对 AOS 数据流进行分散处理。同时,考虑工作时钟频率  $f_{clock}$  与符号率  $R_{symbol}$  之间的关系,确定并行处理通道的数量  $N_{channels}$ 。这些参数之间的具体关系可表示为:

$$N_{bits} = \frac{R_{symbol} \cdot n}{f_{clock}} = \frac{R_{symbol} \cdot \log_2 M}{f_{clock}} = \frac{R_{bit}}{f_{clock}} = N_{channels} \cdot n \quad (1)$$

其中,  $n$  表示每个星座映射后符号所携带的 bit 数,  $M$  是调制阶数,  $N_{bits}$  为每时钟周期符号分散单元需处理的 bit 数,  $R_{bit}$  是比特速率。例如,在  $R_{bit}$  为 600 Mbit/s 的 QPSK 调制方案中,每个时钟需分散的比特数量  $N_{bits}$  为 4,以同时完成 2 次 QPSK 星座映射处理。

2) 星座映射后的符号数据需在符号间进行内插,将符号速率  $R_{symbol}$  匹配至 DAC 采样速率  $f_{DAC}$ ,以确保在物理信道具有良好的传输特性。内插后数据速率与 DAC 采样速率一致,脉冲成型用于限制信号带宽。升余弦滤波器是满足脉冲成型的常用滤波器之一,其冲击响应函数如下:

$$h_{RC}(t) = \frac{\sin\left(\frac{\pi t}{T}\right)}{\frac{\pi t}{T}} \cdot \frac{\cos\left(\frac{\pi \beta t}{T}\right)}{1 - \frac{4\beta^2 t^2}{T^2}} \quad (2)$$

其中,  $T$  为符号周期,  $\beta$  为成型滤波器中滚降系数。

在时域中,升余弦滤波器的脉冲响应使当前符号在其

他符号的理想采样点的幅度为零,无码间干扰。而在通信系统中,系统的传递函数  $H_{system}(f)$  等于通信发送端  $H_T(f)$ 、通信接收端  $H_R(f)$  和信道  $H_c(f)$  三者乘积,在理想信道 ( $H_c(f) = 1$ ) 情况下,可化简为  $H_T(f)$  和  $H_R(f)$  的乘积。因此,收发两端共同选用平方根升余弦滤波器拆解设计复杂度。

$$H_T(f) = H_{RRC}(f) = \sqrt{H_{RC}(f)} \quad (3)$$

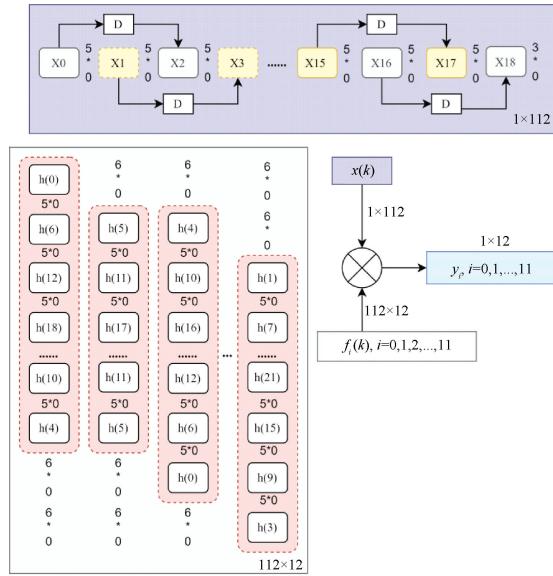

为了降低滤波器设计复杂度,以最大符号速率  $R_{symbol}$  为 300 Msymbol/s 设计平方根升余弦滤波器,其内插系数为 6。12 路并行滤波输出计算公式如下:

$$y_i = x(k) * f_i(k) = \sum_{k=0}^T x(k) \cdot f_i(T - C + i - k), \\ i = 0, 1, 2, \dots, C - 1 \quad (4)$$

其中,  $C$  为通道数量;  $y_i$  为滤波器输出的  $C$  路数据;  $T$  为矩阵行数,  $T = N - 1 + C$ ;  $N$  为滤波器阶数,实际选用 101 阶;  $x(k)$  由滤波器输入数据和内插 0 构成的序列,长度为  $T$ ;  $*$  为卷积运;  $f_i(k)$  为滤波器系数和 0 组成的  $T \times C$  大小的矩阵。

为了降低矩阵运算时乘法、加法计算所需的硬件资源,基于式(5)的计算方法和滤波器对称特性,本系统设计了一种新的多相插值滤波运算方法,如图 8 所示。

待滤波序列由输入符号数据 X0,X1 和延迟单元组成,滤波系数矩阵第一列仅在待滤波序列有效符号位置配置滤波系数,其余位置以零填充,列与列之间进行向下循环移位,在有效位置得到新的滤波器系数。该方法在减少加法、乘法次数的同时,减少了存储资源的开销。

图 8 根升余弦滤波器计算结构示意图

Fig. 8 Schematic diagram of the computational structure of the root-lift cosine filter

$$\begin{aligned} y_0 = & \sum_{i=0}^{100} x(n) \cdot h(n-i) = X_0 \cdot h(100) + \\ & 0 \cdot h(99) + \dots + X_1 \cdot h(94) + \dots + 0 \cdot h(5) + \\ & X_{16} \cdot h(4) + \dots = X_0 \cdot h(0) + X_1 \cdot h(6) + \dots + \\ & X_{15} \cdot h(10) + X_{16} \cdot h(4) \end{aligned} \quad (5)$$

此外,根据系统最高符号率(300 Msymbol/s)与最低符号率(25 Msymbol/s)的关系,在以内插系数为 6 的平方根升余弦滤波器基础上,设计了 2 级半带滤波器和 1 级 1/3 带滤波器。通过遥控指令级联滤波器,使系统适应多种符号速率。

3) 中频载波采用并行多通道直接数字式频率合成器(direct digital synthesizer, DDS)生成。在文献[15]的应用中,并行 DDS 主要用于内插和脉冲成型,即将成型数据以查找表的形式存入 FPGA 中,通过 M 路并行 DDS 实现  $M \times f_0$  速率的映射,其关系如下:

$$f_0 = \frac{M \times K \times f_s}{2^N} \quad (6)$$

其中,  $K$  为频率控制字,  $f_s$  为 DAC 采样速率,  $f_0$  为每个通道采样速率,  $N$  为频率控制字分辨率。

基于该并行结构和奈奎斯特采样定理,本系统提出一种新的中频等效载波生成算法,通过欠采样的形式采用 DDS 生成多通道等效载波,并按照 DAC 采样速率获取等效载波通道间相位差,等效载波频率转换公式及转换后通道相位计算表达式如下:

$$f_{\text{equivalent}} = f_{\text{carrier}} - \frac{f_{\text{carrier}}}{f_{\text{clock}}} \times f_{\text{clock}} \quad (7)$$

$$\theta_i = \theta \cdot i + \varphi = \frac{f_{\text{carrier}}}{f_{\text{dac}}} \cdot 2\pi \cdot i + \varphi, i = 0, 1, 2, \dots, 11 \quad (8)$$

其中,  $f_{\text{carrier}}$  为中频载波频率,  $f_{\text{equivalent}}$  为等效载波频率,  $X$  表示向下取整,  $\theta_i$  为  $i$  通道等效载波相位值,  $\varphi$  为初相位。

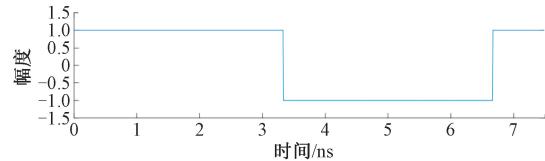

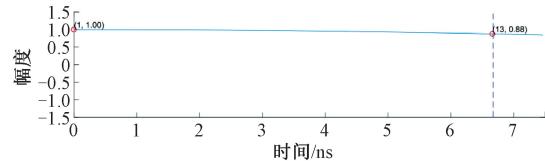

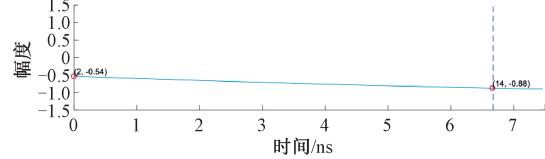

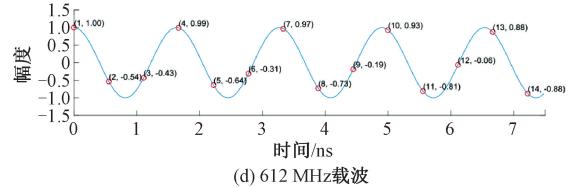

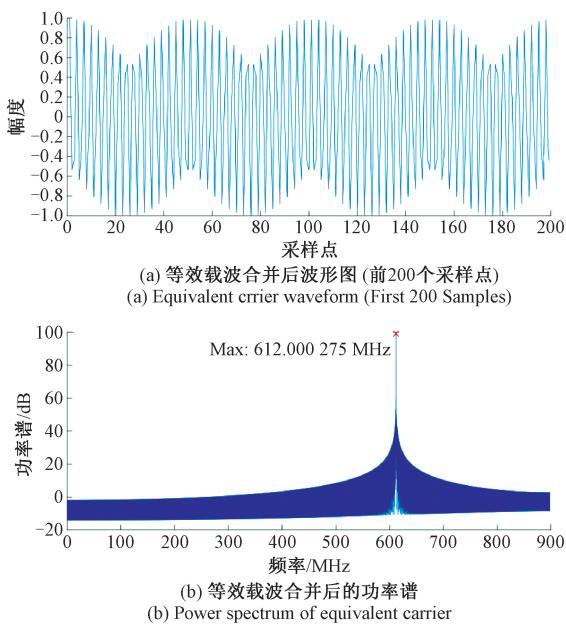

以生成  $f_{\text{carrier}}$  为 612 MHz 的中频载波为例,  $f_{\text{equivalent}}$  经计算为 12 MHz, 通过工作时钟可直接生成该频率的等效载波。如图 9(a)所示, 在相邻 2 个时钟触发沿, 以通道 0、通道 1 为例, 对这两个通道生成的 12 MHz 等效载波采样。如图 9(b)所示, 通道 0 获得的两个采样值为 1.00、0.88; 如图 9(c)所示, 通道 1 获得的两个采样值为 -0.54、-0.88。这些采样值与如图 9(d)所示的直接生成 612 MHz 载波, 并以 1.8 GHz 采样频率获得的第 1、2、13、14 个采样值一致。

(a) 150 MHz 工作时钟

(a) 150 MHz workingClock(b) 第0通道12 MHz等效载波

(b) Channel 0: 12 MHz equivalent carrier(c) 第1通道12 MHz等效载波

(c) Channel 1: 12 MHz equivalent carrier(d) 612 MHz 载波

(d) 612 MHz carrier

图 9 612 MHz 中频载波等效生成示意图

Fig. 9 Schematic diagram of 612 MHz IF carrier equivalent generation

进一步, 通过对 12 个通道的等效载波采样值合并, 其波形图如图 10(a)所示, 并进行频谱分析。如图 10(b)所示, 傅里叶变换后最大频点为 612.000 275 MHz, 误差为  $4.49 \times 10^{-7}$ 。本设计解决了受限于 FPGA 器件工作时钟频率而无法完成中频调制的难点, 且满足星上应用的精度要求。

### 3 实验与结果

#### 3.1 地面测试

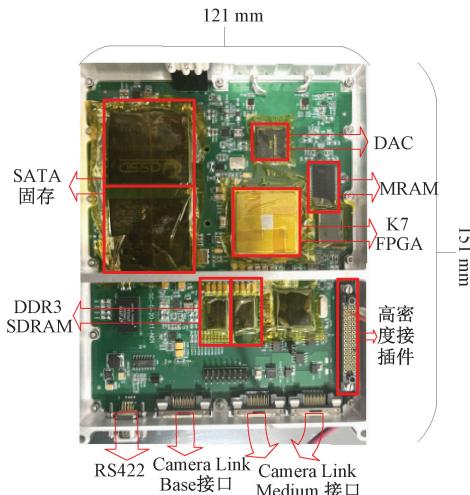

本系统硬件单机如图 11 所示, Camera Link Medium 接

图 10 12 通道等效载波合并后的波形及功率谱

Fig. 10 Waveforms and power spectra after 12-channel equivalent carrier merging

图 11 存储数传一体化系统硬件单机

Fig. 11 Storage digital transmission integration system hardware standalone

口对应高光谱相机载荷,其峰值传输速率超过 2.8 Gbit/s。

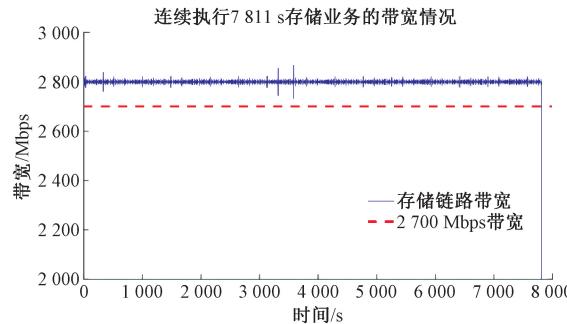

为了验证系统上行链路带宽和稳定性,进行了板级业务测试。对高光谱相机载荷执行记录业务,经 FPGA 集成逻辑分析仪(integrated logic analyzer, ILA)实时抓取核心处理单元计算的载荷存盘上行链路带宽数据,如图 12 所示,测试结果表面上行链路带宽长期稳定在 2.8 Gbit/s。

图 12 载荷存盘上行链路带宽

Fig. 12 Load bank uplink bandwidth

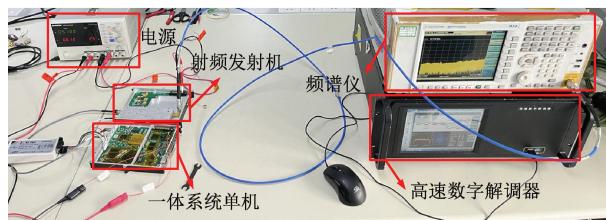

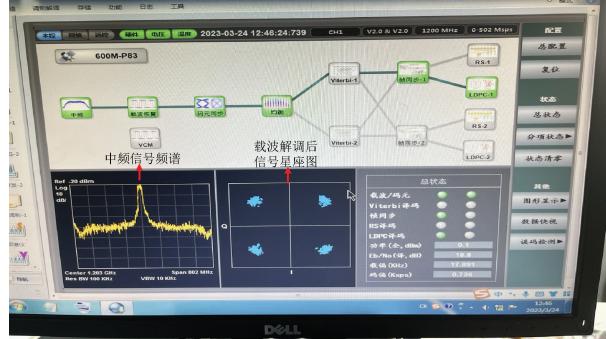

为进一步评估本系统的可靠性,搭建了地面系统测试平台。如图 13 所示,射频发射机与本系统硬件单机相连,负责接收中频业务信号;高速数字解调器与射频发射机相连,根据遥控配置完成解调、解码等信号处理工作。该解调器可以实时显示接收信号频谱和解调后的星座图,同时存储解码后的 AOS 帧数据。

图 13 系统测试平台

Fig. 13 System testbed

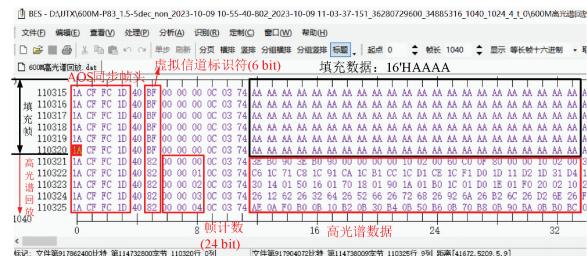

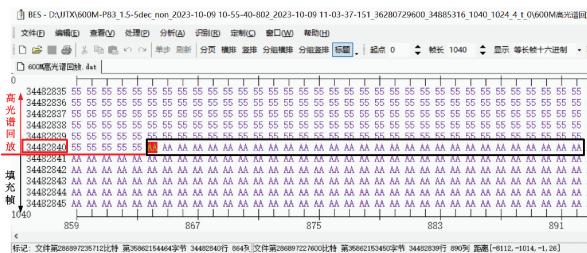

采用 BESNEW 分析高速数字解调器解码后数据,并在系统测试中按照表 3 查找“AOS 帧同步头”和“虚拟信道标识”对应的独特码,以确定当前信道传输载荷类型,并根据“VCDU 计数”验证系统传输过程的完整性、正确性。

表 3 CCSDS AOS 标准数据帧格式<sup>[15]</sup>

Table 4 CCSDS AOS standard data frame format

| 参数    | AOS 帧同步头      | 版本    | 航天<br>标识 | 虚拟信道<br>标识 | VCDU<br>计数 | 信息<br>速率 | VCDU 长度 | VCDU<br>数据域 | VCDU<br>差错控制 |

|-------|---------------|-------|----------|------------|------------|----------|---------|-------------|--------------|

| 数据位宽  | 32            | 2     | 8        | 6          | 24         | 8        | 16      | 7072        | 1024         |

| 高光谱数据 | 32'H1ACF_FC1D | 2'B01 | 8'H02    | 6'B11_1111 |            |          | 16'D884 |             |              |

| 填充帧数据 | 32'H1ACF_FC1D | 2'B01 | 8'H02    | 6'B00_0010 |            |          | 16'D884 | 8'HAA 填充    |              |

为了全面验证系统执行业务的可靠性,采取先执行高

光谱数据记录,再执行高光谱数据回放业务,并通过数据

分析校验系统链路中是否出现数据丢包,载荷数据是否连续完整。系统数传业务通过遥控指令配置为 QPSK、600 Mbit/s 速率,中频载波设定为 612 MHz。

如图 14 所示为高速数字解调器提供的用户界面,在高光谱回放业务期间,系统帧同步锁定,载波同步锁定,载波解调后星座图为标准 QPSK 星座图,中频信号频谱 300 MHz,中心频点在 1.2 GHz。这些观测结果与本文的配置参数吻合,证实了系统数传功能的完整性和稳定性。

图 14 高速数字解调器用户界面

Fig. 14 High-speed digital demodulator user interface

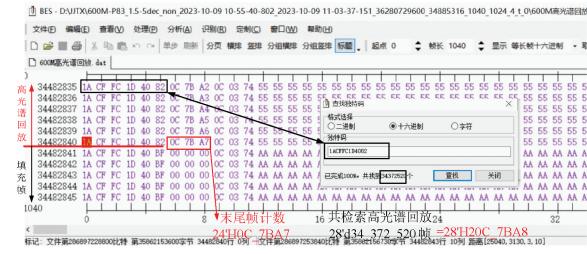

随后依据表 3,通过 BESNEW 软件对高速数字解调器捕获的 AOS 帧数据进行深入分析。图 15(a)呈现了高光谱回放业务启动前,系统填充数据 8'HAA 作为“VCDU 数据域”,以填充帧的形式在信道中传输;高光谱回放业务启动后,“VCDU 计数器”从 0 累加,“虚拟信道标识符”被修订为高光谱标识,标志着数传单元开始在信道中传输实际的高光谱载荷数据。图 15(b)展示了高光谱数据传输的统计信息,高光谱数据首帧与尾帧之间的统计行号差值为 34 372 520,为了验证这一结果的准确性,通过独特码查找高光谱数据行数,得到的结果同样为 34 372 520 行(可转换为 32'H020C\_7BA8)。

进一步分析高光谱回放数据的尾帧,“VCDU 帧计数”为 24'H0C\_7BA7,考虑到其位宽设定为 24 位,该区域在传输过程中发生了两次计算溢出。其精确计算过程为:

$$\text{Amount}_{\text{高光谱}} = 2 \times (24'\text{HFF}_{\text{FFFF}} + 1) + 24'\text{H}0\text{C}_{7\text{BA7}} + 1 + 24'\text{H}0\text{C}_{7\text{BA7}} + 1 = 32'\text{H}020\text{C}_7\text{BA8} \quad (9)$$

这一计算结果与之前的统计信息完全吻合,有力证明了本系统在执行 28.29 GByte 大数据量存储与数传业务的可靠性。

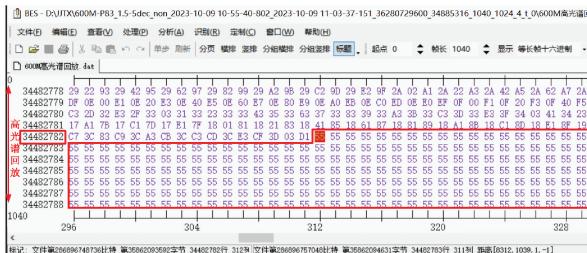

进一步验证系统在数据处理边界下的填充策略正确性,图 16(a)展示了高光谱数据记录业务终止时刻,当单次写入数据量不满足 SATA III 控制器预设的 64 Kbyte 时,系统以 8'H55 填充剩余空间,确保数据块的完整。同样,如图 16(b)所示,在数传下行链路的尾帧处理中,当剩余有效载荷数据不足以填满“VCDU 数据域”时,系统以 8'HAA 进行填充。这些观测结果充分证明了本系统在执行业务期间填充策略的准确性。

(a) Hyperspectral playback of first frame data

(b) Hyperspectral playback of end-frame data

图 15 存储、数传业务正确性测试

Fig. 15 Storage, digital transmission service correctness test

(a) Hyperspectral recording stopped, drop disk filled 8'H55

(b) Hyperspectral playback stops with 8'HAA end-frame padding

图 16 存储、数传业务填充策略测试

Fig. 16 Storage, digital transmission service fill policy testing

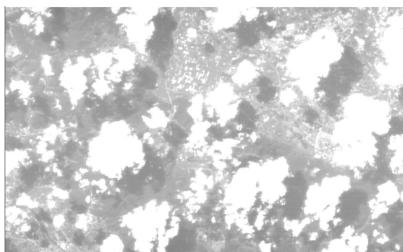

### 3.2 在轨验证

通过吉天星某型号任务的在轨应用,对落盘载荷数据执行数传下行业务并经地面站解析,其高光谱相机在轨拍摄的高分辨率云层图像如图 17 所示。云层清晰完整,这一在轨验证结果证实了本系统在实际空间环境的有效性和可靠性。

### 3.3 系统性能对比

为了全面评估本研究所设计的存储数传一体化系统

图 17 卫星在轨拍摄的高分辨率云层图像

Fig. 17 High-resolution cloud images taken by satellites in orbit

在系统复杂度、存储性能和数传功能等方面的优势,本文进行了与现有文献[3,5,8]中提出系统的对比分析,它们均为面向存储业务和数传业务而设计的星载系统,应用背景相似,表4详细呈现了系统之间的比较结果。

在系统设备数量和软件数量最少的情况下,本系统最高存储速率可达3.69 Gbit/s,存储容量、数传速率均为最高水平,通过FPGA实现的数传功能不仅涵盖了对比系统所支持的全部功能,还进一步拓展支持了脉冲成型、中频调制等功能。

表4 本系统与现有文献提出系统的性能对比示意表

Table 4 Schematic table comparing the performance of this system with the existing systems proposed in the literature

| 参数                            | 本文系统                                                           | 文献[3]               | 文献[5]             | 文献[8]            |

|-------------------------------|----------------------------------------------------------------|---------------------|-------------------|------------------|

| 设备数量                          | 1                                                              | 2                   | 3                 | 11               |

| 软件数量                          | 1                                                              | 1                   | 4                 | 17               |

| 最高载荷速率/(bit·s <sup>-1</sup> ) | 2.88 G                                                         | 550 M               | 1.6 G             | 20 G             |

| 存储容量/bit 及介质                  | 4 T<br>SATA SSD                                                | 512 G<br>NAND flash | 4 T<br>NAND flash | 3 T<br>NOR flash |

| 最高存储速率/(bit·s <sup>-1</sup> ) | 3.69 G<br>900 M<br>(8PSK)<br>600 M<br>(QPSK)<br>7/8 LDPC<br>加扰 | 1 G<br>—            | 4 G<br>—          | 9.3 G<br>450 M   |

| FPGA 实现的数传功能                  | 星座映射<br>脉冲成型<br>中频调制                                           | 7/8<br>LDPC         | 7/8 LDPC          | 加扰               |

## 4 结论

本研究设计并实现了一种卫星高性能存储数传一体化系统。在DDR多通道控制器设计中提出了一种在数据写入和读出DDR时的合路控制算法,节约了大量片上FIFO资源,同时避免了片上缓存溢出或链路卡死的风险。在中频调制模块提出了一种中频等效载波生成算法,中频载波由一组并行工作的DDS产生,每个DDS以欠采样的形式生成多通道等效载波,并按照所需的输出采样速率获取等效载波通道间相位差,以匹配DAC的采样速率。通过地面测试和在轨验证,本系统存储链路带宽长期稳定在2.8 Gbit/s以上,存储、数传业务零误码运行,充分满足了可靠性与稳定性的工作要求;同时与传统的星载系统相比,系统复杂度低,数传业务更为丰富。随着在轨应用的进一步拓展,本系统具有广阔的应用前景和重要的科研价值。

## 参考文献

- [1] 张兵.当代遥感科技发展的现状与未来展望[J].中国科学院院刊,2017,32(7):774-784.

ZHANG B. Current status and future prospects of remote sensing [J]. Bulletinof Chinese Academy of Sciences,2017,32(7):774-784.

- [2] 徐伟,朴永杰.从Pleiades剖析新一代高性能小卫星技术发展[J].中国光学,2013,6(1):9-19.

XU W, PU Y J. Analysis of new generation high-performance small satellite technology based on the Pleiades[J]. Chinese Optics,2013,6(1):9-19.

- [3] 许志宏,董振兴,安军社.基于FPGA的星载一体化高速数据复接器设计[J].电子设计工程,2018,26(5):184-188,193.

XU ZH H, DONG ZH X, AN J SH, et al. Design of spaceborne integrated high-speed data multiplexer

- based on FPGA [J]. Electronic Design Engineering, 2018, 26(5):184-188,193.

- [4] 徐伟,金光,王家骐.吉林一号轻型高分辨率遥感卫星光学成像技术[J].光学精密工程,2017, 25 (8): 1969-1978.

- XU W, JIN G, WANG J Q. Optical imaging technology of JL-1 lightweight high resolution multispectral remote sensing satellite[J]. Optics and Precision Engineering, 2017, 25(8):1969-1978.

- [5] 郝中旭. LDPC 编码与星载多通道存储系统研究[D]. 株洲:湖南工业大学,2023.

- HAO ZH X. Research on LDPC coding and spaceborne multichannel storage system [D]. Zhuzhou: Hunan University of Technology,2023.

- [6] 孙金傲,陈茂胜,邹吉炜,等.微小卫星固存控制系统设计与实现[J].电子测量技术,2023,46(10):1-5.

- SUN J AO, CHEN M SH, ZOU J W, et al. Design and realization of microsatellite storage control system [J]. Electronic Measurement Technology, 2023, 46 (10): 1-5.

- [7] 刘静军,贺小军,王鹏,等.星载多模式和多通道图像采集与处理[J].电子测量技术,2023,46(20):30-35.

- LIU J J, HE X J, WANG P, et al. Spaceborne multi-mode and multi-channel image acquisition and processing[J]. Electronic Measurement Technology, 2023, 46(20):30-35.

- [8] 王元乐,张建华,杨玉辰,等.北京三号 A/B 卫星数传智能处理器在轨处理关键技术及应用[J].航天器工程,2023,32(3):138-144.

- WANG Y L, ZHANG J H, YANG Y CH, et al. Key technologies and applications of on-orbit processing for BJ-3A/B satellites data transmission intelligent processor[J]. Spacecraft Engineering, 2023, 32 (3): 138-144.

- [9] LIU P, WANG Z G, LIU J F, et al. A payload data storage and management method for Chang'E-5[J]. Journal of Deep Space Exploration, 2021, 8 (3): 299-305.

- [10] ZHANG J. Real-time image storage technology of high-speed camera based on camera link interface[C]. Ninth Symposium on Novel Photoelectronic Detection Technology and Applications. SPIE, 2023, 12617: 1300-1304.

- [11] WU W, SU H, WU Q. Implementing a serial ATA controller base on FPGA [C]. 2009 Second International Symposium on Computational Intelligence and Design. IEEE, 2009, 1: 467-470.

- [12] 杨亚涛,张松涛,李子臣,等.SATA 3.0 物理层设计与 FPGA 实现[J].计算机工程与应用,2017,53(20): 38-42.

- YANG Y T, ZHANG S T, LI Z CH, et al. Design and implementation for physical layer of serial ATA revision 3.0 based on FPGA [J]. Computer Engineering and Applications, 2017, 53(20):38-42.

- [13] 王轩,常亮,李杰,基于 FPGA 的 NAND Flash ECC 校验系统设计与实现[J].电子设计工程,2018,26(18): 184-187,193.

- WANG X, CHANG L, LI J. Design and implementation of NAND flash ECC check-out system based on FPGA[J]. Electronic Design Engineering, 2018, 26(18):184-187,193.

- [14] 翁天恒,袁永春,周榕,等.基于 FPGA 的 DDR4 多通道控制器设计[J].电子测量技术, 2022, 45 (12): 148-155.

- WENG T H, YUAN Y CH, ZHOU R, et al. Design of DDR4 multi-channel controller based on FPGA[J]. Electronic Measurement Technology, 2022, 45 (12): 148-155.

- [15] 石彬,高宁,周庭伊.远程动态可重构遥测加密发射机的设计与实现[J].遥测遥控,2024,45(4):81-88.

- SHI B, GAO N, ZHOU T Y. Remote dynamic reconfigurable telemetry encryption transmitter design and implementation [J]. Journal of Telemetry, Tracking and Command, 2024,45(4):81-88.

### 作者简介

朱彦铭(通信作者),硕士研究生,主要研究方向为 FPGA 数字信号处理。

E-mail:shenhua66@shu.edu.cn