DOI:10.19651/j.cnki.emt.2416965

# 基于 FPGA 和国产射频收发器的多通道信号源设计与实现<sup>\*</sup>

何冉 李鹏 冯姣

(南京信息工程大学电子与信息工程学院 南京 210044)

**摘要:** 针对通信测试中需要模拟多种信号这一需求,提出一种大带宽、多通道的信号源硬件架构,以 FPGA 作为硬件控制核心以及基带信号发生器,利用 FPGA 中的高速串行收发器 GTY,实现 JESD204C 接口协议,完成单 Lane 16.5 Gbps 的数据率传输。以 CX8242K 射频收发器为射频发射端,通过 Microblaze 进行配置,实现了调制信号从基带到高中频的高质量产生。针对目标频段,进行了频率规划,并设计了时钟方案和多通道同步方案。最终实现了一款具备宽频带、高精度、低杂散的国产化多通道矢量信号源。经测试证明,该矢量信号源能正常生成各种矢量调制信号,并实现 10 M~6 GHz 范围内的载波频率调节,支持单通道发射信号最大带宽高达 800 MHz,在实际工程测试中有很高的应用价值。

**关键词:** 矢量信号源;FPGA;JESD204C;Microblaze;CX8242K

中图分类号: TN919 文献标识码: A 国家标准学科分类代码: 510.5010

## Design and implementation of multi-channel signal source based on FPGA and domestic RF Transceiver

He Ran Li Peng Feng Jiao

(School of Electronic and Information Engineering, Nanjing University of Information Science and Technology, Nanjing 210044, China)

**Abstract:** In view of the need to simulate multiple signals in communication testing, a large-bandwidth, multi-channel signal source hardware architecture is proposed. FPGA is used as the hardware control core and baseband signal generator. The high-speed serial transceiver GTY in FPGA is used to implement the JESD204C interface protocol and complete the single-lane 16.5 Gbps data rate transmission. The CX8242K RF transceiver is used as the RF transmitter and configured through Microblaze to achieve high-quality generation of modulated signals from baseband to high-IF. Frequency planning is carried out for the target frequency band, and clock schemes and multi-channel synchronization schemes are designed. Finally, a domestically produced multi-channel vector signal source with wide bandwidth, high precision and low spurious is realized. Tests have proved that the vector signal source can normally generate various vector modulation signals, and realize carrier frequency adjustment in the range of 10 M~6 GHz, supporting a single-channel transmission signal with a maximum bandwidth of up to 800 MHz, which has high application value in actual engineering tests.

**Keywords:** vector signal source;FPGA;JESD204C;Microblaze;CX8242K

## 0 引言

为了检验通信设备或系统的性能及参数指标,需要产生各种信号来模拟复杂电磁环境,但是随着军事现代化对电子战和通信系统的要求不断提高,对信号源的性能要求也越来越高,主要表现在国产化、高频率、宽频带、高精度、

多通道等方面<sup>[1]</sup>。因此设计一种射频矢量信号源,能够发射大带宽、高精度、低杂散的信号来模拟复杂电磁环境,是非常有必要且具有广泛应用前景的。

国内外矢量信号源的产品种类繁多。国外厂家主要是德科技、R&S 以及 AnaPico。其中,AnaPico 的多通道信号源覆盖频率范围为 100 kHz~40 GHz,具有极低的相位

收稿日期:2024-09-23

\* 基金项目:国家重点研发计划(2022YFB2902100)、江苏省重点研发计划(BE2023088)项目资助

噪声以及出色的多通道一致性。但是产品价格昂贵且依赖于进口,存在供应链风险,不适合应用于国防及其他关键领域。国内中星联华 SLFS 系列多通道信号源输出频率范围为 2~18 GHz,支持 5/6/8 通道输出,通过高频参考输入来保证多通道同步,但是主要器件国产化程度较低。创远信科 T3661A 矢量信号发生器可支持频率范围为 1 MHz~12.75 GHz,但是仅支持单通道,最大调制带宽为 500 MHz。可见国产信号源或多或少存在调制带宽小、通道数少、相位一致性差、国产化程度低的问题。

此外,目前信号源设计大多采用 FPGA+DAC 架构,但是射频 DAC 方面仍旧面临两个难题<sup>[2]</sup>。一是射频芯片的选型仍以进口芯片为主,其中主要供应商为美国 ADI、TI、亚诺德等公司<sup>[3-4]</sup>。二是传统的 DAC 由于其通道集成度低,在生成高采样速率和多通道的信号时,输出管脚数量过多,使得 PCB 布局复杂度大幅增加。为降低成本并优化 PCB 布局,基于 JESD204 协议的数据传输接口应运而生,并广泛应用于 AD/DA 转换器和 RF 收发器中<sup>[5]</sup>。最新的 JESD204C 已经可支持单 lane 高达 32.5 Gbps 的数据速率传输<sup>[6]</sup>。

基于上述背景,采用 FPGA+国产射频芯片 CX8242K 的结构设计实现了一款矢量信号源。选用国产 CX8242K 射频收发器,提高了信号源的自主可控性以及供应链安全性。内嵌 Microblaze 软核,降低了硬件复杂度,提高了动态配置能力,方便用户进行灵活的系统配置和控制。利用高速收发器 GTY 实现了 JESD204C 协议,弥补传输信号带宽小以及通道集成度低的缺点。通过频率规划,避免了高频镜像的干扰,优化了输出信号质量。设计多通道信号源的时钟方案和同步机制,确保了各通道的相位和幅度一致性。

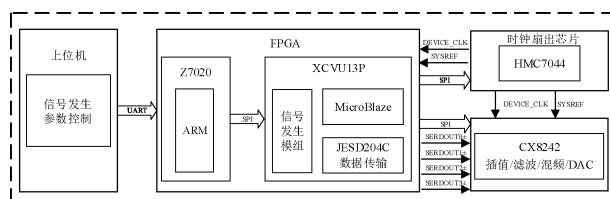

## 1 硬件方案设计及指标要求

本文设计的信号源硬件部分包括 FPGA 载板,射频收发器,时钟管理芯片。FPGA 芯片采用 XCVU13P 以及 Z7020,射频收发器采用城芯公司的 CX8242K,时钟芯片采用 HMC7044。软件部分包括信号源上位机软件以及 CX8242K 配置软件。总体设计框图如图 1 所示。

图 1 系统总体设计框图

Fig. 1 System overall design block diagram

系统基本控制流程是:上位机通过串口对设备部分参数进行控制,包括发送信号类型、调制信号类型、干扰扫频带宽、干扰扫频周期、干扰功率等。此类控制信号在芯片 Z7020 的 ARM 核上处理并通过 SPI 总线协议发送给芯片

XCVU13P。XCVU13P 芯片通过 Microblaze 软核与 AXI 总线桥的互联来实现对内部基带信号发生模组以及外设芯片(CX8242K、HMC7044)的控制。主要控制参数包括输入参考时钟频率、DAC 采样率、时钟源选择、电源设置、混频器设置及 Serdes 设置等。

系统数据流设计方案为信号发生模组接收到控制信号后产生对应的基带信号数据<sup>[7]</sup>,随后数据存于 FIFO 中通过 JESD204C 接口发送高速串行数据给射频芯片 CX8242K,在 CX8242K 中进行插值、滤波、混频等一系列操作后转为射频模拟信号输出。根据设计要求,技术指标如表 1 所示。

表 1 设计指标要求

Table 1 Design index requirements

| 指标名称   | 指标要求              |

|--------|-------------------|

| 输出频率范围 | 10 MHz~6 GHz      |

| 发射带宽   | 支持 800 MHz        |

| 单音动态范围 | ≥50 dBc           |

| 输出相位噪声 | ≤-99 dBc/Hz@1 kHz |

| DA 位数  | ≥14 bit           |

## 2 RF 收发器 CX8242K 及其发射通道设计

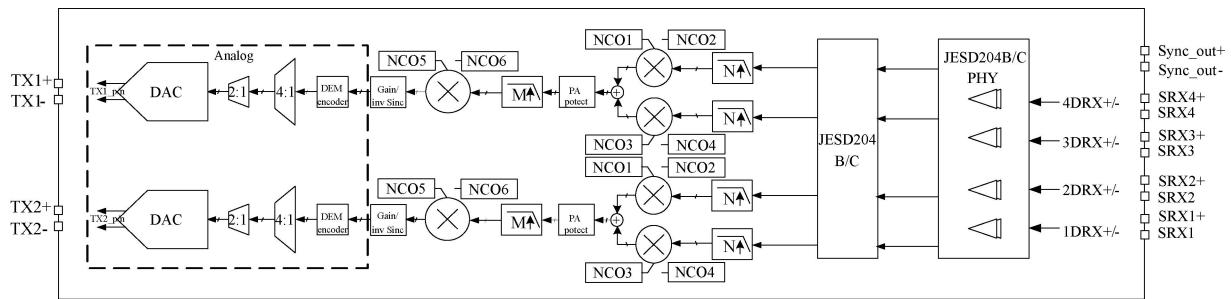

### 2.1 CX8242K 配置

CX8242K 是一款高集成度的国产宽带、射频直采收发器芯片。CX8242K 发射功能框图如图 2 所示。发射 DAC 链路支持 3X~96X 灵活可配置的插值滤波及 NCO 模块,集成 PA 保护模块,支持高达 1 200 MHz 瞬时信号带宽,集成调节范围大于 40 dB 的 DSA(数字信号衰减)模块,用于调节发射链路功率。CX8242K 数据通信接口支持 JESD204B/C,与传统的 LVDS 接口相比,JESD204C 直接与 FPGA 的 GTY 口相连,在大幅提升传输速率的同时,减少了 IO 的资源消耗<sup>[8]</sup>。

CX8242K 发射端内部寄存器配置可分为三大类:芯片一般配置及高速接口配置、数字信号处理配置、模拟端配置。

#### 1) 芯片一般配置及高速接口配置

该组配置主要包括芯片级配置以及 JESD204 相关配置。

芯片级配置主要包括 SPI 设置、TxPLL 设置等。SPI 设置地址为 0x700,低两位控制切换功能,设为 0x02 来控制 DAC0。TxPLL 共有四级分频器,需要根据参考时钟来源和接口速率来确定分频比,各级分频器地址为 F64[3:0],F62[7:4]。

JESD204 相关配置主要包括 JESD204B/C 模式选择、加扰及链路模式使能、数据路由选择等。地址 0x008 用于配置接口方式为 JESD204B/C。链路模式选择决定 JESD204C 链

图2 CX8242K发射功能框图

Fig. 2 CX8242K transmitter function block diagram

路参数,地址为0xD81。加扰及链路模式使能地址为0x50B,0x50B[3:1]用于选择链路模式,最低位为加扰使能控制位。JESD204接收的数据可根据寄存器配置进行灵活的路由,SERDES RX端接收到4条Lane数据,通过配置0xD02[7:0]将数据路由到JESD204C协议进行处理,输出8路data,通过配置0xD5A、0xD5B、0xD5C将8组data路由至不同的DUC模块。

## 2) 数字端配置

该组配置主要包括信号流内插及滤波器配置、NCO配置、数字增益控制等。发射通道共有两组发射滤波器,每组三级,且配置优先级依次降低。内插寄存器地址为0x703,本设计中,第一组滤波器被旁路掉,仅作通路使用,因此只需要配置0x703[3:0]来选自第二组的三级半带滤波器。

NCO配置模式包括上混频、下混频以及Bist模式,由0xA07[1:0]以及0xA08[2:0]联合控制。Bist模式输出NCO震荡的单音信号,可用于DEBUG测试。

数字增益调整由0xC31[3:0]、0xC32[7:0]控制,组成gain\_ctrl\_init[11:0],调整能量公式为:

$$\text{data\_out} = \text{data\_in} * \text{gain\_ctrl\_init}[11:0] / 2\,048 \quad (1)$$

根据输出功率要求可进行数字增益调整。

## 3) 模拟端配置

该组配置主要包括DAC采样率及模式配置。DAC采样时钟由基带锁相环频率合成器(BBPLL)提供,BBPLL共四级,寄存器地址为0xF5C[7:0]以及0xF5B[0]。在250 MHz参考时钟输入下,配置四级分频器技术分别为4、3、4、1,共48倍,可得到12 GHz的DAC采样时钟。计算得0xF5C为0x68,0xF5B为0x41。

DAC工作模式由0xF73[4]决定是否开启MIX模式,MIX模式下数据速率加倍。

## 2.2 发射链路频率规划

CX8242K作为接收端以1 GspS的IQ速率接收到来自FPGA的数字基带信号,理论上可以支持1 GHz带宽传输,但是为了满足高频段、大带宽采样输出的需求,需要对数字信号进行插值处理来提高信号采样率,但会导致频谱的周期延拓,因此需要使用低通滤波器来滤除带外频率成

分<sup>[9]</sup>,这一操作的代价是实际传输的带宽会低于理论带宽。

经过插值滤波后,对数字信号进行复数混频,以提高输出频率。由于数字域混频可以精确地处理IQ信号,因此能有效避免混频产生的镜像信号和本振泄露问题。

因此需要进行频率规划,规划的同时观测芯片在不同频点/功率、不同采样率情况下的杂散信号。以500 MHz步进划分频段,分别测量8、12 GspS采样率下各单音频点的无杂散动态范围(SFDR),扫宽为800 MHz。测量结果如表2所示。

表2 不同采样率下各频点SFDR

Table 2 SFDR at different frequencies at different sampling rates

| 频点/GHz | 8 GspS/dBc | 12 GspS/dBc |

|--------|------------|-------------|

| 0.4    | 62.3       | 71.2        |

| 0.9    | 65.1       | 70.4        |

| 1.4    | 59.8       | 68.7        |

| 1.9    | 56.4       | 67.2        |

| 2.4    | 63.7       | 64.7        |

| 2.9    | 62.4       | 62.5        |

| 3.4    | 60.9       | 61.4        |

| 3.9    | 1.4        | 59.8        |

| 4.4    | 57.8       | 58.7        |

| 4.9    | 56.1       | 58.9        |

| 5.4    | 60.4       | 54.4        |

| 5.9    | 64.2       | 3.2         |

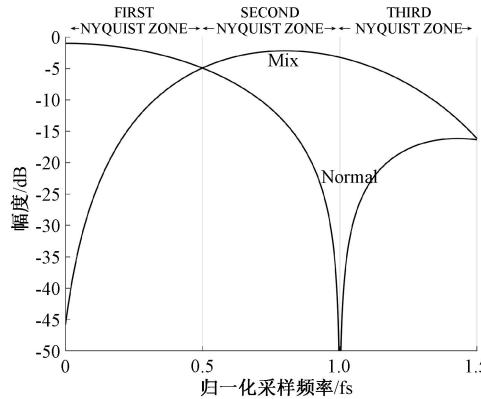

依据上述测量结果,将输出频率划分为10 MHz~5 GHz和5~6 GHz两个频段。CX8242K的最高DAC采样率为12 GspS,对应的奈奎斯特频率为6 GHz。对于10 MHz~5 GHz频段的信号,距离奈奎斯特频率较远,高频镜像功率较小且易于滤除。而对于5~6 GHz频段,由于靠近奈奎斯特频率,高频镜像谐波功率较大且靠近主信号,会对带内信号产生较大影响。因此,将DAC采样率调整为8 GspS,奈奎斯特频率变为4 GHz,通过将该频段置于第二奈奎斯特区,使其远离奈奎斯特频率来衰减镜像频

率。更改 CX8242K 模式为 MIX 模式,该模式下芯片会通过衰减第一奈奎斯特区功率和增大第二奈奎斯特区功率来优化信号在第二奈奎斯特区的输出响应<sup>[10]</sup>。DAC 两种模式下的功率衰减特征如图 3 所示。

图 3 不同模式 DAC 的衰减特征

Fig. 3 Attenuation characteristics of DACs in different modes

综上,对于 10 MHz~5 GHz 频段,使用 12 倍插值系数和 12 Gsp/s 的 DAC 采样率;对于 5~6 GHz 频段,使用 8 倍插值系数和 8 Gsp/s 的 DAC 采样率。该频率规划方案能够保障输出信号远离高频镜像,在各频段都有稳定频率及较低杂散。

### 3 FPGA 数字逻辑设计

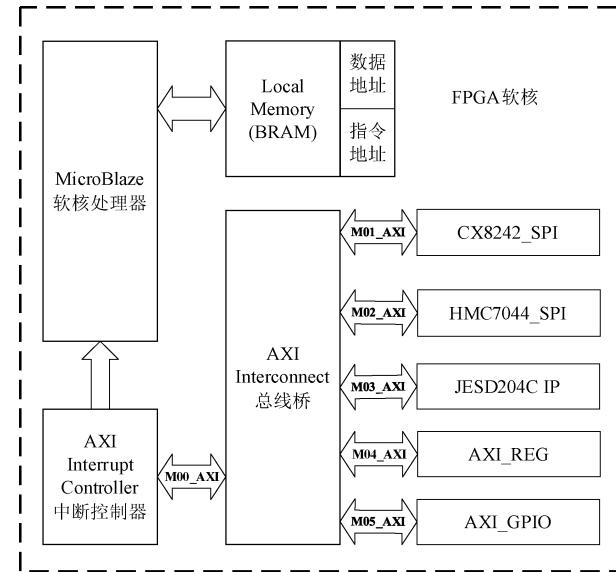

#### 3.1 MicroBlaze 及 AXI 总线互联模块设计

本设计选用 Xilinx 公司的 FPGA XC7U13P-FHGB2104,内嵌 MicroBlaze 软核处理器,通过 AXI-interconnect 总线桥实现 CPU 与各个外设之间的互联,所有外设的 IP 都需要挂在该总线桥上才能和 MicroBlaze 之间进行指令与数据传输。FPGA 软核设计框图如图 4 所示, MicroBlaze 处理器通过 AXI 总线与各种外设模块通信,M00\_AXI~M05\_AXI 接到各个模块,包括 SPI 接口模块、GPIO 模块等,从而控制和管理系统的整体功能<sup>[11]</sup>。

AXI Interrupt Controller 模块主要将 SPI、GPIO 等模块的中断指令进行整合,输入到 MicroBlaze 内核,然后由 MicroBlaze 内核统一调度和控制 SPI、GPIO 等模块的工作。开发者使用 SDK 软件编写 C 语言程序,编译指令缓存至内存空间 BRAM,CPU 访问内存获取指令驱动 SPI、GPIO 外设,完成对 CX8242K 以及 HMC7044 的配置。

CX8242K 提供了标准的三线和四线 SPI 接口用于配置芯片内部寄存器。通过 SPI 接口, MicroBlaze 处理器能够发送配置命令和数据来控制 CX8242K 的操作。设计采用四线 SPI,地址位为 12 bit,最高位标志标识类型,数据位为 8 bit。通过 AXI 总线的时钟四分频配置 SPI 时钟信号为 25 MHz,符合 CX8242K 芯片手册的 SPI 时序配置要求。

HMC7044 同样需要通过 SPI 接口来配置寄存器,通

图 4 FPGA 软核设计框图

Fig. 4 FPGA soft core design block diagram

过 M02\_AXI 总线与软核连接。JESD204C 以及 JESD204C\_PHY IP 核封装到一个 Block Design 中,通过 M03\_AXI 总线连接到 MicroBlaze 软核,方便 MicroBlaze 软核进行任务调度、数据交互和功能配置。此外,基带信号发生模块的关键信息,通过异步 FIFO 转换时钟域,存储在不同的 AXI\_REG 中,M04\_AXI 总线将其加载到 MicroBlaze 软核,方便后续在 SDK 软件中使用 Xil\_In32() 函数进行数据写入。AXI\_GPIO 模块通过 M05\_AXI 总线与软核连接,允许 MicroBlaze 处理器灵活配置和读取 GPIO 引脚的状态,从而控制和监控外部设备的操作。

通过内嵌 Microblaze 软核,充分利用硬件资源,降低硬件复杂度,使得整个系统架构更加简洁高效。提高系统的动态配置能力,实现对各模块的高效管理。

#### 3.2 JESD204C 接口逻辑设计

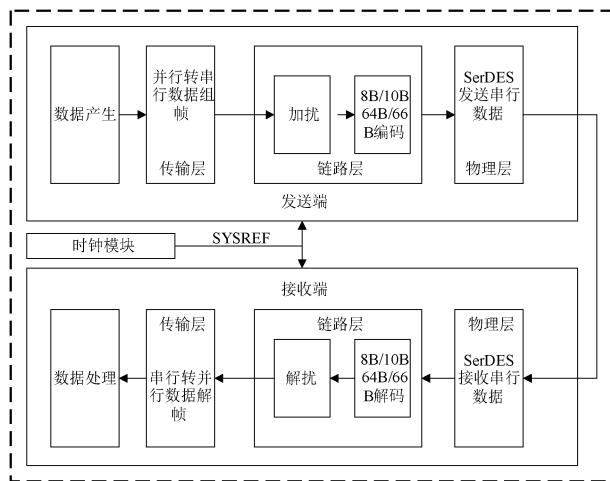

VU13P 系列 FPGA 具有丰富的 RAM 及 DSP 资源、高速 I/O 接口以及支持 JESD204C 的 GTY 资源,可以满足 JESD204C 协议传输需求。协议结构可分为传输层、链路层和物理层。传输层是收发端的第一部分,负责将转换样本映射为非加扰 8 位字节,并进行帧传输。发射端旨将多位样本数据转换成一系列非加扰 8 位字节,接收端旨在按照发射端的逆过程还原有效数据。链路层负责实现 FPGA 与转换器之间的链路初始化,包括 64B/66B 编解码、同步头对齐、扩展多块同步、扩展多块(通道)对齐以及数据传输<sup>[12]</sup>。物理层则按照设置好的线速率接收或发送字符。收发框图如图 5 所示。

##### 1) 传输层设计

传输层设计的难点在于数据链路的组帧映射。需要按照链路配置参数  $L, M, F, N, N'$  对数据进行组帧,表 3 是本设计支持的链路配置。

图5 JESD204C收发框图

Fig. 5 JESD204C transceiver block diagram

表3 支持的链路配置

Table 3 Supported link configurations

| Mode | L | M | F  |

|------|---|---|----|

| 0    | 1 | 2 | 8  |

| 1    | 2 | 2 | 4  |

| 2    | 1 | 4 | 16 |

| 3    | 2 | 4 | 8  |

| 4    | 4 | 4 | 4  |

| 5    | 1 | 8 | 32 |

| 6    | 2 | 8 | 16 |

| 7    | 4 | 8 | 8  |

其中, L 为链路数, M 为转换器数, F 为每一帧所包含的码组数, 每个码组 8 bits。

以 Mode 1 为例, N 和 N' 设置为 14 和 16, 对应 DAC 的 14 bit 精度, 配置了 lane 条数 L 为 2, 分别用于传输基带信号的 I 路和 Q 路数据。IQ 两路数据来源于 FPGA 内部的信号发生模块。首先由模块生成伪随机数序列作为基础数据源, 然后根据所需的调制类型对序列进行符号映射, 生成 I 路和 Q 路信号<sup>[13]</sup>。接着, 这些信号经过串并转换, 将串行数据转换为 4 路并行数据。随后, 4 路并行数据通过成型滤波器(如升余弦滤波器)进行滤波, 确保基带信号的频谱效率和传输质量<sup>[14]</sup>。最终, 经过成型滤波后的基带信号输出, 供系统后续的组帧和传输使用。

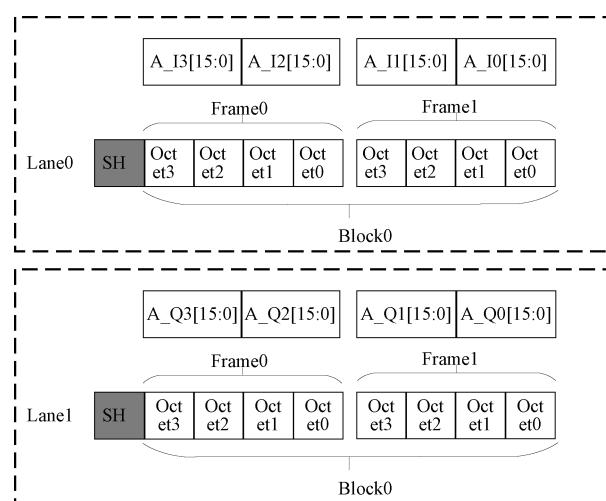

配置转换器个数 M 为 2, 每一帧包含的码组数 F 为 4, 每个码组 8 bits, 一个多块需要 8 个码组填充, 所以需要后续帧的 4 个码组进行填充, 即一个块(Block)可传输两帧 64 bits 数据。传输层数据组帧映射如图 6 所示。

## 2) 链路层设计

链路层的同步过程是实现 JESD204C 协议的重中之重, 难点在于多组数据流通过 JESD204C 的不同 Lane 传

图6 Mode1 数据组帧映射

Fig. 6 Mode1 data framing mapping

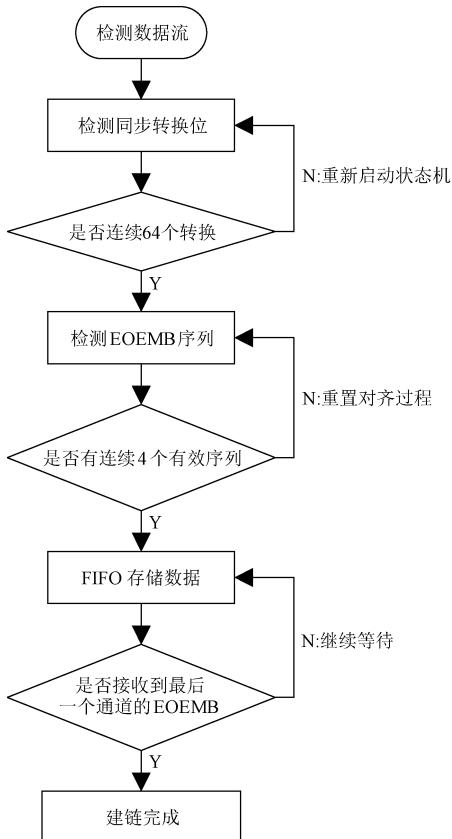

输, 需要各条 Lane 在传输过程中保持严格的时序一致。此外, 链路层还要精确捕捉到多个数据流的同步节点, 主要涉及 3 个阶段。首先是从同步头对齐开始, 接收端通过状态机检测 64/66 位之间的数据转换确定一个同步转换位, 当连续检测到 64 个连续转换, 实现同步头对齐锁定, 否则重启状态机。在实现同步头对齐后, 接收端在转换位中查找扩展多块结束(EOEMB)序列(100001), 一旦检测到 4 个连续有效序列, 就可以实现扩展多块结束锁定(EMB\_LOCK)。每个通道的接收缓冲区在接收到 EOEMB 最后一位后开始缓冲数据, 接收到最后一个接收通道 EOEMB 之后, 所有通道的缓冲区释放数据实现扩展多块(通道)对齐。

建链同步流程图如图 7 所示。

## 3) 物理层设计

物理层经 GTY 高速收发器将数据按照协议进行通过 SerDes 接口发送给 CX8242K, DAC 将数据进行解码解扰解串的一系列操作后, 再进行插值、滤波、混频后转换为射频信号输出。

将 JESD204C 接收端 CX8242K 配置为 Mode1, 即两个转换器(converter)和双链路(lane)模式。通过内置时钟倍频器将 DAC 采样率配置为 12 GHz, 其中 DAC0 和 DAC1 分别用来转换信号的 I 路和 Q 路。每个链路上的数据率:

$$\text{Lane Rate} = \frac{M \cdot N' \cdot F_s}{L \cdot A} \times \frac{66}{64} \quad (2)$$

其中,  $F_s$  为采样率, A 为插值滤波器值。

当  $F_s = 12 \text{ GHz}$ ,  $M = 2$ ,  $N' = 16$ ,  $L = 2$ ,  $A = 12$  时, 每个通道传输数据速率为:

$$\text{Lane Rate} = \frac{2 \times 16 \times 12 \text{ GHz}}{2 \times 12} \times \frac{66}{64} = 16.5 \text{ Gbps} \quad (3)$$

因此, 发射端 GTY 发射速率为 16.5 Gbps。将 FPGA JESD204C IP 核配置为发射端, 具体参数配置: 每帧字节数

图 7 建链同步流程图

Fig. 7 Chain building and synchronization flow chart

$F = 8$ , 多帧数  $K = 64$ , 链路数  $L = 2$ 。GTY 核的参考时钟为 250 MHz, 其线速率:

$$\text{Lane Rate} = 250 \text{ MHz} \times 64 \times \frac{66}{64} = 16.5 \text{ Gbps} \quad (4)$$

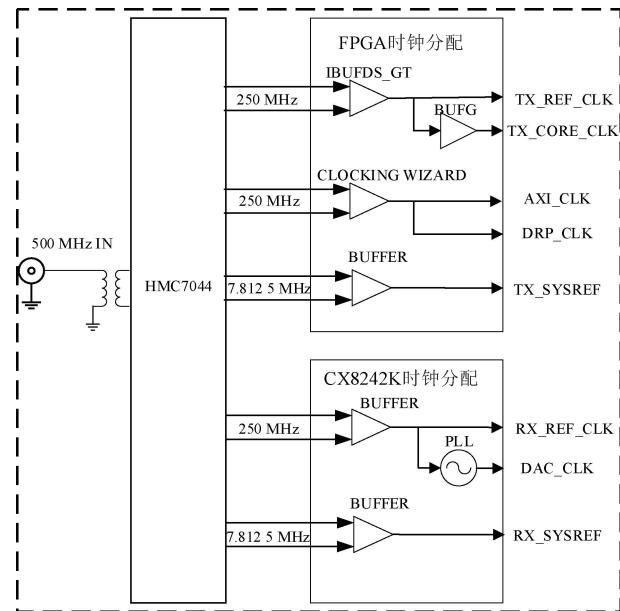

### 3.3 时钟方案设计

JESD204C 协议的高效数据传输依赖于精准的时钟同步机制, 抖动、时钟漂移等都会影响数据传输, 因此在设计时选用了一款高性能时钟管理芯片 HMC7044 来生成低抖动、低相噪的时钟信号。

设计所需的时钟包含以下几部分: 1) 与 CX8242K 内部采样及 NCO 相关的 Device Clock 和 SYSREF 时钟; 2) FPGA 的 JESD204C 接口相关的 Device Clock 和 SYSREF 时钟; 3) FPGA 相关的逻辑时钟和信号处理时钟<sup>[15]</sup>。

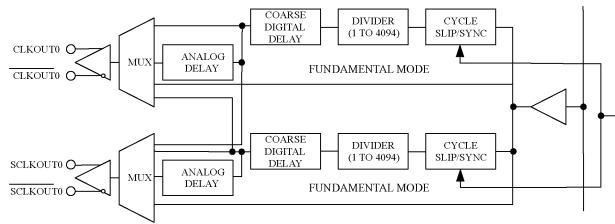

HMC7044 具有两级 PLL 和两个片内 VCO。第一级 PLL 主要是将质量较差的参考输入信号的噪声滤除, 为第二级 PLL 提供良好输入参考信号。由 PLL2 将其倍频至片内的 VCO 输出频率。此外, HMC7044 支持 14 路输出, 每路输出都可独立配置, 支持 1~4 096 倍分频输出, 支持本设计时钟需求。图 8 为 HMC7044 的通道功能框图, 其中 CLKOUT 为器件时钟输出, SCLKOUT 为 SYSREF 信号输出。每个通道均包含独立的分频器, 相位调整和模拟延迟电路。

图 8 HMC7044 通道框图

Fig. 8 HMC7044 channel block diagram

HMC7044 中内部压控振荡器 (VCO) 频率范围为 2.4~3.2 GHz, 对于 JESD 204C 相关的 GT 时钟 250 MHz, 需要对 VCO 频率进行 4 次划分才能满足 HMC7044 的分频系数要求。分频输出后连接到串行收发器的 MGTREFCLK 差分引脚, 经 GTY 专用的 IBUFDS\_GT 转为单端时钟作为 GTY 的 REFCLK。此外 FPGA 的系统时钟 250 MHz 作为差分信号输入经 clocking wizard IP 核分频为 100 MHz 单端时钟作为 AXI\_CLK 以及 DRP\_CLK。对于 SYSREF 同步参考时钟, 频率固定为 250 MHz 的 1/32, 因此在前面分频系数上乘 32 即可。

此外, 对于射频芯片的 12 GHz 采样时钟, 设计 HMC7044 单通道输出 250 MHz 时钟后由 CX8242K 内部 PLL 进行倍频产生。时钟分配方案如图 9 所示。

图 9 时钟分配方案

Fig. 9 Clock distribution scheme

借助 ADI 官方的提供 ADIsimCLK 工具以及 HMC704x\_GUI 软件配置参数, 生成 SPI 配置文件后, 由 MicroBlaze 软核进行 HMC7044 的控制。

### 3.4 发射通道同步设计

为了确保双通道输出的相位和幅度一致性, 需要做到以下 3 点: 首先要考虑 JESD204C 协议的收发同步时序要

求。通过使用HMC7044生成低抖动、低相位噪声的参考时钟SYSREF，并结合PCB等长布线，可以确保时钟相位一致以及4条SERDES通道的收发同步<sup>[16]</sup>。其次，需确保两路RF发射通道的上电一致性，这可以通过配置CX8242K内部寄存器实现同时上电。最后要做到DAC采样同步及本振和插值滤波的同步。PCB布局设计时，需考虑射频前端输出的等长布线，以保证双通道间各采样时钟的同频同相<sup>[17]</sup>。

#### 4 方案验证与分析

本设计的主要程序是在FPGA中实现的，并使用Xilinx公司提供的Vivado 2018.3开发套件进行程序开发。使用RIGOL的RSA5065系列频谱分析仪对信号的频谱特性进行验证与分析。

信号产生硬件平台如图10所示，在完成硬件平台的搭建后，将编译出的bit流文件以及硬件设计文件.hdf文件一起导入到SDK开发环境中。在SDK建立软件工程时，系统会自动识别硬件环境，并基于此生成板级支持包(BSP)作为驱动程序。

图10 硬件平台实物图

Fig. 10 Physical picture of the hardware platform

硬件环境搭建完成后，根据诚芯公司的CX8242K配置软件进行参数配置，主要包括RF DAC的采样频率、发射NCO频率、插值系数、时钟源选择、电源设置、SerDes等参数的配置，生成配置文件后在SDK中用C语言编写程序进行芯片调试。

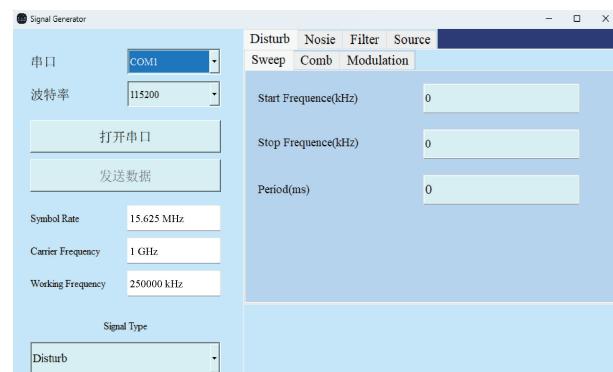

完成以上操作后，打开信号发生器上位机软件操作界面如图11所示。首先打开串口，选择串口类型，随后配置所需调制信号参数，主要参数包括成型滤波器类型、调制信号类型、滚降因子 $\rho$ 、符号率等。配置完成后，点击“发送数据”按钮。

实验所需测试的关键指标主要包括以下3点：1)输出频率范围以及信号纯净度；2)输出调制信号类型；3)JESD204C协议支持最大基带调制信号带宽。

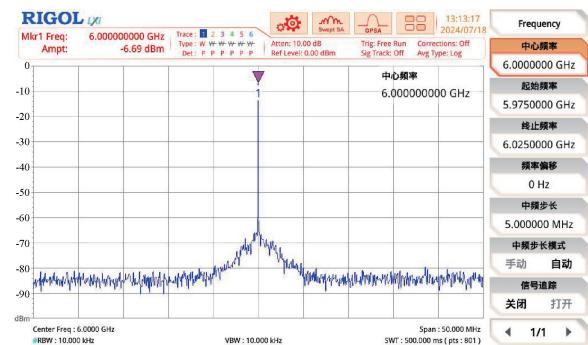

首先验证输出频率是否能够达到6GHz指标，配置发送信号类型为单音信号，NCO频率为6GHz，输出频谱图如图12所示。输出6GHz单音信号功率为-6.69dBm，

图11 上位机软件操作界面

Fig. 11 Upper computer software operation interface

图12 载波频率为6 GHz单音信号频谱图

Fig. 12 Spectrum of single tone signal with carrier frequency of 6 GHz

无杂散动态范围大约为80 dBc，达到指标要求。

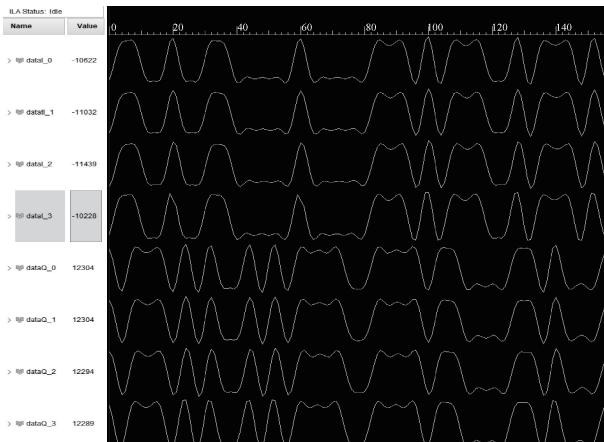

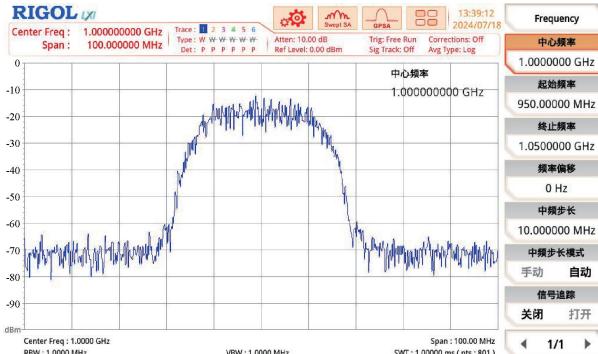

接着验证信号源能否发送各种所需调制信号。在上位机修改基带信号配置参数，更改调制信号类型为QPSK，符号速率为25Mbit/s，滤波器类型为升余弦滤波器，滚降因子 $\rho$ 设为0.5，则信号带宽约为符号速率的1.5倍。配置CX8242KNCO上混频1GHz，插值12倍，DAC采样率12GHz发射射频信号。图13为ILA(逻辑分析仪)抓取的发往DAC的四路并行IQ调制信号，图14为100MHz扫宽下输出载波频率为1GHz的QPSK信号频谱图，可以看出四路并行的IQ信号存在严格的相位关系，调制信号带宽约为32.5MHz，无杂散动态范围约为60dBc。

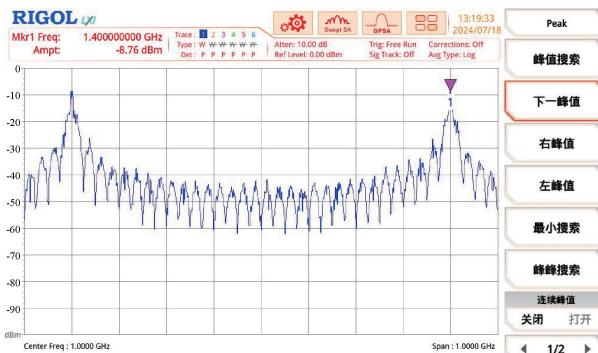

参数配置调制信号类型为2FSK，无成型滤波器，频偏设置为400MHz，符号速率为25Mbit/s，NCO为1GHz，图15为中心频率1GHz，扫宽1GHz下2FSK频谱图。

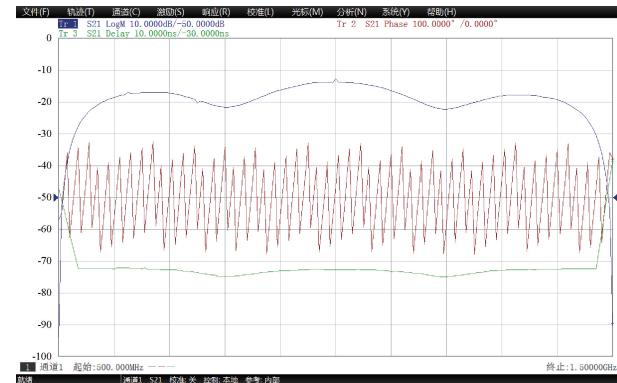

为验证系统是否支持800MHz调制带宽传输，采用AV3672B-S矢量网络分析仪进行收发回环测试，提供频段为500MHz~1.5GHz，功率为-5dBm的激励信号。通过CX8242K接收端的ADC进行1GHz的下变频，频段变为-500~500MHz送入FPGA，FPGA而后将该段基带信号通过DAC进行上变频1GHz发送出去。通过矢量网络信号分析仪测量S21(正向传输系数)。结果如图16所示。

图 13 FPGA 发往 CX8242K 的四路 I/Q 信号

Fig. 13 Four I/Q signals sent from FPGA to CX8242K

图 14 载波频率为 1 GHz 的 QPSK 频谱图

Fig. 14 QPSK spectrum with a carrier frequency of 1 GHz

图 15 载波频率为 1 GHz 的 2FSK 频谱

Fig. 15 2FSK spectrum with a carrier frequency of 1 GHz

图 16 测量 S21 三种格式,分别是 LogM(对数幅度),Phase(相位),Delay(群时延)。观察 S21 幅度谱,看到射频输出信号在 550~1 450 MHz 频段表现良好,由此得到上变频 1 GHz 之前的基带信号可支持频段范围为 -450~450 MHz,可传输带宽接近 900 MHz,达到输出指标 800 MHz。

通过对上述实验结果进行分析,可以得出信号源输出频谱杂散较低且符合 10 MHz~6 GHz 指标。FPGA 内部

图 16 回环测试 S21

Fig. 16 Loopback test S21

四路并行的方案可准确传输各种大带宽基带调制信号。JESD204C 协议可支持超 800 MHz 带宽的信号传输。

选取创远信科代表产品 T3661A 矢量信号发生器进行部分指标对比,得到表 4。

表 4 测试指标对比

Table 4 Comparison of test indicators

| 指标     | 本文设计的信号源               | T3661A 信号源            |

|--------|------------------------|-----------------------|

| 频率范围   | 10 MHz~6 GHz           | 1 MHz~12.75 GHz       |

| 最大带宽   | 800 MHz                | 500 MHz               |

| 调制类型   | 多种矢量调制<br>(QPSK、FSK 等) | 多种矢量调制<br>(ASK、FSK 等) |

| 多通道同步  | 支持双通道同步                | 不支持                   |

| 单音动态范围 | ≥80 dBc                | ≥60 dBc               |

可见本文设计的信号源相较于 T3661A 信号源在调制信号带宽、多通道同步、输出信号质量上有一定优势。

## 5 结 论

本文设计了基于 FPGA 与国产射频收发器 CX8242K 的矢量信号源并成功实现,经测试验证,该设备能正确生成用户所需的多种射频矢量调制信号,通过 JESD204C 接口可实现高达 800 MHz 的宽带信号传输,生成射频信号最高频段可支持 6 GHz,支持双通道同步,表现出良好的频率稳定性和信号纯净度,符合指标要求。解决了现有信号源设计中存在的带宽、同步和信号质量等技术难点,具有重要的工程应用价值。

## 参考文献

- [1] 尹康,罗义军.基于 FPGA 和 AD9364 的矢量信号源设计与实现[J].仪表技术与传感器,2021(5):67-71,86.

YIN K, LUO Y J. Design and implementation of vector signal source based on FPGA and AD9364[J]. Instrumentation Technology and Sensor, 2021(5): 67-71, 86.

- [2] 王鹏,毛开.矢量信号发生器实时动态衰落模块设计与

- 实现[J].国外电子测量技术,2022,41(5):96-102.

- WANG P, MAO K. Design and implementation of a real-time dynamic fading module for vector signal generators [J]. Foreign Electronic Measurement Technology, 2022, 41(5): 96-102.

- [3] 朱健,顾军,朱卫国.宽带频率捷变和复杂调制信号发生器的设计[J].电子测量技术,2019,42(2):52-57.

- ZHU J, GU J, ZHU W G. Design of wideband frequency agile and complex modulation signal generator[J]. Electronic Measurement Technology, 2019, 42(2): 52-57.

- [4] 王子樵,徐湛,陈晋辉,等.频控阵雷达多路相参信号源的设计与实现[J].电子测量技术,2020,43(3):11-16.

- WANG Z Q, XU ZH, CHEN J H, et al. Design and implementation of multi-channel coherent signal source for frequency-controlled radar array [J]. Electronic Measurement Technology, 2020, 43(3): 11-16.

- [5] 张春茗,杨添,严展科,等.基于6 Gsample/s 12 bit ADC接口控制层电路设计与实现[J].电子器件,2020,43(5):1142-1147.

- ZHANG C M, YANG T, YAN ZH K, et al. Design and implementation of interface control layer circuit based on 6 Gsample/s 12 bit ADC [J]. Electronic Devices, 2020, 43(5): 1142-1147.

- [6] LI SH J, MA R H, DENG M X, et al. A 312.5 Mbps~32 Gbps JESD204C wireline transceiver back-compatible with JESD204B in 28 nm CMOS[J]. Integrated Circuits and Systems, 2024, DOI: 10.23919/ICS.2024.3423852.

- [7] 马家麟,孙海洲,任贵珊,等.高集成度多种格式并行输出的视频测试信号源研制[J].电子测量与仪器学报,2022,36(3):217-223.

- MA J L, SUN H ZH, REN G SH, et al. Development of a high-integration video test signal source with multi-format parallel output[J]. Journal of Electronic Measurement and Instrumentation, 2022, 36(3): 217-223.

- [8] 张浩然,吴姿妍,赵晓龙,等.基于FPGA的宽带线性调频信号的产生与实现[J].激光与红外,2022,52(4):594-599.

- ZHANG H R, WU Z Y, ZHAO X L, et al. Generation and implementation of wideband linear frequency modulated signals based on FPGA [J]. Laser & Infrared, 2022, 52(4): 594-599.

- [9] 邵杰,万书芹,任凤霞.基于ASIC的并行流水线级联半带滤波器设计[J].固体电子学研究与进展,2020,40(1):60-65.

- SHAO J, WAN SH Q, REN F X. Design of parallel pipelined cascade half-band filter based on ASIC[J]. Research & Progress of Solid State Electronics, 2020, 40(1): 60-65.

- [10] 赵禹,叶芃,孟婕,等.基于带宽交织采样架构的80 GSps超宽带实时采集系统[J].仪器仪表学报,2024,45(5):147-156.

- ZHAO Y, YE P, MENG J, et al. 80 GSps ultra-wideband real-time acquisition system based on bandwidth interleaving sampling architecture [J]. Chinese Journal of Scientific Instrument, 2024, 45(5): 147-156.

- [11] 杜建平,李震.基于Microblaze与FPGA的总线通信[J].信息系统工程,2014,27(9):19-20.

- DU J P, LI ZH. Bus communication based on microblaze and FPGA [J]. Information Systems Engineering, 2014, 27(9): 19-20.

- [12] 王国栋.JESD204C时钟电路和传输层电路设计[D].南京:东南大学,2022.

- WANG G D. Design of JESD204C clock circuit and transmission layer circuit [D]. Nanjing: Southeast University, 2022.

- [13] 陈建斌,王刚,吴毅杰,等.GMSK多通道接收机的非相干解调算法及FPGA实现[J].无线电通信技术,2023,49(4):746-752.

- CHEN J B, WANG G, WU Y J, et al. Non-coherent demodulation algorithm and FPGA implementation of gmsk multi-channel receiver [J]. Radio Communication Technology, 2023, 49(4): 746-752.

- [14] 李浩,王厚军,肖磊,等.高速并行数字调制信号的产生与实现[J].仪器仪表学报,2023,44(2):110-118.

- LI H, WANG H J, XIAO L, et al. Generation and implementation of high-speed parallel digital modulation signals[J]. Chinese Journal of Scientific Instrument, 2023, 44(2): 110-118.

- [15] 蒋文吉,汪若愚.一种基于AD9371的8通道射频数据采集电路设计[J].电子信息对抗技术,2022,37(2):87-90.

- JIANG W J, WANG R Y. Design of 8-channel RF data acquisition circuit based on AD9371 [J]. Electronic Information Countermeasure Technology, 2022, 37(2): 87-90.

- [16] 王松明.基于JESD204B标准的多通道数据同步传输设计[J].现代雷达,2019,41(8):60-64.

- WANG S M. Design of multi-channel data synchronous transmission based on JESD204B standard[J]. Modern Radar, 2019, 41(8): 60-64.

- [17] 赵昇翔,何岷,贺志毅,等.一种相控阵雷达多通道同步方法[J].现代防御技术,2022,50(1):60-66.

- ZHU SH X, HE M, HE ZH Y, et al. A multi-channel synchronization method for phased array radar [J]. Modern Defense Technology, 2022, 50(1): 60-66.

## 作者简介

何冉,硕士研究生,主要研究方向为高速数据传输,射频芯片开发。

E-mail:h2239662383@163.com

李鹏(通信作者),教授,博士,主要研究方向为数字信号处理、通信系统。

E-mail:peng.li@nuist.edu.cn

冯姣,博士,副教授,主要研究方向为无线通信、信道仿真。

E-mail:jiao.feng@nuist.edu.cn