DOI:10.19651/j.cnki.emt.2416254

# 基于 FPGA 的多接口视频编解码系统<sup>\*</sup>

郑慧捷 吕庆丰 朱志行 邑翔 阎超波

(河海大学信息科学与工程学院 常州 213200)

**摘要:**为进一步提高机器视觉系统的兼容性以及丰富编解码系统处理的视频格式种类,设计了基于FPGA的多接口视频编解码系统。利用异步DDR读写的原理构建编解码选择模块,完成不同视频格式的转换操作,最终系统支持PAL、HDMI、Cameralink视频的解码以及HDMI、Cameralink、LVDS视频的编码功能,同时通过对比不同视频接口的传输特性,实现了上述几种视频接口标准之间的无缝转换。该系统不仅可以作为独立的视频编解码系统,还可以通过LVDS接口连接ARM处理器,从而扩展其应用场景。实验结果表明,系统能够准确解码分辨率为 $720\times576$ 的PAL视频、分辨率为 $640\times512$ 的Cameralink视频以及分辨率为1080p的HDMI视频,并且能够通过HDMI、Cameralink、LVDS视频接口分别输出,此外,系统的各类资源消耗均未超过50%,确保了系统的高效运行。

**关键词:**多接口;视频编解码;FPGA;格式转换

中图分类号: TN91 文献标识码: A 国家标准学科分类代码: 510.4

## Multi-interface video codec system based on FPGA

Zheng Huijie Lyu Qingfeng Zhu Zhixing Yi Xiang Min Chaobo

(College of Information Science and Engineering, Hohai University, Changzhou 213200, China)

**Abstract:** In order to further improve the compatibility of machine vision systems and enrich the types of video formats processed by encoding and decoding systems, a multi interface video encoding and decoding system based on FPGA was designed. By using the asynchronous DDR read-write principle to build the codec selection module and complete the conversion operation of different video formats, the final system supports the decoding of PAL, HDMI and Cameralink videos as well as the encoding functions of HDMI, Cameralink and LVDS videos. Meanwhile, by comparing the transmission characteristics of different video interfaces, the seamless conversion between the above video interface standards is realized. The system can not only be used as an independent video codec system, but also can be connected to ARM processor through LVDS interface, thus expanding its application scenarios. Experimental results show that the system can accurately decode PAL video with a resolution of  $720\times576$ , Cameralink video with a resolution of  $640\times512$  and HDMI video with a resolution of 1080p, and then output it through HDMI, Cameralink and LVDS video interfaces respectively. In addition, the consumption of all kinds of resources in the system does not exceed 50%, which ensures the efficient operation of the system.

**Keywords:** multi-interface; video codec; FPGA; format conversion

## 0 引言

视频图像是获取外界信息的最重要方式之一<sup>[1]</sup>。随着视频质量的不断提高,视频图像数据量越来越大,图像处理系统涵盖了众多可满足不同应用场景的视频接口,视频格式的种类也在不断增加<sup>[2]</sup>。但是由于高级精简指令集机器(advanced reduced instruction set computer machines, ARM)、数字信号处理器(digital signal processor, DSP)等

核心处理器受硬件资源限制以及算法复杂性影响,目前多数机器视觉系统的通用视频接口<sup>[3]</sup>有限,需要编解码系统提高其兼容性。

多接口视频编解码系统在国防建设、民用领域和医疗领域都具有广泛的应用<sup>[4]</sup>。例如,在智能监控领域,多接口编解码系统可以实现对多种监控摄像头的视频格式进行统一处理和分析;在自动驾驶领域,支持多种传感器的视频数据输入和处理,提高车辆的感知能力;在医疗影像领域,能

够实现多种医学影像格式的快速转换和处理,辅助医生进行准确的诊断和治疗。现有的编解码系统具备的接口方式单一,将几种通用视频接口集成为一体的系统比较稀少,难以同时适用于各种编解码场景,因此对多接口视频编解码系统的研究日益迫切。张海平<sup>[5]</sup>提出了一种基于现场可编程门阵列(field programmable gate array, FPGA)的多接口实时视频处理系统,完成了 PAL(phase alteration line)/NTSC(national television system committee) 模拟视频图像的输入,将输入的图像分别通过 CameraLink 接口、VGA(video graphics array)接口和 PAL/NTSC 视频接口输出,但此系统只支持 PAL/NTSC 视频的输入,无法处理其他接口形式的视频输入。Latinovic<sup>[6]</sup>于 2022 年设计了一种信号处理平台,兼容 HD-SDI(high definition serial digital interface),CameraLink 和模拟复合 PAL 接口视频输入,但是平台仅支持以太网编码输出。

鉴于上述情况,考虑到 FPGA 并行处理能力强<sup>[7]</sup>、图像处理速度快且灵活可编程<sup>[8]</sup>等特点,本文设计了一种基于 FPGA 的多接口视频编解码系统。本文贡献如下:系统支持三种视频格式的输入:PAL、CameraLink、HDMI(high definition multimedia interface),以及 3 种视频格式的输出:CameraLink、HDMI、LVDS (low-voltage differential signaling),丰富了编解码系统适配的输入输出视频接口类型,兼容性较强;此外,本系统还可以完成输入和输出  $3 \times 3$  视频格式之间的任意无缝转换。系统不仅可以传输通用格式的视频流,还可以输出自定义的 LVDS 视频数据,便于与一些嵌入式系统兼容,例如 ARM 处理器,拓展了机器视觉系统的应用场景。

## 1 系统硬件设计

### 1.1 硬件设计

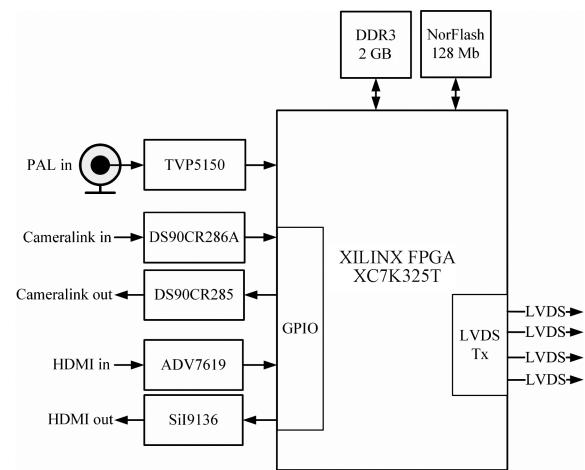

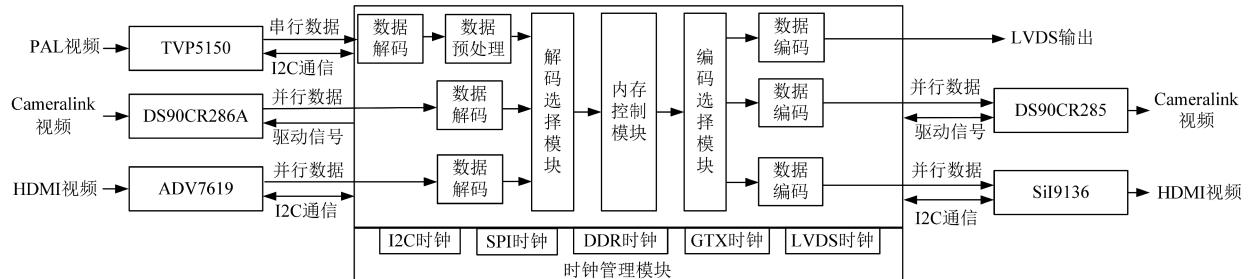

多接口视频编解码系统实现的是 PAL、HDMI、CameraLink 和 LVDS<sup>[9]</sup> 接口的解码与编码,并且能完成任意两种接口类型之间的转换。根据功能要求,系统的硬件框图如图 1 所示,主要包括 FPGA 模块设计、电源模块设计、按键控制模块设计、视频输入模块设计和视频输出模块设计。

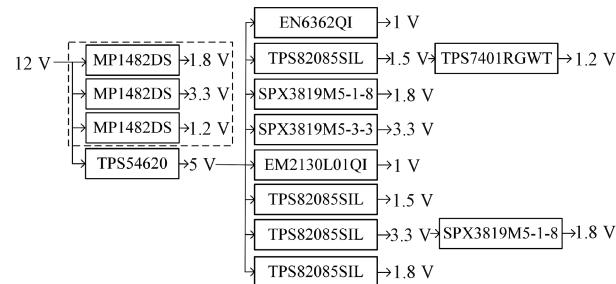

#### 1) 电源树设计

不同的模块需要不同的电压进行供电,同一模块的不同电源引脚可能也需要不同的电压进行供电<sup>[10]</sup>,因此要对电源进行设计。系统整体使用 12 V 电压供电,之后使用不同的电源芯片进行电压转换确保各个模块稳定运行。电源树设计如图 2 所示。

虚线框内的电源转换用来给编解码模块供电。使用同步降压稳压器 MP1482D 将 12 V 分别降为 1.8 V、3.3 V、1.2 V,最大电流均为 2 A。其中,1.8 V 电压给 PAL 解码芯片和 HDMI 解码芯片供电,3.3 V 给 PAL 解码芯片、HDMI 编解码芯片、CameraLink 编解码模块均提供电压,1.2 V 用来给 HDMI 编码芯片供电。

图 1 系统硬件框图

Fig. 1 System hardware block diagram

图 2 电源树设计

Fig. 2 Power tree design

虚线框外的电源树设计给 FPGA 供电。首先使用同步降压转换器 TPS54620 将 12 V 转换为 5 V,支持电流 6 A。之后 5 V 的电压通过 TPS82085SIL 电源芯片分别转换为 1.5 V、3.3 V、1.8 V,最大电流为 3 A。其中 1.5 V 电源不仅给 DDR 供电,还经过 TPS7401RGWT 转换成 1.2 V 给 FPGA 供电,3.3 V 电压经过 SPX3819M5 芯片转成 1.8 V 给 FPGA 供电。其他由 5 V 转成的 1 V、1.8 V、3.3 V、1.5 V 则直接供 FPGA 使用。

#### 2) 视频输入接口驱动

PAL 视频接口传输的是模拟信号,FPGA 处理的是数字信号<sup>[11]</sup>,经过 TVP5150 模数转换器的处理,输出的 8 位 YCbCr 4 : 2 : 2 格式的 ITU-R BT. 656 数据可以传输至 FPGA 处理。TVP5150 的 IO 口电压为 3.3 V,本文将 FPGA 的 Bank14 供电电源设置为 3.3 V 与其相连。此外,针对模拟电源 1.8 V 和数字电源 1.8 V、3.3 V 同时接入产生的电磁干扰,使用 II 型滤波器进行隔离。

HDMI 视频输入接口采用 1.4 A 标准与 TYPE-A 型插座,为了统一视频数据输入的格式,输入 FPGA 的视频数据需要是 YCbCr 格式。选用 ADV7619 进行 HDMI 的解码,它支持 HDMI 1.4 A 标准,只使用 16 个输出引脚,其他引脚则设置为高阻态。它的 IO 工作电压为 3.3 V,与

FPGA 的 Bank15 连接, 可以将外部设备输入的 HDMI 信号转换为 RGB、YCbCr 和 DTV 格式的视频信号。

Cameralink 视频输入接口采用 Base 模式, 该模式一共传输 4 路 LVDS 串行差分数据和 1 路 LVDS 的差分时钟信号<sup>[12]</sup>, 而 FPGA 的 I/O 接口标准是 LVCMOS 或者是 LVTTL, 因此需要使用转换芯片。高速解串器 DS90CR286A 的工作电压为 3.3 V, 与 FPGA 的 BANK16 相连接, 可以将四对 LVDS 数据流转换为并行的 28 位 LVCMOS 数据, 输出给 FPGA。

### 3) 视频输出接口驱动

HDMI 输出接口严格遵循 1.4 A 标准, 采用的是最小化传输差分信号 (transition minimized differential signaling, TMDS) 技术<sup>[13]</sup>。Si9136 是 HDMI 的编码发射芯片, 可以将 FPGA 输出的视频数据高效地转换为 TMDS 格式的视频数据, 并且通过 HDMI 接口输出。

Cameralink 视频输出接口采用 Base 模式, 使用 LVDS 信号传输, 传输速率为 2.04 Gb/s。高速串行器 DS90CR285 可以将 28 位 LVCMOS/LVTTL 视频数据转换为 4 对 LVDS 数据流, 进而通过 Cameralink 接口输出显示。由于 DDR (double data rate synchronous dynamic random access memory) 缓存的视频格式为 YCbCr, 只需要连接 16 位视频数据信号, 其余 8 位引脚设为高阻态。

LVDS 接口是一种低电压差分信号传输技术接口, 它只完成接口的时序转换, 而不处理图像的数据格式。该接口可以将解码后的视频数据发送到 ARM 处理器进行复杂的图像处理。本系统实现的是 LVDS 接口与海思 Hi3559 处理器之间的数据传输, 需要将 LVDS 配置成一对差分时钟和四条 Lane 的模式以便实现与 Hi3559 的数据交互。

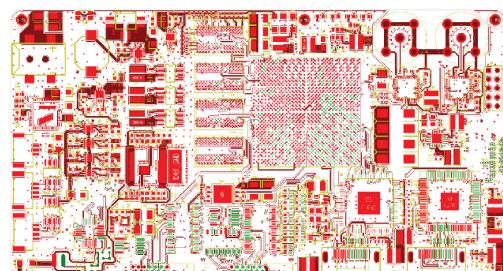

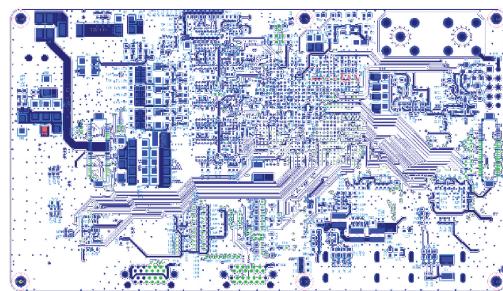

## 1.2 系统电路板

基于上述电源模块的设计以及对视频输入输出芯片的统筹规划, 完成了如图 3(a)所示的印制电路板 (printed circuit board, PCB) 顶层布局布线图和图 3(b)所示的 PCB 底层布局布线图。根据布局布线图制板之后得到了如图 4 所示的系统实物图。图 4(a)展示的是系统的俯视图, 图 4(b)展示的是系统的仰视图。在图 4(a)中可以看出, FPGA 芯片位于电路板中间, FPGA 芯片下方左侧两个接口是 Cameralink 输入和输出接口, 右侧两个接口是 HDMI 输入输出接口, 电路板左下角白色的接口是 PAL 输入接口。图 4(b)中位于左右两边的两个板对板夹层连接器是 LVDS 的输出接口。

## 2 多接口视频格式切换逻辑设计

### 2.1 基于异步 DDR 读写的视频格式切换

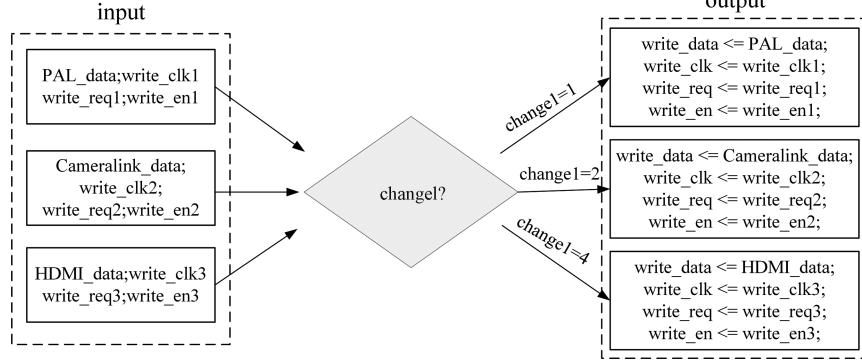

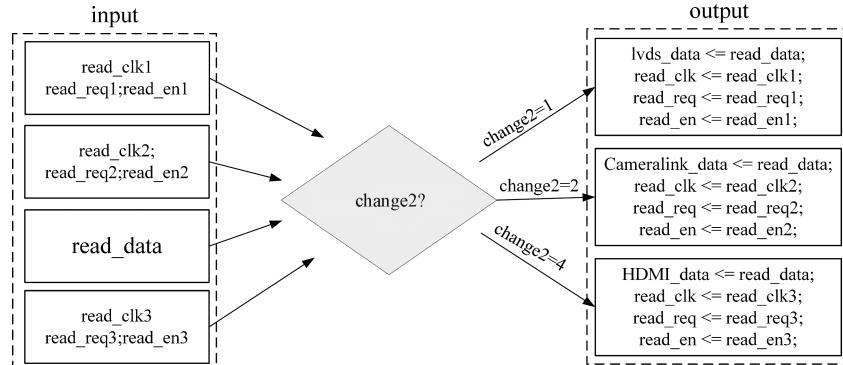

不同视频格式之间的转换通过编码选择模块和解码选择模块实现, PAL、HDMI、Cameralink 接口输入的 3 种视频经过解码处理均变成相同的数据格式, 便于编解码选择模块进行选择以及进入 DDR 缓存。视频格式切换原理如

(a) PCB 顶层布局布线

(a) PCB top layer layout and routing

(b) PCB 底层布局布线

(b) PCB bottom layer layout and routing

图 3 FPGA 板卡布局布线图

Fig. 3 FPGA board layout and routing diagram

(a) 电路板俯视图

(a) Top view of the circuit board

(b) 电路板仰视图

(b) Bottom view of the circuit board

图 4 系统实物图

Fig. 4 Physical diagram of the system

图 5 所示。由图 5 可知具体切换原理为: 根据外部设备输入的视频接口, 用户通过按键切换数据信号, 选择 PAL、HDMI、Cameralink 三种视频输入中任意一种解码后的数据, 将这个数据经由 DDR 缓存传输至编码选择模块。编码选择模块同样使用按键选择编码方式, 将读出的视频数据

编码成 LVDS、HDMI 和 Cameralink 三种视频格式中的任意一种格式输出。

图 5 视频格式切换原理示意图

Fig. 5 Schematic diagram of video format switching principle

其中,解码选择模块和编码选择模块是三选一的多路

图 6 解码选择器工作原理

Fig. 6 Working principle of the decoder selector

由图 7 可以看出,编码选择模块输入端包括 LVDS、HDMI、Cameralink 三种视频格式的读时钟 read\_clk, 读请求 read\_req 以及读使能 read\_en, 此外, 输入端的读数据 read\_data

图 7 编码选择器工作原理

Fig. 7 Working principle of the encoder selector

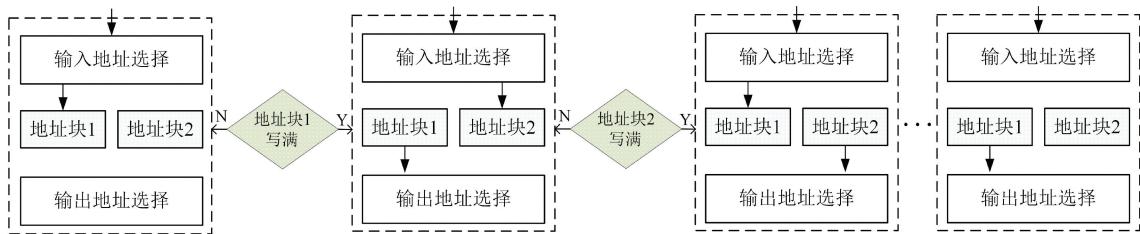

值得注意的是,DDR 的读端和写端是异步的,这样视频数据的解码和编码是互不影响的,便于编解码操作的独立进行,但由于读写速度的不一致,会造成帧交错的现象。为此,本文设计了乒乓操作<sup>[14]</sup>来避免帧交错的发生,乒乓操作的原理如图 8 所示。

在进行视频数据缓存时,将 DDR3 划分出两个地址块,解码后的数据首先写入地址块 1,同时输入地址选择模块对数据进行计数。当写满一帧时,地址标志位翻转,数据开始写入地址块 2,此时,输出地址选择模块开始从地址块 1 读数据。接下来判断地址块 2 是否写满一帧,若是,地

址标志位翻转,数据开始写入地址块 1,输出地址选择模块从地址块 2 读数据,若否,则继续保持上面的状态直到地址块 2 写满,如此循环。这样的乒乓操作保证了视频数据的高效稳定正确的传输。

## 2.2 系统总体逻辑

根据异步 DDR 读写的视频格式切换原理,设计了如图 9 所示的系统总体逻辑,由 7 个关键模块组成,分别是时钟管理模块、芯片配置模块、解码选择模块、编码选择模块、视频输入模块、视频输出模块和内存控制模块。这些模块共同实现了多接口视频编解码系统的功能。

图 8 乒乓操作原理示意图

Fig. 8 Schematic diagram of the Ping-Pong operation principle

图 9 系统总体逻辑功能设计图

Fig. 9 Overall logical function design diagram of the system

每一种视频接口的输入首先通过相应解码芯片的处理得到统一格式的有效数据,再经过解码选择模块进入内存控制模块进行缓存,之后利用编码选择模块选择编码方式输出显示。最终实现了 3 种视频格式输入、3 种视频格式输出中任意两种格式之间的视频格式切换操作。

## 2.3 视频编码和解码

### 1) PAL 视频解码

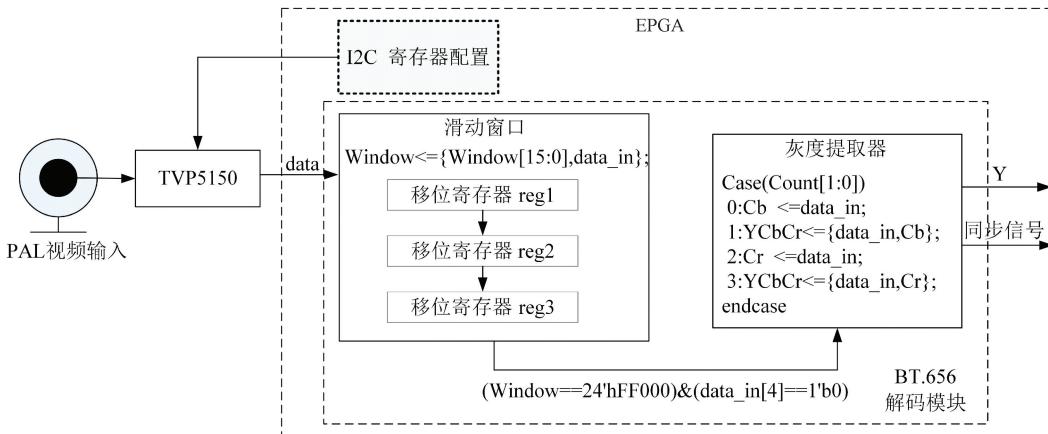

PAL 制视频信号<sup>[15]</sup> 经过 TVP5150 的处理,输入的模

拟视频信号转换为 8 位 YCbCr 的 BT.656 信号,并且隔行输出,同时提供同步信号。图 10 展示了 BT656 视频的解码逻辑。它利用滑动窗口的方法,在解码时,当检测到前 3 个移位寄存器中的值分别为 0xff、0x00 和 0x00 时,解码器会进一步检查数据的第 4 位,如果这一位的值为 0,那么解码器就会识别出起始码 SAV,否则表示结束码 EAV 到来。之后利用灰度提取器区分灰度信号 Y 与色度信号 Cb、Cr,并生成同步信号。

图 10 BT656 视频解码逻辑框图

Fig. 10 Logical block diagram of BT656 video decoding

解码之后的数据需要进行去隔行<sup>[16]</sup> 操作,使用插值算法来实现。通过地址切换信号实现奇偶场地址的变换,系统在初始状态时,地址切换信号的值为 0,当奇场图像数据全部写入之后,地址切换信号翻转为 1,接下来的数据则被写入偶场地址,最终显示的是一幅完整连贯的图像。

### 2) HDMI 视频解码和编码

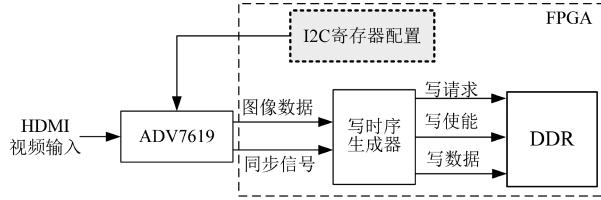

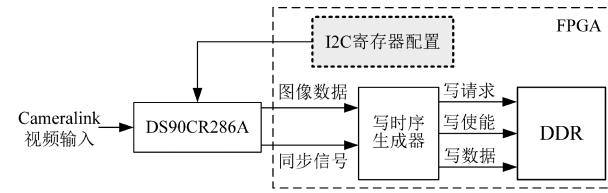

HDMI 视频的解码逻辑如图 11 所示。为了统一视频数据解码后的格式,对 ADV7619 进行集成电路总线 (inter-integrated circuit, I2C) 寄存器配置,使其输出单边沿为 YCbCr4 : 2 : 2 的视频数据。根据 ADV7619 输出的

图像数据和同步信号生成写时序来向 DDR 写入图像数据。同步信号包括帧同步信号 vs, 行同步信号 hs 以及数据有效信号 de, 当写时序生成器检测到 vs 的上升沿, 就会向 DDR 发送写请求, 随后根据写使能信号向 DDR 写入数据。

图 11 HDMI 视频解码逻辑框图

Fig. 11 Logical block diagram of HDMI video decoding

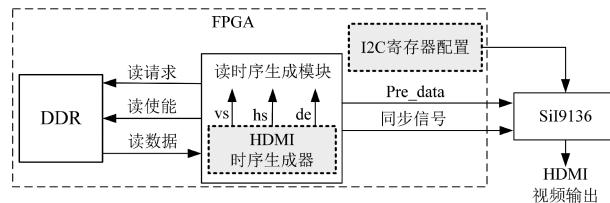

HDMI 视频的编码逻辑如图 12 所示, 首先由读时序生成模块根据 vs 信号生成读请求发送给 DDR, 其中 HDMI 时序生成器利用计数器的原理产生 HDMI 时序, 然后按照 HDMI 时序读出的数据以及同步信号 vs、hs、de 被传送到 SiI9136 编码芯片。此外, 还需通过 I2C 总线对 SiI9136 的寄存器进行配置以接收 YCbCr 格式的信号。

图 12 HDMI 视频编码逻辑框图

Fig. 12 Logic block diagram of HDMI video encoding

### 3) Cameralink 视频解码和编码

Cameralink 相机选用 base 模式输入图像数据, 数据包括 8 位灰度视频图像数据和 3 路同步信号。Cameralink 视频的解码逻辑如图 13 所示。首先 DS90CR286A 的第 25 引脚被拉高以启动转换器, 得到 28 位 LVCMOS 并行数据, 包括 24 位 RGB 信号和 4 路同步信号, 由于视频输入采

用的是灰度相机, 24 位 RGB 信号中只有 8 位用于表示灰度信息。之后写时序生成器接收并行数据, 产生向 DDR 写入的写请求, 最后生成写使能向 DDR 写入图像数据。

图 13 Cameralink 解码逻辑框图

Fig. 13 Logic block diagram of Cameralink decoding

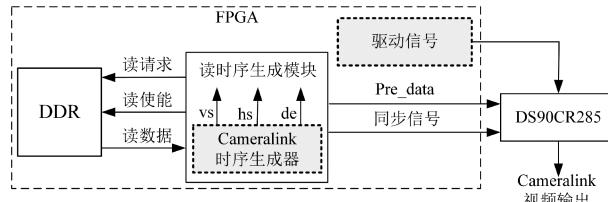

Cameralink 视频的编码逻辑如图 14 所示。首先由读时序生成模块根据 Cameralink 的时序信号生成读时序, 其中 Cameralink 时序生成器利用计数器的原理, 生成 vs、hs、de 信号。然后 DDR 中的数据按照 Cameralink 视频时序被读出。最后读出的数据被传输到 DS90CR285 编码芯片, 将芯片的第 32 引脚设置为高电平以启动编码操作。

图 14 Cameralink 视频编码逻辑框图

Fig. 14 Logic block diagram of Cameralink video encoding

### 4) LVDS 视频编码

为了本系统更好的连接 Hi3559 处理器等后端开发平台, 系统包含 LVDS 输出接口。在逻辑设计中需要将内存控制模块读出的并行数据转换成 LVDS 高速串行信号输出, 解码的关键在于同步码的插入。系统采用的 LVDS 同步码格式如表 1 所示, 特殊码型 SOF 和 EOF 分别标识帧的开始和终止, SOL 和 EOL 分别代表行的起始和结束, 它们由 4 个字段组成, 其中前 3 个字段为固定的基准码, 最后一个字段用于区分帧/行的起始或结束。

表 1 LVDS 同步码格式

Table 1 LVDS synchronization code format

| 字序     | 位宽    | 同步码     |         |         |         |

|--------|-------|---------|---------|---------|---------|

|        |       | SOL/SAV | EOL/EAV | SOF/SAV | EOF/EAV |

| 第 1 个字 | 8 bit | FFh     | FFh     | FFh     | FFh     |

| 第 2 个字 | 8 bit | 00h     | 00h     | 00h     | 00h     |

| 第 3 个字 | 8 bit | 00h     | 00h     | 00h     | 00h     |

| 第 4 个字 | 8 bit | 80h     | 9Dh     | ABh     | B6h     |

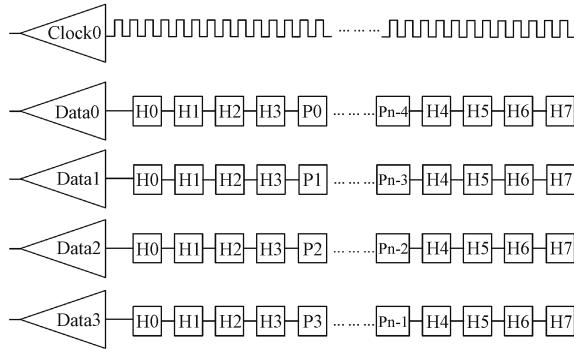

为了能够更精确的区分视频帧的各个部分, 保证数据的正确性, 系统使用 SOF 和 EOF 分别标记有效像素数据的第一行起始和最后一行的结束, 用 SOL 和 EOL 分别标

记无效数据区域的起始和结束。系统采用 4 个 Lane 传输视频数据, LVDS 同步码和像素数据分布在各个 Lane 上, 具体传输方式如图 15 所示。其中, H 是同步码, P 是像素。

H 和 P 的位宽与图像传感器输出单个像素的位宽一致。这种传输方式保证了像素数据的准确性。

图 15 LVDS 同步码传输模式

Fig. 15 LVDS synchronization code transmission mode

进行 LVDS 编码时,首先同步码嵌入器生成符合 LVDS 传输协议的 vs、de 和 8 位同步码,读时序生成模块根据 vs 信号产生读请求并发送到 DDR。随后发送读使能,确保从 DDR 读出的数据中同步码被准确嵌入。接下来将读取的数据实施拆分处理,使之均匀分散到 4 条 Lane。

### 3 实验分析与应用

系统实验所用设备及环境如图 16 所示。其中,带有 Cameralink 视频采集卡的主机用来完成 Cameralink 视频

图 16 系统验证环境

Fig. 16 System verification environment

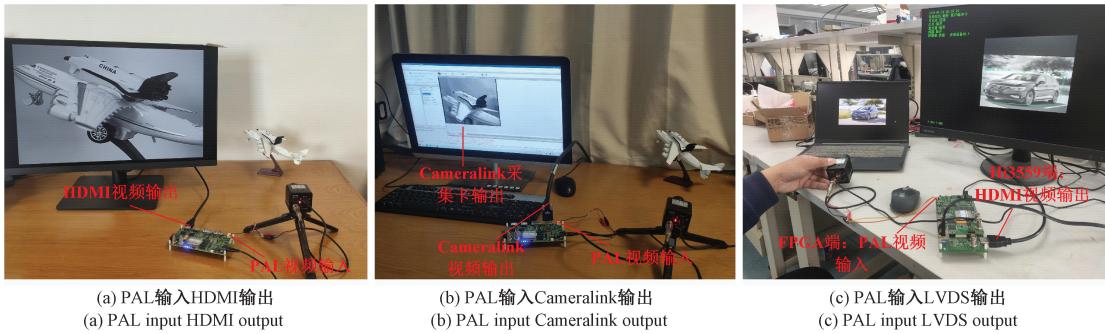

#### 3.1 视频格式切换功能验证

##### 1) PAL 视频解码

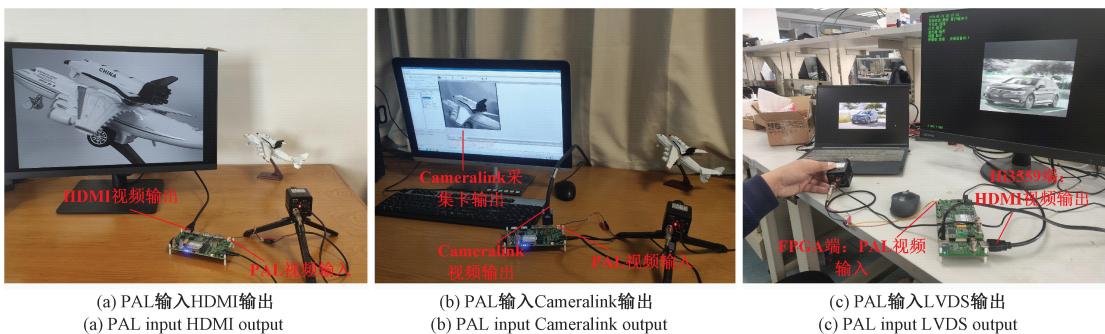

在进行 PAL 视频的解码操作时,使用的是灰度相机。将采集的视频接入 PAL 接口,再分别用 HDMI、Cameralink 以及 Hi3559 端视频输出接口显示,解码效果如图 17(a)~(c) 所示。

图 17 PAL 解码效果图

Fig. 17 Effect of PAL decoding

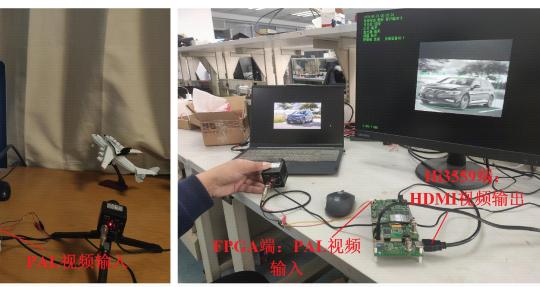

##### 2) 基于 HDMI 输出的视频格式切换

HDMI 视频编码时,分别选用了 PAL 输入接口、HDMI 输入接口以及 Cameralink 输入接口作为多元化的视频源,HDMI 输出效果如图 18(a)~(c) 所示。

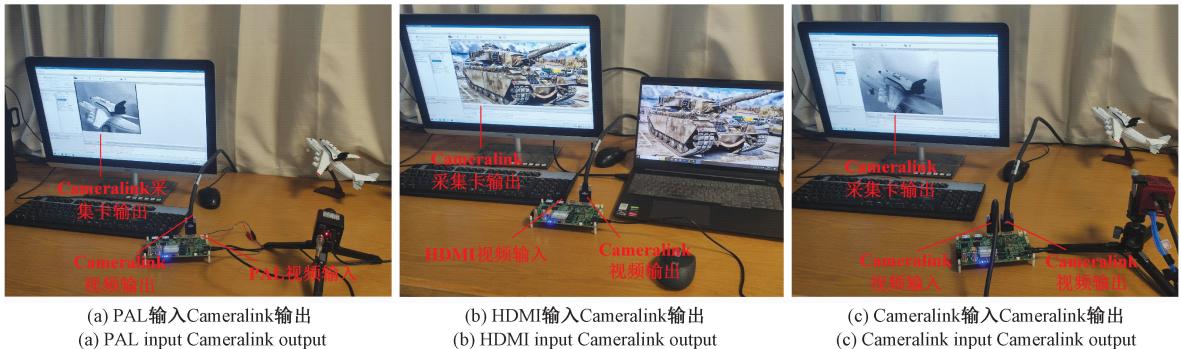

##### 3) 基于 Cameralink 输出的视频格式切换

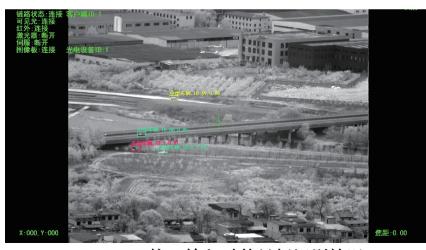

Cameralink 解码的视频源使用的是实验室自研国产钢镓砷短波红外相机。Cameralink 编码时,分别使用了 PAL 输入接口、HDMI 输入接口和 Cameralink 输入接口输入视频,经过 FPGA 处理之后从 Cameralink 视频输出接口显示。Cameralink 输出效果如图 19(a)~(c) 所示。

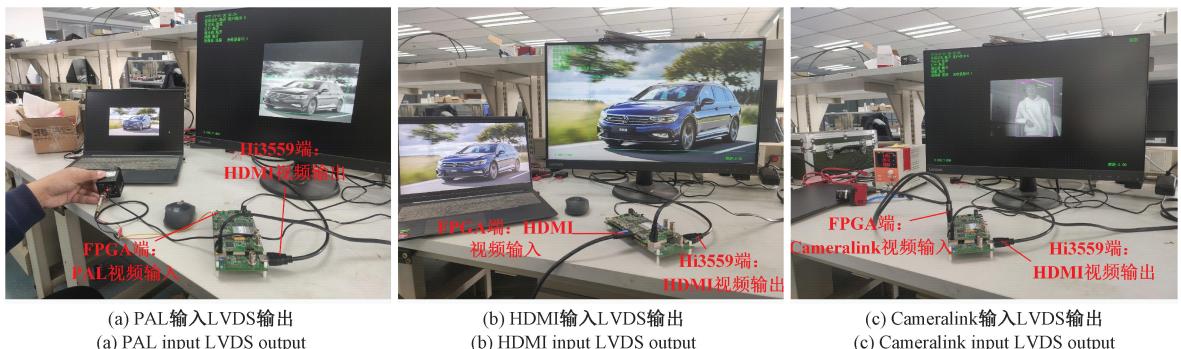

##### 4) 基于 LVDS 输出的视频格式切换

在进行 LVDS 编码时,视频输入分别采用 PAL、

格式的输出,分辨率为  $720 \times 576$  的模拟 PAL 相机和分辨率为  $640 \times 512$  的 Cameralink 相机分别作为 PAL 和 Cameralink 视频格式的输入源,HDMI 视频源笔记本电脑作为 HDMI 的输入,支持分辨率为 1 080p,显示屏作为 HDMI 的输出,稳压电源用来给相机供电。Hi3559 板卡和 FPGA 板卡之间通过 LVDS 接口相连实现数据传输。

图 18 视频格式转换结果

Fig. 18 Effect of video format conversion

#### 3.2 性能指标测试

##### 1) PAL 视频解码

在进行 PAL 视频的解码操作时,使用的是灰度相机。将采集的视频接入 PAL 接口,再分别用 HDMI、Cameralink 以及 Hi3559 端视频输出接口显示,解码效果如图 17(a)~(c) 所示。

HDMI 和 Cameralink 输入接口,之后数据传输到 FPGA,再进行 LVDS 编码将数据发送到 Hi3559 处理器进行处理与显示。LVDS 编码输出效果如图 20(a)~(c) 所示。

根据以上各个视频接口格式的转换实验,可以看出,3 种视频输入接口与 3 种视频输出接口之间的视频格式切换效果都比较稳定,且视频画面清晰,满足了实际应用的需求。

#### 3.2 性能指标测试

HDMI 接口输出的视频的分辨率和帧率如图 21 所示。PAL 相机的视频分辨率为  $720 \times 576$ ,Cameralink 相机的分辨率为  $640 \times 512$ ,由于 HDMI 输出接口支持的分辨率是固定搭配,没有与 PAL 输入接口和 Cameralink 输入

图 18 HDMI 输出效果

Fig. 18 HDMI output effect

图 19 Cameralink 输出效果

Fig. 19 Cameralink output effect

图 20 LVDS 编码效果

Fig. 20 LVDS encoding effect

图 21 HDMI 输出效果

Fig. 21 HDMI output effect

接口传输的分辨率相匹配的选项,故选择  $800 \times 600$  作为 HDMI 视频的输出分辨率。从图 21(a)和(c)中可以看出, PAL 输入和 Cameralink 输入时,HDMI 输出的视频分辨率均为  $800 \times 600$ ,视频帧率为 60 fps,图 21(b)显示 HDMI 接口输入时,HDMI 输出的视频分辨率为  $1080p$ ,帧率为 60 fps。表明 HDMI 输出接口能正常运行。

图 22(a)展示了 PAL 接口输入,Cameralink 接口输出时的视频帧率为 40.9 fps,分辨率为  $720 \times 576$ ,图 22(b)中

显示,HDMI 接口输入、Cameralink 接口输出时的视频帧率为 34.3 fps,分辨率为  $1080p$ ,图 22(c)中显示,Cameralink 接口输入、Cameralink 接口输出时的视频帧率为 25.0 fps,分辨率为  $640 \times 512$ 。表明 Cameralink 输出接口能正常工作。

LVDS 接口输出的数据是直接发送到 Hi3559 进行处理,最后通过 Hi3559 的 HDMI 接口输出显示,视频的分辨率和帧率是其内部测试的,这里不多叙述。

(b) HDMI 输入 Cameralink 输出效果图

(c) Cameralink 输入 Cameralink 输出效果图

图 22 Cameralink 输出效果

Fig. 22 Cameralink output effect

### 3.3 性能对比

本文设计的系统可以接收 PAL、Cameralink、HDMI 的视频格式类型,同时支持转换为 LVDS、Cameralink 和

HDMI 格式输出,且输入和输出格式之间可以无缝切换。与文献[5]和文献[6]的输入输出视频接口类型对比如表 2 所示。

表 2 本文提出的系统与文献[5]和文献[6]支持的视频接口类型对比

Table 2 Comparison of supported video interface types between the proposed system and references [5] and [6]

| 文献[5]   |            | 文献[6]      |         | 本文设计的系统    |            |

|---------|------------|------------|---------|------------|------------|

| 支持的输入接口 | 支持的输出接口    | 支持的输入接口    | 支持的输出接口 | 支持的输入接口    | 支持的输出接口    |

| PAL     | PAL        | HD_SDI     | 以太网     | PAL        | LVDS       |

| PAL     | VGA        | Cameralink |         | Cameralink | Cameralink |

|         | Cameralink | PAL        |         | HDMI       | HDMI       |

从表中可以看出,文献[5]提出的系统只支持一种视频源的输入,文献[6]中的视频信号处理平台中的视频信号仅通过以太网接口编码输出,本文设计的系统支持 3 种视频接口的输入以及 3 种视频接口的输出,对 LVDS 编码的支持提供了高速、低功耗的数字信号传输通道,对 HDMI 接口的支持则增强了系统在高清晰度视频应用中的适应性和兼容性。此外,3.2 节的性能指标测试表明 PAL 输入、Cameralink 输入和 HDMI 输入时,HDMI 接口编码输出的分辨率分别为  $800 \times 600$  和  $1080p$ ,帧率均达到了 60f/s,Cameralink 接口编码输出的分辨率分别为  $720 \times 576$ 、 $640 \times 512$  和  $1080p$ ,帧率分别为 40.9、25.0 和 34.3 fps。即使 PAL 相机的视频分辨率为  $720 \times 576$ ,Cameralink 相机的分辨率为  $640 \times 512$ ,系统也能进行适当的处理和调整,使得最终编码输出的信号能够在同一接口下保持较高的质量以及能够确保在不同应用场景下的视频流畅性,展示了系统在处理不同输入信号时的灵活性和

适应性。由此可见,在输入输出接口的种类和性能上,系统均表现出更强的多样性和兼容性,能够满足更广泛的应用需求,尤其在需要高分辨率和高速数据传输的系统中具有显著优势。这些改进不仅提升了系统的灵活性和可扩展性,也为未来的多样化智能应用奠定了坚实基础。

### 3.4 逻辑资源占用

FPGA 的逻辑资源占用率如表 3 所示,LUT、LUTRAM、FF、BRAM 以及 DSP 等各类资源的消耗比例均未超过 10%,对于关键的时钟资源,包括 MMCM 和 PLL,它们的占用率也稳定在 50% 以下。这样的低资源占用率为后续的深度开发和扩展提供了足够的逻辑资源裕量。

### 3.5 系统的应用

本文设计的基于 FPGA 的多接口视频编解码系统已经与 ARM 端的 Hi3559 集成,构成了一个高效的智能识别系统,系统中 FPGA 编解码板卡与 Hi3559 板卡通过板间连接器进行连接,如图 23 所示。多接口编解码系统主要

表 3 FPGA 逻辑资源占用率

Table 3 FPGA logic resource utilization %

| 逻辑资源   | 占用率  | 逻辑资源 | 占用率   |

|--------|------|------|-------|

| LUT    | 8.46 | IO   | 43.60 |

| LUTRAM | 3.65 | GT   | 6.25  |

| FF     | 3.52 | BUFG | 43.75 |

| BRAM   | 0.90 | MMCM | 30.00 |

| DSP    | 0.36 | PLL  | 10.00 |

是对各类视频源的输入进行解码之后再编码输出给 ARM 端进行识别处理,集成的智能识别系统能够实时识别并分类各种类型的车辆(如小型车辆、中型车辆和大型车辆),并为每个识别到的目标分配唯一的 ID 进行追踪和监控。不同视频接口输入时智能识别系统在实际应用中的效果如图 24(a)~(c)所示。从图中可以看出,本文设计的视频

图 23 智能识别系统

Fig. 23 Intelligent identification system

(a) PAL 接口输入时的目标识别情况

(a) Target recognition under PAL interface input(b) HDMI 接口输入时的目标识别情况

(b) Target recognition under HDMI interface input(c) Cameralink 接口输入时的目标识别情况

(c) Target recognition under Cameralink interface input

图 24 多接口编解码系统应用实例

Fig. 24 Application example of the multi-interface encoding and decoding system

编解码系统的准确性与实时性比较高,能准确识别到车辆以及它们的大小,达到了预期标准。

## 4 结 论

针对主流视频编解码系统接口方式单一,应用领域有限的问题,本文基于 FPGA 设计了一种多接口视频编解码系统,系统在硬件上适配了 4 种视频接口,并在逻辑功能上增加了编解码选择模块的设计,实现了不同视频接口之间的无缝转换。此外,该系统可以通过 LVDS 接口与海思 Hi3559 进行连接,拓展了 Hi3559 视频接口的兼容性。经过多次功能验证以及性能指标测试,系统的模拟 PAL、HDMI、Cameralink 以及 LVDS 视频接口的解码输入和编码输出功能都很稳定且效果较好,同时逻辑资源占用较少,为机器视觉系统应用到多种场景提供了一个良好的解决方案。但是本系统的 LVDS 接口数据传输仅用到四条 Lane,LVDS 的发送速率仅达到 600 Mbps,并未到达系统的传输极限,在未来的研究中可以增加多路 LVDS 的输出,使系统的性能得到充分的发挥。

## 参 考 文 献

- [1] 赵冬青,王晨辉,陈建军. 基于 Hi3519 的高清图像采集存储装置设计[J]. 电子测量技术, 2020, 43(22): 170-174.

ZHAO D Q, WANG CH H, CHEN J J. Design of high-definition image acquisition and storage device based on Hi3519 [J]. Electronic Measurement Technology, 2020, 43(22): 170-174.

- [2] 马家麟,孙海洲,任贵珊,等. 高集成度多种格式并行输出的视频测试信号源研制[J]. 电子测量与仪器学报, 2022, 36(3): 217-223.

MA J L, SUN H ZH, REN G SH, et al. Implementation of the high-integration video signal-source with the multi-format and parallel-output function[J]. Journal of Electronic Measurement and Instrumentation, 2022, 36(3): 217-223.

- [3] 刘静军,贺小军,王鹏,等. 星载多模式和多通道图像采集与处理[J]. 电子测量技术, 2023, 46(20): 30-35.

LIU J J, HE X J, WANG P, et al. Spaceborne multi-mode and multi-channel image acquisition and processing[J]. Electronic Measurement Technology, 2023, 46(20): 30-35.

- [4] JAIN D K, JACOB S, ALZUBI J, et al. An efficient and adaptable multimedia system for converting PAL to VGA in real-time video processing[J]. Journal of Real-Time Image Processing, 2020, 17 ( 6 ): 2113-2125.

- [5] 张海平. 基于 FPGA 的多接口实时视频处理系统研

- 究[D]. 吉林:吉林大学, 2015.

- ZHANG H P. Multi interface real time video processing system based on FPGA [D]. Jilin: Jilin University, 2015.

- [6] LATINOVIC N, POPADIC I, TOMIC B, et al. Signal processing platform for long-range multi-spectral electro-optical systems[J]. Sensors, 2022, 22(3):1294.

- [7] 孙楠, 张鹏, 孟园. 全景图像采集与高速传输系统设计[J]. 国外电子测量技术, 2023, 42(7): 88-94.

- SUN N, ZHANG P, MENG Y. Panoramic image acquisition and high-speed transmission system design[J]. Foreign Electronic Measurement Technology, 2023, 42(7): 88-94.

- [8] 李历仲. 兼容多种视频输出的图像编解码系统接口板设计[D]. 西安:西安电子科技大学, 2019.

- LI L ZH. Design of interface board compatible with multiple video output format for image coding and decoding system [D]. Xi'an: Xi'an Xidian University, 2019.

- [9] 尚辰阳, 任勇峰. 基于 LVDS 远距离高可靠性传输系统设计[J]. 仪表技术与传感器, 2022(12): 67-72.

- SHANH CH Y, REN Y F. Design of long distance high reliability transmission system based on LVDS [J]. Instrument Technique and Sensor, 2022(12): 67-72.

- [10] 刘博, 邱凯强, 赵谦. 嵌入式硬件供电时序控制方法的研究[J]. 航空计算技术, 2023, 53(4): 113-116.

- LIU B, QIU K Q, ZHAO Q. Research on sequence control method of embedded hardware power supply [J]. Aeronautical Computing Technique, 2023, 53 (4): 113-116.

- [11] 李浩, 王厚军, 肖磊, 等. 高速并行数字调制信号的产生与实现[J]. 仪器仪表学报, 2023, 44(2): 110-118.

- LI H, WANG H J, XIAO L, et al. Generation and implementation of high-speed parallel digital modulation signals[J]. Chinese Journal of Scientific Instrument, 2023, 44(2): 110-118.

- [12] HE S CH, ZHOU Y, LIN S, et al. FPGA-based research on high frame rate infrared image real-time acquisition and processing system[C]. 7th Symposium on Novel Photoelectronic Detection Technology and Applications, 2021;11763.

- [13] SARKAR S, BHAIRANNAWAR S S, RAJA K B. FPGACam: A FPGA based efficient camera interfacing architecture for real time video processing [J]. IET Circuits Devices & Systems, 2021, 15(8): 814-829.

- [14] 严飞, 丁兆东, 刘银萍, 等. 基于 FPGA 的多路实时视频处理系统设计[J]. 液晶与显示, 2022, 37(7): 861-870.

- YAN F, DING ZH D, LIU Y P, et al. Design of multi-channel real-time video processing system based on FPGA[J]. Chinese Journal of Liquid Crystals and Displays, 2022, 37(7): 861-870.

- [15] 赵清琳, 任勇峰, 武旌阳. 基于 FPGA 的 PAL 图像数据解码与传输设计[J]. 集成电路与嵌入式系统, 2024, 24(3): 94-98.

- ZHAO Q L, REN Y F, WU J Y. Design of PAL image data decoding and transmission based on FPGA [J]. Integrated Circuits and Embedded Systems, 2024, 24(3): 94-98.

- [16] 付思哲. 基于 FPGA 的视频去隔行系统设计[D]. 北京:中国石油大学, 2022.

- FU S ZH. Design of video deinterlacing system based on FPGA [D]. Beijing: China University of Petroleum, 2022.

## 作者简介

郑慧捷(通信作者),硕士研究生,主要研究方向为视频图像处理及工程化实现。

E-mail:z1605822025@163.com

吕庆丰,硕士研究生,主要研究方向为视频图像处理及工程化实现。

朱志行,本科,主要研究方向为视觉感知和图像处理。

邑翔,硕士研究生,主要研究方向为视频图像处理及工程化实现。

闵超波,博士,副教授,主要研究方向为机器视觉与光电探测。