DOI:10.19651/j.cnki.emt.2416065

# 基于分裂基 FFT 的 S 波段雷达信号 处理单元设计与实现<sup>\*</sup>

陈泽宗 周章凯 赵晨

(武汉大学电子信息学院 武汉 430072)

**摘要:** 回波信号的信息解调主要依赖于 FFT 完成, 本文提出了一种基于分裂基 FFT 的 FPGA 实现信号处理单元方案, 用于高效解调回波信号信息。在原方案中, 距离维解调由 DSP 完成, 速度维解调在 PC 端进行, 但其采用的单核 DSP 无法同时处理距离维解调与数据上传, 导致实时性较低。本文利用 FPGA 并行处理和灵活可编程的特点, 将两次信号解调集成至 FPGA 中实现, 并完成了数据处理与上传的并行设计, 提高了数据处理的实时性与可靠性。其中分裂基 FFT 是实现上述功能的关键, 本文通过设计自适应计算单元与数据流控制单元, 提升了分裂基 FFT 的处理速度, 相比传统结构, 本文方案节省了 5.4% 以上的计算周期; 相比改进后的分裂基 FFT, 可节省 2.31% 以上的计算周期。闭环测试结果表明, 本文设计的集成化信号处理单元解调得到的目标点信噪比高达 70 dB, 能够很好地满足信号处理的要求。

**关键词:** 分裂基 FFT; 回波信号处理; FPGA

中图分类号: TN952 文献标识码: A 国家标准学科分类代码: 510.1020

## Design and implementation of S-Band radar signal processing unit based on split-radix FFT

Chen Zezong Zhou Zhangkai Zhao Chen

(School of Electronic Information, Wuhan University, Wuhan 430072, China)

**Abstract:** The demodulation of echo signal information primarily relies on the FFT. This paper proposes an FPGA-based signal processing unit scheme utilizing the split-radix FFT for efficient information demodulation of echo signal. In the original scheme, range dimension demodulation was performed by a DSP, while velocity dimension demodulation was conducted on a PC. However, the single-core DSP could not handle range dimension demodulation and data uploading in parallel, resulting in suboptimal real-time signal processing. Leveraging the large-scale parallel processing and flexible programmability of FPGA, this paper integrates both demodulations into the FPGA, achieving a parallel design for data processing and uploading, thereby enhancing real-time data processing. The split-radix FFT is crucial for achieving this functionality. By designing adaptive computation units and data flow control units, this paper improves the processing speed of the split-radix FFT. Compared to traditional structures, the proposed scheme reduces computation cycles by over 5.4%; compared to the improved split-radix FFT, it reduces computation cycles by over 2.31%. Closed-loop test results demonstrate that the integrated signal processing unit designed in this paper achieves a target signal-to-noise ratio (SNR) of 70 dB, effectively meeting the requirements for signal processing.

**Keywords:** split-radix FFT; echo signal processing; FPGA

## 0 引言

随着雷达技术的不断发展, 雷达在目标检测、自动驾驶以及海洋探测等领域发挥着不可或缺的作用<sup>[1-3]</sup>。武汉大

学无线电海洋遥感实验室自主研发了一款船载 S 波段多普勒测波雷达, 能够便捷地获取海洋的浪高、浪周期和表面流等动力学参数<sup>[4]</sup>。对于雷达系统接收到的回波信号, 经过专用芯片完成数字下变频后, 即可得到两路基带信号正交

分量  $I$  与同相分量  $Q$ 。基于回波谱理论,对  $I$ 、 $Q$  信号在距离维和速度维各完成一次快速傅里叶变换(fast Fourier transform,FFT),即可解调得到在不同距离元处的海洋流速信息<sup>[5]</sup>。文献[6]采用 DSP 处理器 TMS320C6748 + Spartan6 系列 FPGA 完成了上述的 S 波段雷达主板的设计,其中信号处理主要由 DSP 配合 PC 端完成,DSP 负责  $I$ 、 $Q$  信号的距离维解调,PC 端负责对 DSP 上传的数据完成速度维解调,而 FPGA 则负责整体雷达时序控制。

然而,由于 TMS320C6748 为单核处理器,无法同时处理多个进程,故在上传数据时,距离维解调需要等待一定的时间才能开始处理。显然,当出现数据上传耗时较久的情况时,数据处理的实时性将会下降。针对此类问题,文献[7-8]基于多核 DSP 可并行处理多进程的特性,实现了多任务并行设计。然而,相对于高端多核 DSP,FPGA 有着灵活可编程、可扩展性强、成本低等优势,因此本文选择资源较丰富的 Kintex-7 系列 FPGA,完成了雷达信号处理单元的设计。并且,不同于常见采用 FPGA 中 Nios II、Microblaze 等不便移植的软核处理器来实现信号处理的方案<sup>[9-10]</sup>,本文完全使用硬件描述语言完成了整体设计,并将两次信号解调过程移植到 FPGA 中实现,这大幅地提升了雷达信号处理单元的可靠性与可移植性。

其中,FFT 处理的快慢是决定着信号处理单元性能的重要因素,相对于基 2 或基 4FFT 算法,杜梅尔(Duhamel)等提出的分裂基 FFT 算法具有更低的复数乘法计算量,在计算复杂度与工程实现复杂度之间取得了较好的均衡<sup>[11]</sup>。文献[12]通过 4-bit 量化旋转因子,进一步减少了 FPGA 实现分裂基 FFT 算法时的资源消耗,但其计算精度为 0.25,不适用于本文中对信号处理精度要求较高的场景。文献[13]基于 Eisenstein 基底,对分裂基 FFT 算法进行了改进,进一步减少了乘法计算量,但是其主要应用于信号长度为 6 的整数次幂的情况。文献[14]基于资源换取速度的思想,理论上实现了低延迟全并行流水线分裂基 FFT 的设计,但是其资源消耗过多。

并且,上述分裂基 FFT 实现方案均是基于 L 形运算单元完成的。从运算的中间级开始,分解结果中开始出现 2 点或 4 点 DFT,此时若继续仅采用 L 形运算单元,会导致计算结构臃肿复杂,点数不能灵活改变。因此,本文基于分裂基 FFT 的运算结构,在 FPGA 中设计了自适应计算单元与数据流控制单元,使其在资源消耗不大的情况下,能够在较短的时间内完成分裂基 FFT 处理。同时,相较于文献[6],本文将两次信号解调过程集成至 FPGA 中实现,使得信号处理单元更加的集成化与小型化;并且解调得到的目标点信噪比高达 70 dB,完全满足要求。因而,本文在完成信号处理单元集成化设计的同时,提供了一种 FPGA 高效完成分裂基 FFT 的方案。

## 1 基于分裂基 FFT 的雷达信号处理

### 1.1 回波信号的信息解调

S 波段雷达为线性调频中断连续波(linear frequency modulation interrupted continuous wave,LFMICW)体制,设雷达发射信号  $S_e$  的中心频率为  $f_e$ ,初始相位为 0。则发射信号可以表示为:

$$S_e(t) = \cos(2\pi f_e t + \pi\alpha t^2), 0 \leq t \leq T_s \quad (1)$$

其中,  $\alpha = B/T_s$ ,  $T_s$  为扫频周期,  $B$  为扫频带宽。

假设在一次实验中,共连续发射了  $N$  个扫频脉冲,对于第  $p$  ( $1 \leq p \leq N$ ) 个扫频脉冲而言,回波相对于发射信号的延迟为  $T_d(t)$ ,如下:

$$T_d(t) = T_0 - \frac{2v(t + pT_s)}{c} \quad (2)$$

其中,  $T_0 = 2R_0/c$ ,  $R_0$  为目距离,  $c$  为光速,  $v$  为目径向速度。则其回波信号  $S_r(t)$  可表示为:

$$S_r(t) = A \cdot S_e(t - T_d(t)) = A \cos[2\pi\varphi_p(t)] \quad (3)$$

其中,  $A$  为信号衰减,  $\varphi_p(t)$  为回波信号的瞬时相位。由于  $S_r(t)$  经过数字下变频之后,可生成 IQ 两路信号<sup>[15]</sup>,故在单个扫频周期  $T_s$  内,第  $p$  个脉冲的目标回波信号可以表示为复信号  $S_p(t)$  的形式。

$$S_p(t) = A_p \cdot e^{j\varphi_p(t)} = A_p \cdot e^{j(\varphi_p + 2\pi f_p t)} \quad (4)$$

其中,  $f_p$  为接收到回波信号的频率,  $\varphi_p$  为相位,则根据式(2)~(4)可得:

$$f_p = \frac{2vf_e}{c} - \alpha T_0 + \frac{2vpBf_e}{c} \quad (5)$$

由于目标速度引起的频偏远远小于目标距离引起的频偏,故通过  $f_p$  即可解调得到目标距离  $R_0$ 。而在一个扫频周期内,对式(4)关于时间  $t$  做 FFT,可得其频谱函数  $S_p(f)$  如下:

$$S_p(f) = \frac{A_p}{2} \frac{\sin\pi(f - f_p)T_s}{\pi(f - f_p)} e^{j\varphi_p} \quad (6)$$

式(6)为中心频率为  $f_p$  的抽样函数谱,即距离解调后的回波谱。在对同一距离元处的观测速度时,可将相位  $\varphi_p$  看作是在  $[-NT_s/2, NT_s/2]$  上的连续信号以频率  $1/T_s$  采样得到的,公式如下:

$$\varphi_p = \varphi_0 + 2\pi f_e \frac{2v}{c} t, |t| \leq \frac{NT_s}{2} \quad (7)$$

$\varphi_0$  为常量。此时,同一距离元处信号表示为:

$$S_R(t) = A_m e^{j\varphi_p}, |t| \leq \frac{NT_s}{2} \quad (8)$$

对每个距离元处接收到的  $N$  个不同扫频脉冲信号进行 FFT,即可得到距离多普勒谱  $S_R(f)$ :

$$S_R(f) = A_m \frac{\sin\pi(f - \frac{2v}{c}f_e)NT_s}{\pi(f - \frac{2v}{c}f_e)} e^{-j2\pi f_e T_0} \quad (9)$$

通过式(9)可得到由目标速度引起的频偏  $\Delta f =$

$2v_f/c$ , 进而得到对应距离元处的径向速度  $v$ 。本文将得到式(6)和(9)的过程分别称为距离维 FFT 与速度维 FFT, 二者为雷达信号解调的关键部分, 因此, 为提升雷达回波信号处理单元的性能, 本文采用乘法计算量更少的分裂基 FFT 来完成设计。

## 1.2 分裂基 FFT 算法

对于序列长度为  $N = 2^M$  ( $M$  为正整数) 的复信号  $x(n)$ , 其离散傅里叶变换 (discrete Fourier transform, DFT) 后的表达式如式(10)所示。

$$X(k) = \sum_{n=0}^{N-1} x(n) W_N^{nk}, n, k \in [0, N-1] \quad (10)$$

分裂基 FFT 的基本思想是对偶序号的值按照基 2 进行分解, 奇序号则按照基 4 进行分解<sup>[16]</sup>。为在 FPGA 中实现该运算结构, 将序号  $n, k$  按如下分解:

$$n = n_0 + \frac{N}{4}n_1, 0 \leq n_0 \leq \frac{N}{4} - 1, 0 \leq n_1 \leq 3 \quad (11)$$

$$k = 4k_0 + k_1, 0 \leq k_0 \leq \frac{N}{4} - 1, 0 \leq k_1 \leq 3$$

将式(11)代入到式(10)中, 可得:

$$X(4k_0 + k_1) = \sum_{n_0=0}^{N/4-1} \sum_{n_1=0}^3 \left[ x\left(n_0 + \frac{N}{4}n_1\right) W_4^{n_1 k_1} \right] W_N^{n_0 (4k_0 + k_1)} \quad (12)$$

当  $k_1 = 0, 2$  时, 旋转因子  $W_4^{n_1 k_1}$  结果为  $\pm 1$ , 故可将偶数序号处的  $X(4k_0)、X(4k_0 + 2)$  合在一起看作每隔 2 点取 1 点的  $N/2$  点抽选, 如下所示:

$$X(2k_a) = \sum_{n_a=0}^{N/2-1} x_a(n_a) W_N^{2n_a k_a} = \text{DFT}[x_a(n_a)],$$

$$0 \leq k_a \leq N/2 - 1 \quad (13)$$

其中,  $x_a(n_a) = [x(n_a) + x(n_a + N/2)]$ 。同理奇数序号处的  $X(4k_0 + 1)、X(4k_0 + 3)$  可各看作  $X(k)$  序列每隔 4 点取 1 点的  $N/4$  点抽选, 如下所示:

$$X(4k_b + 1) = \sum_{n_b=0}^{N/4-1} x_b(n_b) W_N^{4n_b k_b} = \text{DFT}[x_b(n_b)], 0 \leq$$

$$k_b \leq N/4 - 1 \quad (14)$$

$$X(4k_c + 3) = \sum_{n_c=0}^{N/4-1} x_c(n_c) W_N^{4n_c k_c} = \text{DFT}[x_c(n_c)], 0 \leq$$

$$k_c \leq N/4 - 1 \quad (15)$$

$$\text{其中, } x_b(n_b) = \sum_{n_1=0}^3 [x(n_b + n_1 N/4) W_4^{n_1}] W_N^{n_b}, x_c(n_c) = \sum_{n_1=0}^3 [x(n_c + n_1 N/4) W_4^{3n_1}] W_N^{3n_c}.$$

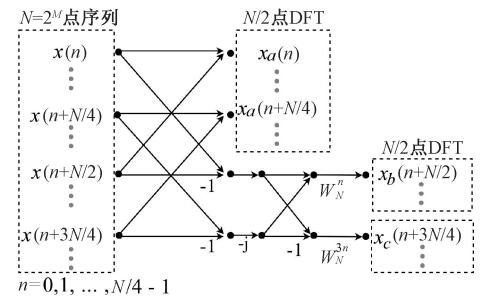

根据式(13)~(15)可得分裂基 FFT 基本的信号流图如图 1 所示, 根据图 1 可知为得到  $x_a(n_a)$  值, 进行 1 次加法操作即可, 而为得到  $x_b(n_b)$  或  $x_c(n_c)$  值需要进行 3 次加减和 1 次复数乘法操作。

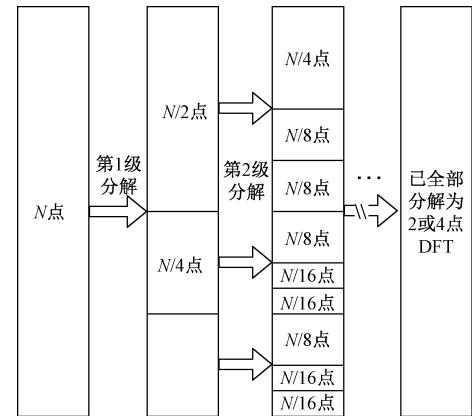

$N$  点 DFT 经过第一级的  $N/4$  次 L 形运算后, 可以分解为一个  $N/2$  点 DFT 和两个  $N/4$  点 DFT。经过  $M - 1$

图 1 分裂基 FFT 中 L 形运算流图

Fig. 1 L-Shaped flow diagrams in Split-Radix FFT

级分解后, 结果仅由 2 点或 4 点 DFT 组成, 如图 2 所示。

图 2 分裂基 FFT 分解示意图

Fig. 2 Schematic diagram of Split-Radix FFT decomposition

分裂基 FFT 通过将基 2 与基 4 分解耦合在一起, 相较于传统的基 2 和基 4 FFT, 分别可减少 33% 和 11% 以上的复数乘法量, 有效地降低了运算时长。

## 2 雷达信号处理单元集成化设计与实现

### 2.1 基于 FPGA 的雷达信号处理单元方案设计

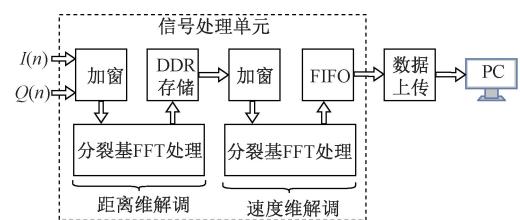

本文设计的雷达信号处理单元框图如图 3 所示, 其中, 两次加窗操作是为了抑制 FFT 处理过程中产生的频谱泄露, 进而提升解调准确度。

图 3 信号处理单元结构框图

Fig. 3 Block diagram of signal processing unit

在这里采用旁瓣更小的汉明窗函数, 对信号进行振幅调制, 其可将 99.963% 的能量集中在窗谱的主瓣内<sup>[17]</sup>, 有效地抑制了频谱泄露。长度为  $N$  的汉明窗函数如下:

$$w(n) = 0.54 - 0.46 \cos\left(2\pi \frac{n}{N}\right) \quad (16)$$

其中,  $n = 0, 1, \dots, N-1$ , 上述的加窗操作采用 Xilinx 的乘法器 IP 核实现即可。同时, 由图 3 可知, 本文中信号处理单元完成信号的两次解调, 主要依靠分裂基 FFT 处理进行实现。

## 2.2 基于 FPGA 的分裂基 FFT 高效设计与实现

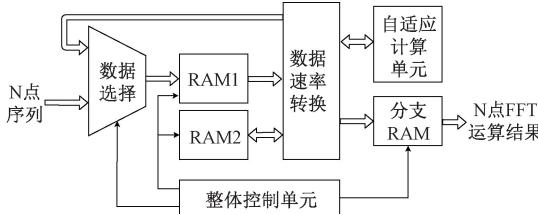

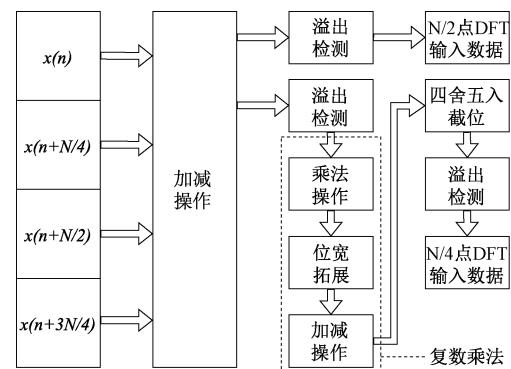

本文基于 FPGA 实现分裂基 FFT 的框架如图 4 所示, 经过该模块可完成  $N$  点分裂基 FFT 的处理。

图 4 分裂基 FFT 模块的实现框架

Fig. 4 Implementation of Split-Radix FFT module

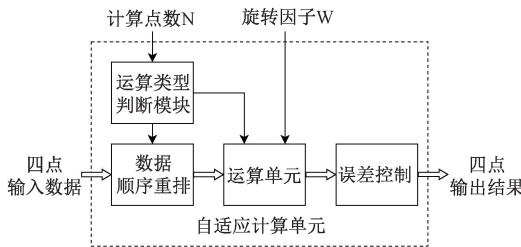

为处理分裂基 FFT 中不同类型的运算, 本文设计了自适应计算单元, 其结构如图 5 所示。

图 5 自适应计算单元框图

Fig. 5 Block diagram of adaptive computing unit

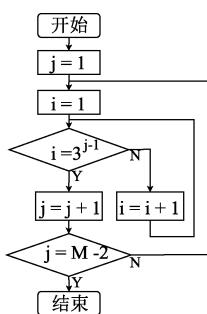

其中, 分裂基 FFT 处理速率与灵活性的提高均离不开图 5 中的运算类型判断模块。首先对图 2 中的各级运算的子序列按照  $(i, j)$  进行编号, 对应的点数定义为  $P(i, j)$ , 其中  $i$  为子序列在第  $j$  级中的序号, 比如第 2 级运算中第一个  $N/4$  点子序列编号为  $(2, 2)$ , 图 6 展示了  $N$  点序列中编号  $(i, j)$  遍历的过程。

图 6 子序列序号遍历过程

Fig. 6 Subsequent serial number traversal process

其中, 对  $i$  值关于 3 进行除法运算, 即可得到商  $k$  与余

数  $q$ , 进而通过式(17)可得到  $P(i, j)$ :

$$P(i, j) = \begin{cases} P(k+1, j-1)/2, & q = 0 \\ P(k+1, j-1)/4, & q \neq 0 \end{cases} \quad (17)$$

其中,  $j \in [2, M-2]$ ,  $P(1, 1) = N$ 。由式(17)可得各子序列的点数  $P(i, j)$ , 而其与自适应计算单元中的运算类型关系如表 1 所示。

表 1 子序列点数与运算标志的对应关系

Table 1 Correspondence between subsequence points and operation flags

| 点数 $P(i, j)$ | 运算标志 $Flag\_Comp$ |

|--------------|-------------------|

| 2            | $2'b01$           |

| 4            | $2'b10$           |

| 非 2 非 4      | $2'b00$           |

当运算标志  $Flag\_Comp$  为  $2'b01$ , 此时需要使能数据顺序重排模块, 以实现两次 2 点 DFT 的并行处理; 当  $Flag\_Comp$  为  $2'b10$ , 使能 4 点 DFT 计算单元; 当  $Flag\_Comp$  为  $2'b00$  时, 使能 L 形计算单元。由于在进行 2 点或 4 点 DFT 时, 旋转因子的值为  $\pm 1$ , 此时无需乘法器即可完成运算。基于上述的自适应计算单元, 本文在第  $M-2$  级即可完成  $N$  点分裂基 FFT 处理, 无需完成所有级的运算。

此外, 本文针对复数乘法进行了资源优化, 本文中采用的复数乘法单元如下:

$$(a+jb)(c+jd) = (ac-bd) + j(bc+ad) = a(c-d) + d(a-b) + j[c(b+a) - a(c-d)] \quad (18)$$

通过 3 个乘法器 IP 核即可实现复数乘法, 其中的每个复数乘法单元均可节省一个乘法器资源。

由于在 FPGA 中, 定点运算速度快, 资源消耗少, 但乘法计算精度较低<sup>[18]</sup>, 因此需要对其进行误差进行控制, 以防止运算误差扩大。以图 1 中 L 形运算为例, 其误差控制示意图如图 7 所示。

图 7 L 形运算中的误差控制

Fig. 7 Error control in L-Shaped computation

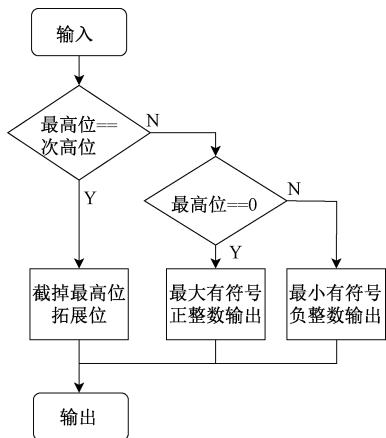

其中, 溢出检测主要针对四舍五入截位或加减运算后的结果而言的, 其检测流程如图 8 所示。

图 8 溢出检测流程

Fig. 8 Overflow detection process

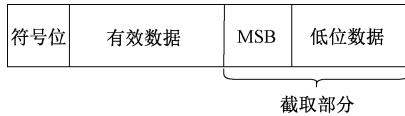

在复数乘法中, 乘法操作是先于加减操作的, 故在溢出检测之前, 需要先对乘法结果进行四舍五入截位, 如图 9 所示。

图 9 四舍五入截位操作

Fig. 9 Rounding and truncation

对于正数而言, 若截取部分的最高位 MSB 为 1, 则产生进位, 有效数据部分加 1。对于负数而言, 不需要进位时有效数据才需要加 1, 若截取部分的最高位为 1, 且低位数据不全为 0, 此时不发生进位, 有效数据部分加 1。为避免因加 1 操作而导致的数据溢出, 本文同样需在四舍五入截位后完成溢出检测, 如图 7 所示。

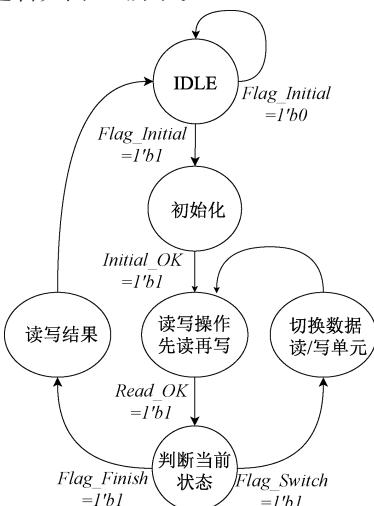

此外, 为确保不同级运算切换时数据能无间隙地处理, 本文基于分裂基 FFT 原址运算结构, 设计了数据流读写控制单元, 其逻辑如图 10 所示。

图 10 数据流读写控制逻辑

Fig. 10 Data stream read and write control logic

其中, 标志信号与对应的事件操作如表 2 所示。

表 2 不同标志信号与事件的对应关系

Table 2 Correspondence between different sign

signals and events

| 标志信号         | 信号拉高代表发生的事件   |

|--------------|---------------|

| Flag_Initial | 原始数据开始存入 RAM1 |

| Initial_OK   | 原始数据存储完成      |

| Read_OK      | 待处理的数据读取完成    |

| Flag_Switch  | 切换至下一级运算      |

| Flag_Finish  | 最后一级运算完成      |

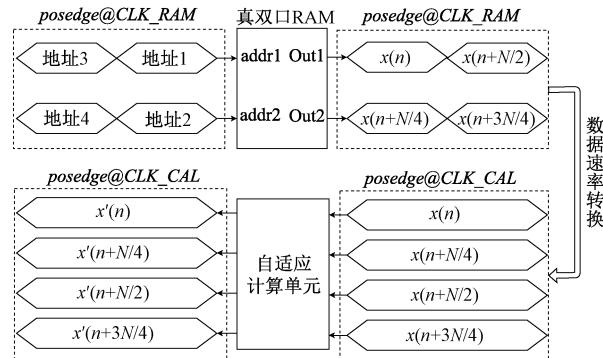

当切换至下一级运算时, 图 4 中 RAM1 和 RAM2 的存取功能将进行互换, 同时分支 RAM 中的内容将被新一级的运算结果覆盖。待最后一级运算完成时, 按照码元倒序对分支 RAM 读取, 即可得到 N 点分裂基 FFT 处理结果。由于上述 RAM 均为真双端口 RAM, 因此本文设计了数据速率转换模块, 如图 11 所示, 其中 CLK\_CAL 为计算单元的工作时钟, CLK\_RAM 为 RAM 的读写时钟。

图 11 数据速率转换功能框图

Fig. 11 Data rate conversion function block diagram

通过数据速率转换模块, 自适应计算单元可高效地与 RAM 完成数据交互, 从第  $\lceil (M-2)/2 \rceil$  级开始, 即可输出 FFT 结果, 并且仅需要  $M-2$  级运算即可完成  $N$  点分裂基 FFT。 $\lceil \cdot \rceil$  代表向上取整。

### 2.3 两次信号解调的并行处理设计与实现

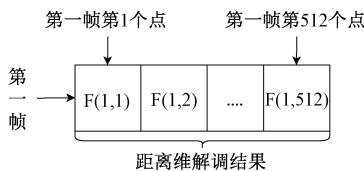

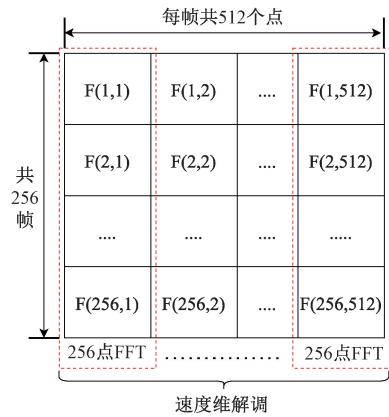

由图 3 可知, 本文将距离维与速度维解调均集成至信号处理单元中实现, 因此需要对两次信号解调并行处理的逻辑进行设计与实现。基于 1.1 节中的回波信号解调理论, 设共有 256 帧扫频脉冲, 一帧信号为 512 点。假设第一帧信号经过距离维 512 点分裂基 FFT 处理后的格式如图 12 所示。

经过 512 点分裂基 FFT 处理后, 即可得到一帧距离维解调的回波谱。如果要完成速度维解调, 则需要等待 256 帧相干累积完成, 如图 13 所示。

对 256 帧所有的第 1 个点组成的序列完成 FFT, 即可完成第 1 次速度维解调, 若要得到包含速度信息的距离多

图 12 第一帧数据处理后的格式

Fig. 12 Format of the first processed frame of data

图 13 256 帧数据相干累积示意图

Fig. 13 Diagram of coherent accumulation of 256 frames

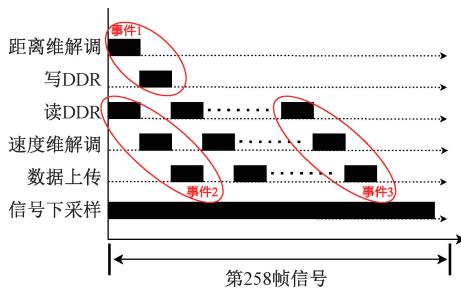

普勒谱,则需要 512 次速度维解调。因此,在前 256 帧信号距离维解调完成之后,方可开始第 1 次速度维解调,故需要对第 258 帧信号扫频周期内完成的事件进行并行控制,如图 14 所示。

图 14 事件并行示意图

Fig. 14 Event parallelism diagram

此时已经完成了前 256 帧的距离维解调以及 DDR 存储,其中事件 1 代表第 257 帧信号距离解调及结果存储操作;事件 2 代表前 256 帧信号的第一次速度维解调及结果上传操作;事件 3 代表最后一次速度维解调。而第 258 帧的信号下采样需在扫频周期内一直执行,因此通过对事件的并行化处理,可以最优化地利用资源完成信号处理单元的设计。

### 3 结果与分析

#### 3.1 S 波段雷达系统参数配置

本文以高海况为例对信号处理单元进行测试,参数配置如表 3 所示。

表 3 S 波段雷达系统参数配置

Table 3 S-band radar system parameter configuration

| 参数名称          | 值                   |

|---------------|---------------------|

| 相干累积帧数        | 256 帧               |

| 扫频周期 $T_s$    | $2.560 \mu\text{s}$ |

| 扫频带宽 $B$      | 30 MHz              |

| 基带信号速率 $f'_s$ | 200 KSPS            |

根据表 3 中的  $T_s$  与  $f'_s$  可得,在一个扫频周期内复信号  $I(n) + jQ(n)$  的有效点数  $N$  为 512 点,因此窗函数与对应距离维解调的点数也为 512 点,而速度维解调的点数与相干累积帧数相关,即 256 点。

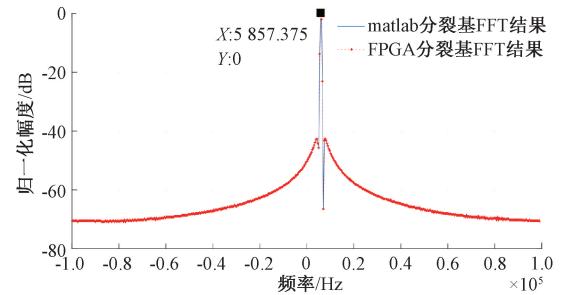

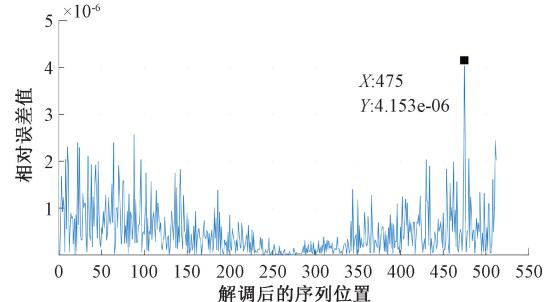

#### 3.2 数据处理误差分析

本文采用 FPGA 内生成的 1.506 MHz 理想信号作为模拟输入信号,其与 1.5 MHz 信号混频后,距离维 FFT 得到的理想差频值  $f_b$  应为 6 kHz。此处以距离维 FFT 为例,对误差进行分析,如图 15 所示。

(a) FPGA 与 matlab 进行距离维 FFT 后的谱对比

(a) Comparison of spectra after Range-Domain FFT between FPGA and MATLAB

(b) FPGA 与 matlab 处理之间的相对误差

(b) Relative error between FPGA and MATLAB processing

图 15 FPGA 与 matlab 进行距离维 FFT 对比

Fig. 15 Comparison of Range-Domain FFT between FPGA and MATLAB

由于距离维 FFT 点数  $N$  为 512,故当前的频率分辨率  $\epsilon = f'_s/N = 390.625 \text{ Hz}$ ,则实际距离维解调得到的差频  $f'_b$  如式(19)所示,其中  $\lfloor \cdot \rfloor$  为向下取整。

$$f'_b = \epsilon \cdot \lfloor \frac{f_b}{\epsilon} \rfloor \quad (19)$$

图 15 为 FPGA 与 matlab 进行距离维 FFT 的结果对比,可知二者得到的归一化幅度 0 dB 频点均为 5 859.375 Hz,与

式(19)计算值完全一致;且二者处理的相对误差最大不超过  $4.153 \times 10^{-6}$ 。证明 FPGA 中完成的分裂基 FFT 处理准确无误,能够很好地满足雷达信号处理单元的精度要求。

### 3.3 数据处理速率分析

据 2.2 节可知,本文完成  $N$  点分裂基 FFT 共需  $M-2$  级运算,且计算单元总需计算次数  $Cnt$  如下:

$$Cnt = \frac{M \cdot N}{6} - \frac{N}{36} - (-1)^M \cdot \frac{2}{9} \quad (20)$$

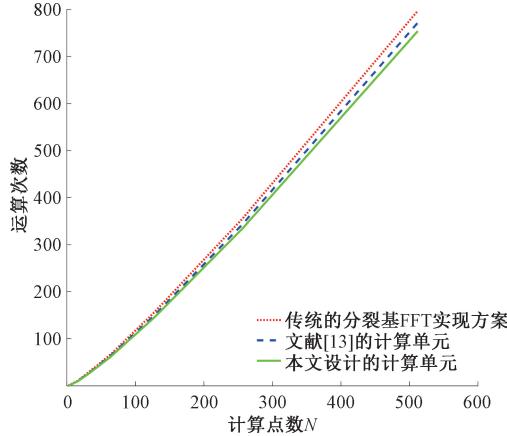

在乘法器资源消耗相同的情况下,随着点数  $N$  的增加,本文所设计的自适应计算单元优势越明显。当  $N=512$  时,本文相对于传统的运算结构至少可节省 5.4% 的计算周期;相对于文献[13]基于 Eisenstein 基底对分裂基 FFT 算法进行改进的方案,本文可节省 2.31% 以上的计算周期,对比如图 16 所示。

图 16 本文与其他计算单元运算次数的对比

Fig. 16 Comparison of the number of operations with other computing units

本文中各级运算切换时的流水线延迟为 10 个计算时钟 CLK\_CAL,因此本文基于 FPGA 完成  $N$  点分裂基 FFT 处理的总计算周期  $T$  为:

$$T = [Cnt + 10(M-2)] \times CLK\_CAL \quad (21)$$

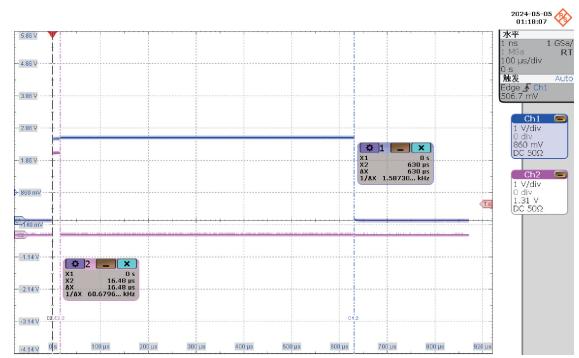

当 CLK\_CAL 为 50 MHz 时,以距离维解调为例,对本文与文献[6]中所需时长进行对比,对比如图 17 所示,蓝线代表本文处理时长,紫线代表文献[6]处理时长。

据图 17 可知,本文完成距离维解调中 512 点分裂基 FFT 所需时长为 16.48  $\mu$ s,与式(21)理论值完全一致。而文献[6]完成距离维解调需要 630  $\mu$ s,进一步证明了本方案能够有效地提升数据处理速率。

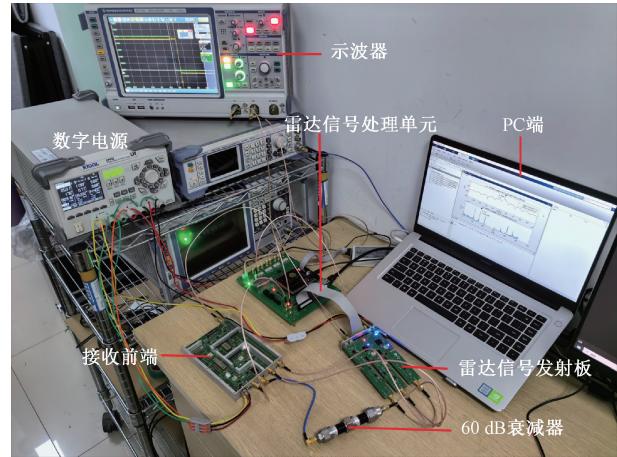

### 3.4 S 波段雷达信号处理单元闭环测试

S 波段雷达系统闭环测试环境如图 18 所示。大功率的发射信号经过一级 60 dB 衰减器后,再送至接收前端完成信号的下变频;得到的中频信号在雷达信号处理单元中完成信息解调,最后通过以太网将处理后的数据上传至 PC 端进行进一步分析。

为模拟在距离雷达  $R$  处存在静止目标,需要对 TP 信

图 17 本文与文献[6]处理时长对比

Fig. 17 Processing time comparison with reference [6]

图 18 雷达系统闭环测试环境

Fig. 18 Radar system closed-loop test environment

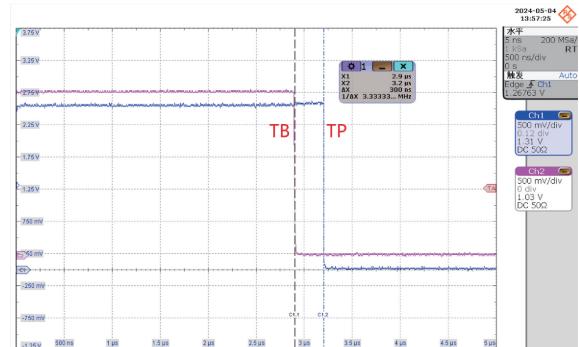

号延时  $\tau$ ,其具体设置如图 19 所示。

图 19 闭环测试时 TP 与 TB 信号设置

Fig. 19 TP and TB signal settings in closed-loop testing

TP 与 TB 分别是对雷达信号发射板和接收前端进行开关控制的脉冲信号,正常开环工作情况下 TP 应超前于 TB 信号 300 ns。在这里将 TP 信号滞后于 TB 信号 300 ns,如图 19 所示,因此此时的  $\tau$  值应为 600 ns,由  $R = c \cdot \tau / 2$ ,可得模拟静目标的距离  $R$  为 90 m。由于当前扫频带宽  $B$  为 30 MHz,根据  $\Delta R = c / 2B$ ,可得当前距离分辨

率  $\Delta R$  为 5 m。而在闭环测试时,距离维解调得到的差频  $f''_b$  应为:

$$f''_b = \epsilon \cdot \frac{R}{\Delta R} \quad (22)$$

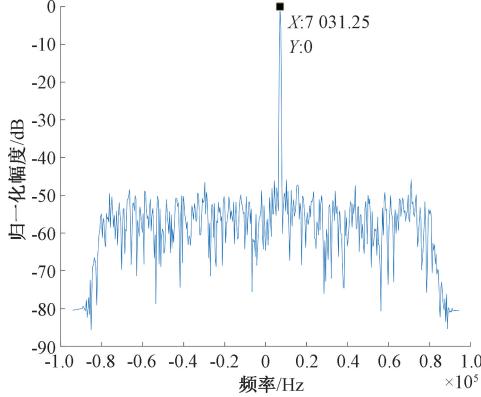

其中,  $\epsilon$  为频率分辨率 390.625 Hz。图 20 为 PC 端接收到的一帧距离维解调后得到的数据。

图 20 一帧距离维解调数据

Fig. 20 One frame of range demodulation data

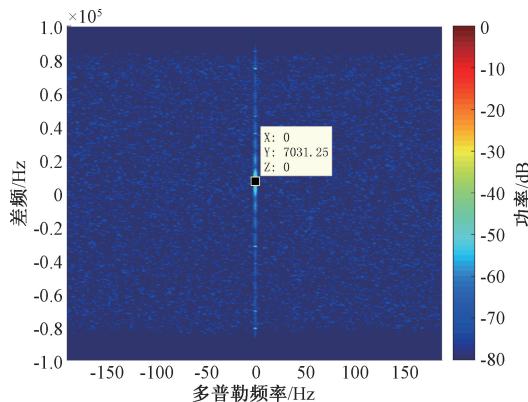

据图 20 可知在实际闭环测试时,归一化幅度 0 dB 频点为 7 031.25 Hz,与式(22)计算得到的  $f''_b$  完全一致,同时信噪比接近于 50 dB,证明本文设计的 S 波段雷达信号处理单元能够较好地完成距离维解调。图 21 为闭环测试时 256 帧相干累积得到的距离多普勒谱,也即回波信号的速度维解调。

图 21 256 帧相干累积距离多普勒谱

Fig. 21 256-frame coherent accumulated range-Doppler spectrum

从图 21 可知,归一化功率 0 dB 频点为 7 031.25 Hz,且该处的多普勒频率为 0 Hz,也即目标速度为 0 m/s。由此可得上述闭环测试得到的距离多普勒谱与模拟目标完全相符,且信噪比高达 70 dB。

此时对雷达信号处理单元的资源消耗进行分析,如表 4 所示。

据上述可知,在资源消耗不大的情况下,本文成功地将信号的两次解调集成在 S 波段雷达信号处理单元中实现,

表 4 S 波段雷达信号处理单元消耗资源

Table 4 S-band radar signal processing unit resource usage

| 资源类型       | 消耗资源   | 总资源     |

|------------|--------|---------|

| DSP48      | 32     | 840     |

| Block RAM  | 42     | 445     |

| Slice LUTs | 15 423 | 203 800 |

并且处理结果精确,误差极低,能够很好地满足指标要求。

## 4 结 论

本文基于分裂基 FFT 的运算结构,设计了自适应计算单元,通过对运算类型的判断,使得运算结构更加灵活,解决了分裂基 FFT 中不同运算类型导致的运算结构臃肿问题,使得分裂基 FFT 的处理周期更短。相对于传统的运算结构,本文至少可节省约 5.4% 的计算周期,与文献[13]相比,本文至少可节省约 2.31% 的计算周期。相较于文献[6]中雷达信号处理单元,本文中距离维解调的速率提升了一个数量级,同时将原本由 DSP 和 PC 端完成的两次信号解调均集成到 FPGA 中实现;在资源消耗较低的情况下,本文设计的 S 波段雷达信号处理单元运算精度较高,有着更高的集成度,从而方便后续的拓展与小型化实现。此外,本文提出的分裂基 FFT 高效实现方案,还可应用于其他信号处理领域,以提升系统性能并扩展应用范围,具有一定的参考价值。

## 参 考 文 献

- [1] 杨路,周文豪,余翔,等.一种抑制杂波的高精度车载雷达目标检测方法[J].仪器仪表学报,2022,43(10):145-151.

YANG L, ZHOU W H, YU X, et al. High-precision vehicle radar target detection method with clutter suppression [J]. Chinese Journal of Scientific Instrument, 2022, 43(10): 145-151.

- [2] 陈泽宗,李飞扬,赵晨,等.岸空双基地雷达时频同步电路设计[J].电子测量技术,2023,46(20):24-29.

CHEN Z Z, LI F Y, ZHAO C H, et al. Design of time-frequency synchronization circuit for shore-air bistatic radar[J]. Electronic Measurement Technology, 2023, 46(20): 24-29.

- [3] 杨建华,赵轩,郭全民,等.基于路侧激光雷达的障碍物目标检测方法[J].国外电子测量技术,2023,42(1):13-19.

YANG J H, ZHAO X, GUO Q M, et al. Obstacle target detection method based on roadside LiDAR[J]. Foreign Electronic Measurement Technology, 2023, 42(1): 13-19.

- [4] CHEN Z Z, CHEN X SH, ZHAO C H, et al. Wave height and wave period derived from a shipboard

- coherent S-Band wave radar in the south China sea[J]. *Remote Sensing*, 2019, 11(23): 2812-2834.

- [5] CHEN Z Z, WANG Z H, CHEN X, et al. S-Band doppler wave radar system[J]. *Remote Sensing*, 2017, 9(12): 1302.

- [6] 翟栋晨. 基于 FPGA 与 DSP 的雷达主板设计与实现[D]. 武汉: 武汉大学, 2020.

- ZHAI D CH. Design and implementation of radar mainboard based on FPGA and DSP [D]. Wuhan: Wuhan University, 2020.

- [7] 郑东卫, 白亚莉. 基于 FPGA 和多核 DSP 的雷达信号处理架构设计[J]. 火控雷达技术, 2023, 52(2): 84-90.

- ZHENG D W, BAI Y L. Design of a radar signal processing architecture based on FPGA and multi-core DSP[J]. *Fire Control Radar Technology*, 2023, 52(2): 84-90.

- [8] 李雷, 张晔, 胡楷. 基于 DSP 的海上红外小目标检测系统设计[J]. 现代电子技术, 2023, 46(4): 30-34.

- LI L, ZHANG Y, HU K. Design of marine infrared small-target detection system based on DSP [J]. *Modern Electronics Technique*, 2023, 46(4): 30-34.

- [9] 王青, 耿丽. 基于 FPGA 的激光雷达多通道数据实时采集系统[J]. 激光杂志, 2022, 43(11): 74-77.

- WANG Q, GENG L. Multi channel real-time data acquisition system of lidar based on FPGA[J]. *Laser Journal*, 2022, 43(11): 74-77.

- [10] 姚佳辰, 马睿, 杨晓华, 等. 基于分块转置的二维快速傅里叶变换的 FPGA 设计[J]. 电子测量技术, 2023, 46(15): 38-44.

- YAO J CH, MA R, YANG X H, et al. FPGA-based design of two-dimensional fast Fourier transformation via block transposing [J]. *Electronic Measurement Technology*, 2023, 46(15): 38-44.

- [11] 伍家松, 达臻, 魏黎明, 等. 基于分裂基-2/(2a)FFT 算法的卷积神经网络加速性能的研究[J]. 电子与信息学报, 2017, 39(2): 285-292.

- WU J S, DA ZH, WEI L M, et al. Acceleration performance study of convolutional neural network based on split-radix-2/(2a) FFT algorithms [J]. *Journal of Electronics & Information Technology*, 2017, 39(2): 285-292.

- [12] 季鹏飞. 单比特超宽带数字信道化接收机关键技术研究[D]. 长沙: 国防科技大学, 2022.

- JI P F. Research on key technology of monobit uwb digital channelized receiver [D]. Changsha: National University of Defense Technology, 2022.

- [13] 王超. 基于 Eisenstein 基底的快速傅里叶变换算法的研究[D]. 合肥: 中国科学技术大学, 2021.

- WANG CH. Research on fast fourier transform algorithm based on eisenstein[D]. Hefei: University of Science and Technology of China, 2021.

- [14] HAZARIKA J, AHAMED S R, NEMADE H B. Low-complexity, energy-efficient fully parallel split-radix FFT architecture[J]. *Electronics Letters*, 2022, 58(18): 678-680.

- [15] 吴思奇, 赵晨, 陈泽宗. 船载 S 波段测波雷达多带宽数字下变频设计[J]. 电子测量技术, 2021, 44(10): 17-23.

- WU S Q, ZHAO CH, CHEN Z Z. Design of multi-bandwidth digital down conversion of shipboard coherent S-band wave radar [J]. *Electronic Measurement Technology*, 2021, 44(10): 17-23.

- [16] 上官甲天, 王裕. 基于优化分裂基 FFT 算法的 APF 谐波检测策略[J]. 电子测量技术, 2023, 46(5): 23-29.

- SHANGGUAN J T, WANG Y. The harmonic detection strategy for APF based on the optimized split-radix FFT algorithm[J]. *Electronic Measurement Technology*, 2023, 46(5): 23-29.

- [17] 刘啸星, 蔡体青, 金伟明. 海洋重力测量中滤波方法比较研究[J]. 压电与声光, 2022, 44(6): 913-916.

- LIU X X, CAI T J, JIN W M. Comparative study on filtering methods in ocean gravity measurement [J]. *Piezoelectrics & Acoustooptics*, 2022, 44(6): 913-916.

- [18] 吴宇航, 何军. 基于 FPGA 加速的行为识别算法研究[J]. 电子测量技术, 2022, 45(13): 25-32.

- WU Y H, HE J. Research on activity recognition algorithm based on FPGA acceleration[J]. *Electronic Measurement Technology*, 2022, 45(13): 25-32.

## 作者简介

陈泽宗(通信作者), 博士, 教授, 主要研究方向为无线电海洋遥感。

E-mail: chenzz@whu.edu.cn

周章凯, 硕士研究生, 主要研究方向为雷达系统与数字电路设计。

E-mail: 2846244266@qq.com

赵晨, 博士, 副教授, 主要研究方向为海洋雷达技术。

E-mail: zhaoc@whu.edu.cn