DOI:10.19651/j.cnki.emt.2415823

# 一种用于 IC 测试的精密测量单元电路设计<sup>\*</sup>

夏进 刘士兴 李航 李帮金 梁华国

(合肥工业大学微电子学院 合肥 230009)

**摘要:** 随着集成电路产业的快速发展,对集成电路测试要求越来越高,精密测量单元是集成电路直流参数测试的核心单元。本文设计了一种用于集成电路测试的 PMU 电路,该电路使用现场可编程门阵列控制 DAC 模块施加电压激励,激励信号经 PI 调节器和功率放大器后,通过电阻匹配网络施加到被测器件,ADC 采集测试响应数据,实现加压测流、加流测压等参数测试功能。所设计的 PMU 电路具有测试范围宽、测量精度高的优点,施加/测量电压范围  $-10 \sim +15$  V、最大电流  $\pm 1.838$  A。对不同测试模式下的系统性能进行了校准并采用高精度电阻负载进行功能验证,实验结果表明,系统校准后的测试误差优于 0.05%,能够满足通用集成电路直流参数测试的要求。

**关键词:** 集成电路测试; 直流参数测试; 精密测量单元; 现场可编程阵列

中图分类号: TN98 文献标识码: A 国家标准学科分类代码: 510.10

## Precision measurement unit circuit design for IC testing

Xia Jin Liu Shixing Li Hang Li Bangjin Liang Huaguo

(School of Microelectronics, Hefei University of Technology, Hefei 230009, China)

**Abstract:** With the rapid development of the integrated circuit industry, higher requirements are put forward for integrated circuit testing, and the Precision Measurement Unit is the core unit for integrated circuit DC parameter testing. A PMU circuit for integrated circuit testing is designed in this paper, which uses a Field-Programmable Gate Array to control the DAC module to apply voltage excitation. The excitation signal after the PI regulator and power amplification is applied to the Device Under Test through the resistor matching network. Then, the ADC module reads back the test response data to realize the parameter testing functions such as applying voltage to measure current and applying current to measure voltage. The designed PMU circuit has the advantages of wide test range and high measurement accuracy, with an applied or measured voltage range of  $-10$  V to  $+15$  V and a maximum current of  $\pm 1.838$  A. The system performance in different test modes was calibrated and functionally verified with high-precision resistive loads, and the experimental results show that the system calibrated test error is better than 0.05%, which is able to meet the requirements of DC parameter testing of general-purpose integrated circuits.

**Keywords:** integrated circuit test; DC parameters test; precision measurement unit; field-programmable gate array

## 0 引言

集成电路测试是贯穿集成电路全寿命周期的重要环节,也是集成电路产品质量的保证<sup>[1]</sup>。自动测试设备(automatic test equipment, ATE)则是完成集成电路测试不可或缺的工具,其中直流参数测试是集成电路测试的重要环节,是验证集成电路的质量和性能重要手段。20世纪70年代以来,我国开展集成电路测试的相关研究,取得了阶段性成果<sup>[2]</sup>。但我国集成电路测试研究起步较晚,先进测试技术由发达国家垄断<sup>[3]</sup>,近年来,随着集成电路产业的

快速发展,国产集成电路测试设备不断涌出,开展集成电路测试技术的研究对我国集成电路产业的发展具有重要意义<sup>[4-5]</sup>。

精密测量单元(precision measurement unit, PMU)作为直流参数测试的主要功能部件,用于对被测器件(device under test, DUT)施加激励与测量响应<sup>[6]</sup>。文献[7-8]以FPGA作为控制单元,采用AD5522设计了精密测量单元,具有集成度高和测试速度快等优点,但受专用功能的制约,施加电压/电流的范围有限,可扩展性不足。文献[9-11]扩展了施加电压和电流的范围,仍存在带负载能力较弱等问题。

收稿日期:2024-04-12

\*基金项目:国家自然科学基金重大科研仪器研制项目(62027815)资助

题。本文设计了一种用于集成电路测试的精密测量单元电路,实现了电压/电流宽范围和高精度测量。

## 1 测试系统结构设计

直流参数测试是用来确定集成电路的直流电气性能,在规定的端子施加电压/电流激励,测量其响应值。如果响应值在规定范围,则通过测试;反之,测试失败<sup>[12-16]</sup>。PMU 电路对待测 DUT 施加电压/电流激励、并准确测量相应引脚的电流/电压值。

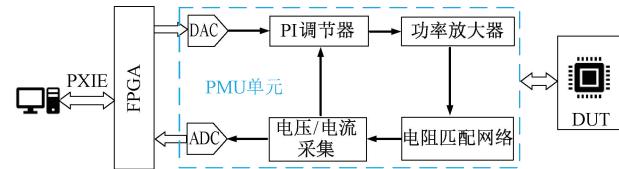

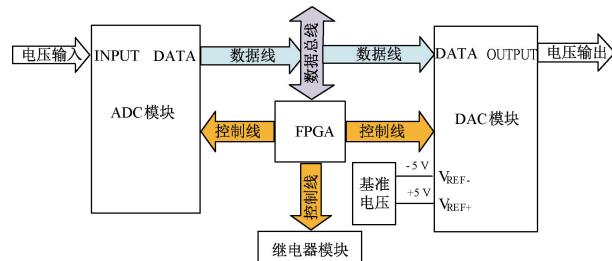

如图 1 所示,直流参数测试电路主要包括 DAC 模块、PI 调节器、功率放大器、电阻匹配网络、电压/电流采集电路和 ADC 模块等。FPGA 将来自上位机的测试指令转化为控制指令,DAC 输出电压激励信号经过 PI 调节、功率放大等对 DUT 施加设定的激励信号;采集电路获取被测器件引脚上的电压/电流参数,经 ADC 转换为数字量实现对

DUT 响应信号的测量。

图 1 PMU 系统设计框图

Fig. 1 Block diagram of PMU system design

## 2 精密测量单元的设计

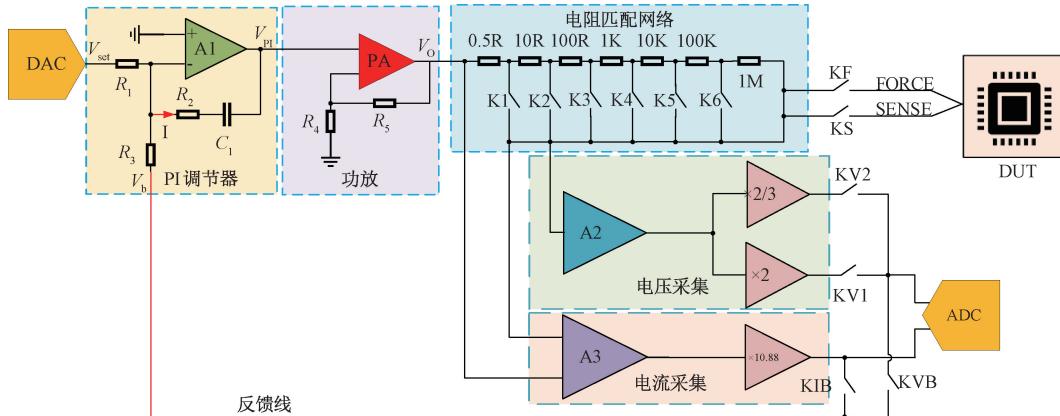

PMU 专用芯片由于受到功能的制约,测量范围有限<sup>[17]</sup>。为扩宽直流参数测试范围,提高测试精度,设计了一种如图 2 所示的 PMU 电路,实现对 DUT 施加激励,并获取测量值。

图 2 PMU 模块电路图

Fig. 2 PMU module circuit diagram

### 2.1 PI 和功放电路设计

如图 2 所示,为提高 PMU 电路环路响应速度及精度,得到稳定的输出;加入比例积分(proportional integral,PI)调节电路,通过积分运算消除设定偏差,DAC 输出电压  $V_{set}$  为设定值, $V_b$  是 ADC 采集的 DUT 电压/电流反馈信号。由于运算放大器 A1 反向输入端“虚地”,且  $R_1=R_3$ ,则流入 R2 的电流如式(1)所示。

$$I = \frac{V_{set}}{R_1} + \frac{V_b}{R_3} = \frac{V_e}{R_1} \quad (1)$$

式中: $V_e$  为 PI 调节器输入信号,输出如式(2):

$$V_{PI} = -\frac{R_2}{R_1} \times V_e - \frac{1}{R_1 \times C_1} \int V_e dt \quad (2)$$

改变电阻  $R_1$ 、 $R_2$  和电容  $C_1$  的数值,调整 PI 调节器的比例系数( $R_2/R_1$ )和积分系数( $1/(R_1-C_1)$ ),实现施加电压、电流的精准输出。功率放大电路 PA 选用 OPA544,实现输出电压/电流驱动,工作电压高达  $\pm 35$  V,最大持续输出电流 2 A。功率放大电压输出公式如式(3)所示。

$$V_o = (1 + \frac{R_5}{R_4}) \times V_{PI} = 3V_{PI} \quad (3)$$

### 2.2 工作模式设置

PMU 有 4 种工作模式:加压测流(force voltage measure current,FVMI)、加压测压(force voltage measure voltage, FVMV)、加流测压(force current measure voltage, FIMV) 和 加流测流(force current measure current, FIMI)。

如图 2 所示,继电器 KIV、KVB 分别控制 DUT 的电压/电流反馈到 PI 的输入端,使其工作在电压/电流模式。FV 工作模式时,KVB 闭合、KIB 断开, $V_b$  端接入电压反馈信号。KVB 闭合时,电压回路中 KV1、KV2 两个控制继电器,仅 KV1 闭合时对应 E1 电压档,DUT 电压经 2 倍放大反馈至  $V_b$  端。稳定输出时  $V_{set} = -V_b$ ,而  $V_{set}$  范围为  $\pm 10$  V,因此 E1 档电压范围  $\pm 5$  V。仅 KV2 闭合对应 E2 电压档,DUT 电压经  $2/3$  衰减接入  $V_b$  端,电压范围可达  $\pm 15$  V。MV 工作模式,2 个电压档的控制方式与参数同上。

电流工作模式时,KIB闭合、KVB断开,电流反馈信号接入 $V_b$ 端。更进一步,继电器K1~K6的通断选择不同采样电阻 $R_s$ ,根据式(4)得到相应的FI/MI电流。

$$I = \frac{V_b}{R_s \times 10.88} = -\frac{V_{set}}{R_s \times 10.88} \quad (4)$$

其中,10.88为电流放大器的放大倍数。K1~K6继电器全部断开时, $R_s=1\ 111\ 110.5\ \Omega$ ,对应I1档电流范围为 $\pm 827\ nA$ 。如表1所示,K6~K1依次闭合(其余断开)分别对应I2~I7共6个电流档。例如,仅有继电器K1闭合时对应I7档, $R_s=0.5\ \Omega$ ,电流范围 $\pm 1.838\ A$ 。

表1 PMU电路FI/MI电流档明细

Table 1 PMU circuit FI/MI current file breakdown

| 电流档位 | 控制继电器     | $RS/\Omega$ | 电流范围              |

|------|-----------|-------------|-------------------|

| I1   | K1~K6全部断开 | 1 111 110.5 | $\pm 827\ nA$     |

| I2   | 仅K6闭合     | 111 110.5   | $\pm 8.27\ \mu A$ |

| I3   | 仅K5闭合     | 11 110.5    | $\pm 82.7\ \mu A$ |

| I4   | 仅K4闭合     | 1 110.5     | $\pm 827\ \mu A$  |

| I5   | 仅K3闭合     | 110.5       | $\pm 8.31\ mA$    |

| I6   | 仅K2闭合     | 10.5        | $\pm 87.5\ mA$    |

| I7   | 仅K1闭合     | 0.5         | $\pm 1.838\ A$    |

### 2.3 PMU电路V/I功能EDA仿真

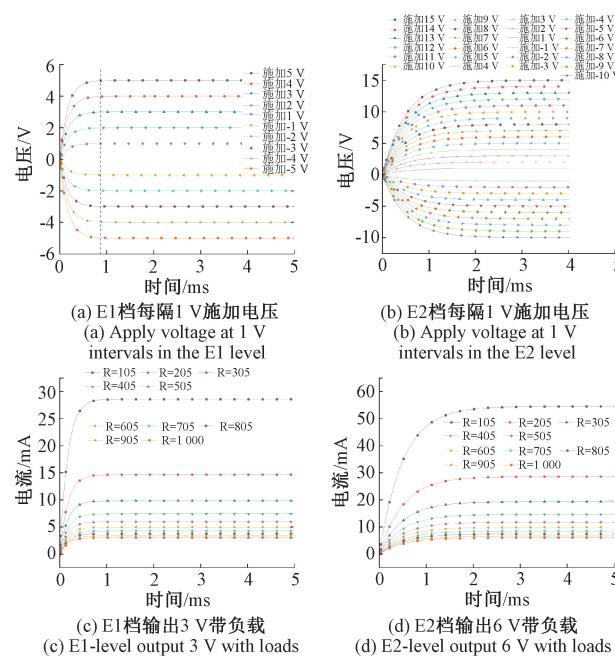

#### 1)施加电压模式

分别在E1、E2档对相同负载间隔1V进行EDA仿真数据分析,再对不同负载施加电压检测负载电流。

如图3(a)和(b)所示,在相同负载下E1档和E2档电压输出结果与理论分析一致。如图3(c)和(d)所示,以E1、E2档电压3V、6V为例,分别施加不同负载的电压输出达到预期设定值,并且能够正确输出对应电流。从图3可以看出E1档690μs施加电压达到目标的99%,E2档2.36ms施加电压达到目标的99%。

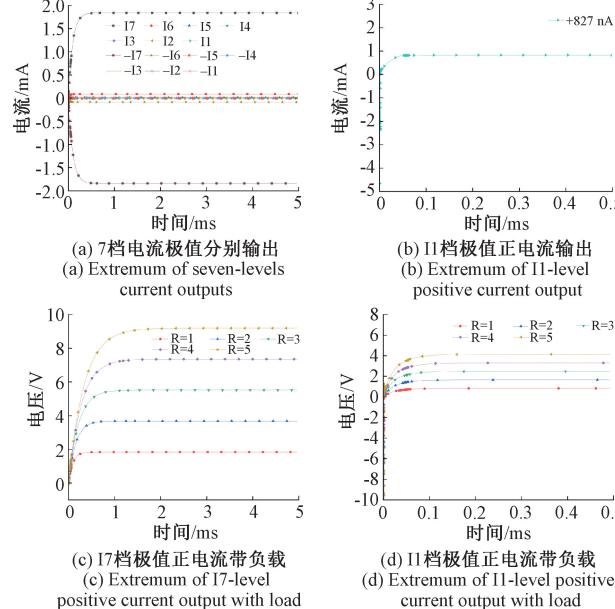

#### 2)施加电流模式

在施加电流模式下,如图4(a)分别对I1~I7共7个电流档位对相同负载施加相应档位最大正负电流,图4(b)给出施加最小电流的结果。I7档在453us时达到目标输出的99%,I1档在147us时达到目标输出的99%。使用不同负载施加电流,电流恒定,不同负载的电压相应变化如图4(c)和(d)所示,与理论分析结果一致。

### 3 精密测量单元电路逻辑控制

PMU电路系统采用Xilinx公司FPGA芯片作为主控制器,使用Verilog HDL硬件描述语言编程,实现对DAC、ADC模块的驱动以及对有关继电器的控制。

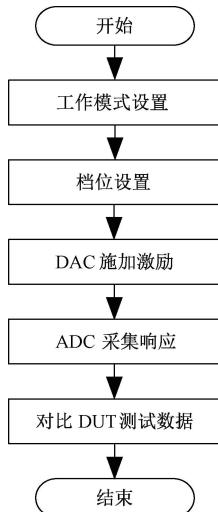

PMU电路逻辑控制框图如图5所示。FPGA指令控制继电器切换相应工作状态;配置DAC的控制时序,通过数据总线将设定值输入DAC模块,使其输出相应的激励

图3 施加电压仿真结果

Fig. 3 Simulation results of applied voltage

图4 电流施加电路仿真结果

Fig. 4 Current applied circuit simulation results

电压;同时控制ADC的读时序,从数据总线读回MV/MI的响应值。

PMU电路系统控制流程如图6所示,首先控制继电器对PMU的工作模式以及档位进行设置,再控制DAC施加激励,经调理后施加到被测器件,最后由ADC进行采样并读回响应值。

#### 3.1 DAC模块

DAC是PMU电路系统中施加高精度电压/电流的核

图 5 PMU 电路逻辑控制框图

Fig. 5 Logic control block diagram of precision measurement circuit system

图 6 PMU 控制流程图

Fig. 6 PMU control flow chart

心器件,设计选用 14 bits 分辨率的 DAC 专用集成电路 AD7841,施加激励的范围为  $\pm 10$  V,输出电压如式(5):

$$V_{out} = 2[V_{REF}(-) + \frac{CODE}{2^{14}} \times V_{REF}] \quad (5)$$

其中, CODE 为 FPGA 控制器设置的二进制数值,  $V_{REF} = V_{REF+} - V_{REF-} = 10$  V。

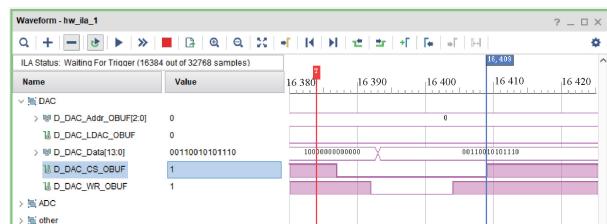

图 7 为 FPGA 对 DAC 控制时序波形。CS# 设置为低电平,拉低 WR# 不少于 50 ns 时间后,将设定数据 DATA 写入 AD7841 的寄存器中,使其输出对应的电压。

图 7 DAC 控制时序波形图

Fig. 7 DAC control timing waveform diagram

### 3.2 ADC 模块

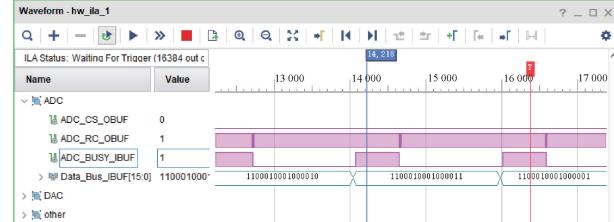

ADC 模块是实现对 DUT 的电压/电流参数的采集,

以及施加电压/电流的信号反馈,设计选用 16 bits 分辨率的 ADC 专用集成电路 LT1605。图 8 为 FPGA 对 ADC 控制时序波形及其输出数据的截图。其中,CS# 设为低电平,R/C# 拉低大于 40 ns 后再拉高。当 BUSY# 为低电平时,ADC 开始将模拟输入电压转换成数字信号,BUSY# 由低电平变为高电平时表示转换完成,此时输出数据有效。

图 8 ADC 控制时序波形图

Fig. 8 ADC control timing waveform diagram

### 4 实验结果分析

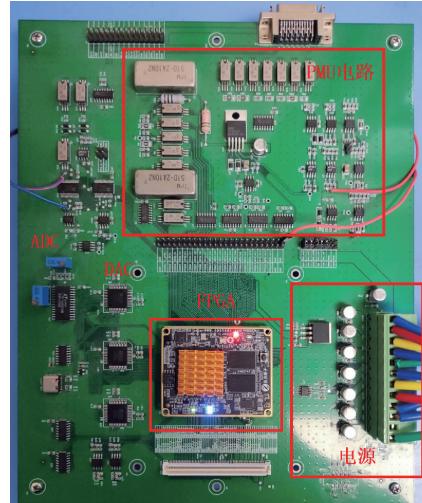

PMU 电路 PCB 如图 9 所示,在室温条件下,使用直流电源对设计的电路进行供电,通过 FPGA 实现对 ADC、PMU、DAC 等模块的逻辑控制。并设置电压/电流激励,待输出电压/电流稳定后,使用吉时利 2401 六位半数字源表测量施加的电压/电流值。

图 9 PMU 电路实物

Fig. 9 PMU circuit physical

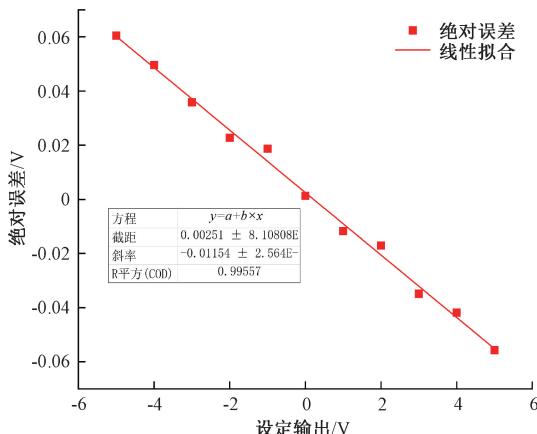

表 2 为  $\pm 5$  V 电压档位校准前的测量数据,从表中可以看出电路在校准前具有较大的误差,最大绝对误差为 0.060 49 V,最大满量程误差为 0.604 9%。

在理想情况下,电路输出与实际测量值相同,但由于环境的差异、电磁干扰、电路模块之间的干扰以及元器件自身偏差都可能导致误差产生,这些误差可分为随机误差和系统误差。其中随机误差可以通过多次测量求平均值的方法消除影响,系统误差往往是线性的偏移误差和增益误差,而此类误差适合使用最小二乘法进行曲线拟合对电

表2 ±5 V电压档位校准前测量数据

Table 2 Measured data before calibration at ±5 V voltage level

| 设定输出/V | 实际输出/V    | 绝对误差/V    | 满量程误差/%  |

|--------|-----------|-----------|----------|

| -5     | -4.939 51 | 0.060 49  | 0.604 9  |

| -4     | -3.950 32 | 0.049 68  | 0.496 8  |

| -3     | -2.964 15 | 0.035 85  | 0.358 5  |

| -2     | -1.977 28 | 0.022 72  | 0.227 2  |

| -1     | -0.981 31 | 0.018 69  | 0.186 9  |

| 0      | 0.001 31  | 0.0013 1  | 0.013 1  |

| 1      | 0.988 24  | -0.011 76 | -0.117 6 |

| 2      | 1.982 95  | -0.017 05 | -0.170 5 |

| 3      | 2.965 12  | -0.034 88 | -0.348 8 |

| 4      | 3.958 19  | -0.041 81 | -0.418 1 |

| 5      | 4.944 32  | -0.055 68 | -0.556 8 |

路进行校准<sup>[18]</sup>。

对表2中的绝对误差进行线性拟合,结果如图10所示,拟合度R<sup>2</sup>为0.9957,具有良好的线性度。在对电路进行校准后进行实验,测量结果如表3所示。校准后,电路的最大满量程误差为0.0333%。

图10 ±5 V电压档位未校准绝对误差

Fig. 10 Uncalibrated absolute error for ±5 V voltage level

表3 ±5 V电压档位校准后测量数据

Table 3 Measured data after calibration at ±5 V voltage level

| 设定输出/V | 设定输出/V    | 绝对误差/V    | 满量程误差/%  |

|--------|-----------|-----------|----------|

| -5     | -5.000 61 | -0.000 61 | -0.006 1 |

| -4     | -3.999 83 | 0.000 17  | 0.001 7  |

| -3     | -3.001 08 | -0.001 08 | -0.010 8 |

| -2     | -2.002 52 | -0.002 52 | -0.025 2 |

| -1     | -0.997 91 | 0.002 09  | 0.020 9  |

| 0      | -0.001 86 | -0.001 86 | -0.018 6 |

| 1      | 0.996 67  | -0.003 33 | -0.033 3 |

| 2      | 2.003 02  | 0.003 02  | 0.030 2  |

| 3      | 2.996 72  | -0.003 28 | -0.032 8 |

| 4      | 3.998 42  | 0.001 42  | 0.014 2  |

| 5      | 4.999 23  | -0.000 77 | -0.007 7 |

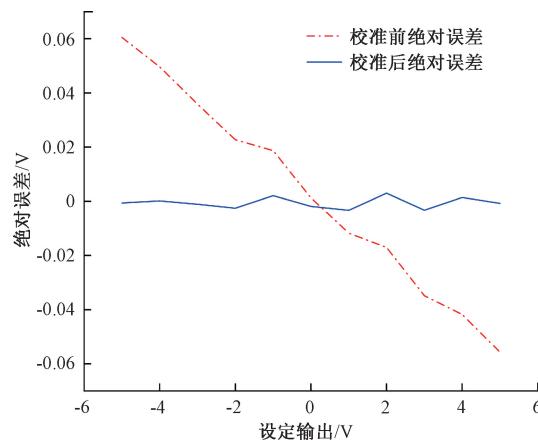

从图11将校准前测量数据绝对误差和校准后测量绝对误差进行对比,可以看出电路经过校准过后最大绝对误差由0.6049%降低到0.0333%,且整体误差明显降低。

图11 ±5 V电压档位校准前后输出误差

Fig. 11 Output error before and after calibration of ±5 V voltage level

表4为各个档位校准后误差数据,校准后的满量程误差在±1.838 A档位小于0.3%,其他档位整体小于0.05%。表明本设计实现了宽测试范围,高测试精度的优点。

表4 各个档位校准后误差数据

Table 4 Error data after calibration of each level

| 档位        | 最大绝对误差      | 满量程误差/% |

|-----------|-------------|---------|

| ±5 V      | 0.003 33 V  | 0.033 3 |

| -10~+15 V | 0.009 8 V   | 0.039 2 |

| ±827 nA   | 0.52 nA     | 0.031 4 |

| ±8.27 μA  | 0.007 26 μA | 0.043 9 |

| ±82.7 μA  | 0.040 6 μA  | 0.024 5 |

| ±827 μA   | 0.632 μA    | 0.038 2 |

| ±8.31 mA  | 0.007 82 mA | 0.047 1 |

| ±87.5 mA  | 0.068 3 mA  | 0.039 0 |

| ±1.838 A  | 0.008 A     | 0.217 6 |

表5为同类的测试系统的相关参数,在电流测试范围本文所设计电路具有显著的优势,可以测试电流最大±1.838 A的范围,在精度上,相较于文献[6]和文献[9]具有更高的电压精度,相较于文献[8]在同档位下具有更高的电流精度。

表5 同类测试系统相关参数

Table 5 Parameters related to similar test systems

| 测试系统  | 电压/电流范围       | 精度         |

|-------|---------------|------------|

| 文献[6] | ±40 V/±1 A    | 0.4%/0.3%  |

| 文献[8] | ±20 V/±80 mA  | 0.03%/0.1% |

| 文献[9] | ±20 V/±500 mA | 0.5%/0.1%  |

采用 0.1% 精密电阻作为负载, 设置激励电压/电流设定值, 待输出电压/电流稳定后, 在负载端使用六位半源表测量施加到精密电阻上的电压/电流值, 并计算出实际值

与理想值之间的相对误差。节选了两种测试模式在不同量程范围典型的测试结果, 结果如表 6 所示。

表 6 PMU 电路功能测试结果

Table 6 PMU circuit function test results

| 模式   | 负载/ $\Omega$ | 档位                            | 理想施加值            | 实际施加值                | MI/MV       |

|------|--------------|-------------------------------|------------------|----------------------|-------------|

| FVMI | 499          | $\pm 5\text{ V}$              | -3 V             | -2.998 7 V           | -6.009 1 mA |

|      | 499          | $\pm 5\text{ V}$              | 5 V              | 5.0011 V             | 10.021 8 mA |

|      | 499          | -10~+15 V                     | 12 V             | 11.9971 V            | 24.042 2 mA |

| FIMV | 499          | $\pm 82.7\text{ }\mu\text{A}$ | 50 $\mu\text{A}$ | 49.982 $\mu\text{A}$ | 24.944 mV   |

|      | 49.9         | $\pm 8.31\text{ mA}$          | 5 mA             | 4.997 6 mA           | 249.421 mV  |

|      | 49.9         | $\pm 1.838\text{ A}$          | 50 mA            | 49.976 8 mA          | 2.494 3 V   |

## 5 结 论

本文设计了一款用于集成电路测试设备的精密测量单元电路。该电路系统能够提供 FV/MV 电压 -15 V、+15 V, MI/FI 最大电流档  $\pm 1.838\text{ A}$ , MI/FI 最小电流档  $\pm 827\text{ nA}$ , 系统误差在  $\pm 1.838\text{ A}$  档位小于 0.3%, 其他档位小于 0.05%。所设计的精密测量电路测试系统, 具有使用方便, 操作简单, 便于升级和维护等特点, 为集成电路的直流参数测试提供了一种低成本解决方案, 其应用前景广阔。

## 参考文献

- [1] 罗宏伟, 刘竞升, 余永涛, 等. 超大规模集成电路测试现状及关键技术[J]. 电子产品可靠性与环境试验, 2021, 39(S2):16-20.

- [2] LUO H W, LIU J H, YU Y T, et al. Testing situation and key technology of ultra large-scale integrated circuit [J]. Electronic Product Reliability and Environmental Testing, 2021, 39(S2):16-20.

- [3] 黄林. 我国集成电路测试技术现状及发展策略[J]. 科技资讯, 2018, 16(20):37-38.

- [4] HANG L. China's integrated circuit test technology status quo and development strategy[J]. Science & Technology Information, 2018, 16(20):37-38.

- [5] 徐志君. 集成电路测试技术的应用研究[J]. 电子测试, 2018,(9):93,114.

- [6] XU Z J. Research on application of integrated circuit testing technology[J]. Electronic Test, 2018,(9):93,114.

- [7] 孔宪伟, 李秦华. 集成电路测试与标准化领域研究综述[J]. 信息技术与标准化, 2023(7):39-43.

- [8] KONG X W, LI Q H. Overview of research in IC testing and standardization field [J]. Information Technology & Standardization, 2023(7):39-43.

- [9] 马宁, 韩磊. 模拟 IC 自动测试系统的直流参数测试单元[J]. 电子设计工程, 2014, 22(12):121-123.

- [10] 张为, 王佳琪, 童炜. 一种高精度直流参数测试系统的设计与实现[J]. 天津大学学报(自然科学与工程技术版), 2020, 53(12):1288-1294.

- [11] ZHANG W, WANG J, TONG W. Design of an integrated circuit test system for DC parameters[J]. Journal of Tianjin University(Science and Technology), 2020, 53(12):1288-1294.

- [12] 张玺, 王硕, 童炜, 等. 一种用于三维闪存测试的低成本 PMU 电路[J]. 微电子学与计算机, 2020, 37(5):1-5.

- ZHANG X, WANG Q, TONG W, et al. A low-cost PMU circuit for 3D NAND Flash memory testing[J]. Microelectronics & Computer, 2020, 37(5):1-5.

- [12] 刘媛媛,高剑,蒋常斌.基于ATE的MCU芯片并行测试技术研究[J].电子测量技术,2020,43(4):116-120.

- LIU Y Y, CAO J, JIANG C B. Research on parallel testing technology of MCU chip based on ATE[J]. Electronic Measurement Technology, 2020, 43 (4): 116-120.

- [13] 王香芬,欧阳骁哲,张鸿军,等.基于信号传输完整性的通用测试接口板设计[J].国外电子测量技术,2022, 41(5):149-154.

- WANG X F, OUYANG X ZH, ZHANG H J, et al. Design of universal test interface board based on signal integratit [J]. Foreign Electronic Measurement Technology, 2022,41(5):149-154.

- [14] 周建.混合集成电路测试板FPGA逻辑设计[D].成都:电子科技大学,2014.

- ZHOU J. Logic design of mixed-signal IC ATE based on FPGA [D]. Chengdu: University of Electronic Science and Technology of China,2014.

- [15] 陈昆,刘丹.集成电路测试技术研究[J].电子元器件与信息技术,2020,4(8):12-14.

- CHEN K, LIU D. Integrated circuit test technology research[J]. Electronic Component and Information Technology, 2020,4(8):12-14.

- Technology, 2020,4(8):12-14.

- [16] 倪宋斌,马美铭.集成电路成品测试的常见问题分析[J].电子与封装,2023,23(12):24-27.

- NI S B, MA M M. Analysis of common problems in finished integrated circuit testing [J]. Electronics & Packaging, 2023,23(12):24-27.

- [17] 王佳琪.基于FPGA的3D NAND Flash直流参数测试系统的设计与实现[D].天津:天津大学,2019.

- WANG J Q. Design of integrated circuits test system for 3D NAND Flash of DC parameter [D]. Tianjin: Tianjin University,2019.

- [18] 杨莫非,刘士兴,廖福宁,等.基于ARM的实验室数字源表设计[J].电子测量技术,2021, 44 (7): 165-169,178.

- YANG M F, LIU SH X, LIAO F N. et al. Design of laboratory source meter based on ARM[J]. Electronic Measurement Technology, 2021,44(7):165-169,178.

### 作者简介

夏进,硕士研究生,主要研究方向为集成电路测试和可编程器件与集成系统设计。

E-mail:jinboy1997@163.com

刘士兴(通信作者),博士,副教授,硕士生导师,主要研究方向为集成电路测试技术、机器视觉与智能制造、电子测量及核电子学、可编程器件与集成系统设计等。

E-mail:liusx@hfut.edu.com