DOI:10.19651/j.cnki.emt.2415598

# 基于温度传感阵列的 TSV 内部缺陷检测技术研究<sup>\*</sup>

聂磊<sup>1</sup> 于晨睿<sup>1</sup> 张鸣<sup>1</sup> 骆仁星<sup>2</sup>

(1. 湖北工业大学机械工程学院 武汉 430068; 2. 湖北泰和电气有限公司 襄阳 441057)

**摘要:** 在 TSV 三维集成领域,由于 TSV 内部缺陷的微小化和检测的不可接触性,寻找一个无损、灵敏且高效的内部缺陷检测方法尤为重要。针对这一挑战,提出了一种基于温度传感阵列的 TSV 内部缺陷检测方法。内部缺陷对 TSV 三维封装芯片的外部温度分布产生了影响,这些温度分布呈现出有规律的变化,每一种缺陷类型都会导致外部温度分布产生不同的偏差。利用温度传感阵列测量这些分布变化对缺陷进行有效的识别与分类。根据工作状态下的芯片产生的热信号以揭示其内部的缺陷信息,设计了基于温度传感阵列的检测系统。通过理论分析与仿真模拟,构建了模拟芯片工作状态下的温度分布和热变化的模型。实验中,以芯片样品的样本制备和测试平台搭建为基础,同时利用分类识别模型成功实现了对内部缺陷的有效分类,准确率高达 99.17%。这种检测方法为高密度和微型化芯片的可靠性分析和故障诊断提供了一个经济高效的新途径。

**关键词:** 硅通孔; 内部缺陷; 传感阵列; 检测技术; LSTM

中图分类号: TN305.94 文献标识码: A 国家标准学科分类代码: 520.2050

## Research on TSV internal defect detection technology based on temperature sensing array

Nie Lei<sup>1</sup> Yu Chenrui<sup>1</sup> Zhang Ming<sup>1</sup> Luo Renxing<sup>2</sup>

(1. School of Mechanical Engineering, Hubei University of Technology, Wuhan 430068, China;

2. Hubei Taihe Electric Co., Ltd., Xiangyang 441057, China)

**Abstract:** In the field of TSV 3D integration, due to the miniaturization of internal defects and the challenges associated with non-contact detection, identifying a non-destructive, sensitive, and efficient method for internal defect detection is crucial. In response to this challenge, a TSV internal defect detection method based on a temperature sensor array has been proposed. Internal defects influence the external temperature distribution of TSV 3D packaged chips, displaying regular patterns of change. Each type of defect causes different deviations in the external temperature distribution. By utilizing a temperature sensor array to measure these distribution changes, effective identification and classification of defects can be achieved. A detection system, based on the temperature sensor array, was designed to reveal the internal defect information based on the thermal signals generated by chips under operational conditions. Through theoretical analysis and simulation modeling, a model simulating the temperature distribution and thermal changes of chips under working conditions was developed. In the experiments, based on the preparation of chip samples and the setup of a testing platform, effective classification of internal defects was achieved using a classification recognition model, reaching an accuracy rate of up to 99.17%. This detection method provides a cost-effective and efficient new approach for the reliability analysis and fault diagnosis of high-density and miniaturized chips.

**Keywords:** silicon via; internal defects; sensor array; detection technology; LSTM

## 0 引言

硅通孔(through-silicon via, TSV)是三维集成封装的前沿技术,为芯片内部及各芯片之间提供了高效的垂直电

路连接手段<sup>[1]</sup>。该方法通过多芯片堆叠与垂直互联,极大地提高了集成度与性能。TSV 不仅缩短了信号传输路径,降低了功耗,还实现了更高的电路密度和更加紧凑的芯片设计<sup>[2]</sup>。因此,TSV 技术对芯片性能和功能带来了较大提

升,被广泛应用于各式各样的高科技领域<sup>[3]</sup>。然而,TSV 制造工艺的复杂性,特别是包括刻蚀、沉积和电镀等众多步骤,可能引入诸如不均匀刻蚀、杂质残留等内部缺陷<sup>[4]</sup>。随着微电子封装微型化和高密度化,对芯片内部的故障定位与缺陷诊断变得要求更高,使得 TSV 缺陷检测成为集成电路封装领域中一个急需解决方案的重大挑战<sup>[5]</sup>。

在三维集成电路的封装中,TSV 三维封装芯片的完整性检测是保证产品性能的关键步骤。缺陷检测方法通常分为接触式和非接触式两大类<sup>[6]</sup>。接触式检测较为常见的有电学检测,这种方法可以精确评估电子产品的电性能,但也存在一些隐患。Jun 等<sup>[7]</sup>提出了一种基于自偏置电流参考源(self-calibrating reference source,SCRS)的充放电技术,用于检测和识别 TSV 的故障。这种技术通过测量充电时间来实现对开路、漏电和复合故障的检测与鉴别。SCRS 技术通过延长 TSV 充放电过程,提高了故障检测的准确性。然而在对 TSV 芯片进行完整性和性能测试时,可能引入机械性损伤。此外,非接触式检测方法,如光学检测、X 射线成像、声学检测法和红外热成像等都各有其局限性。Park 等<sup>[8]</sup>提出了一种基于无监督学习的异常检测检查方法用于检测芯片缺陷,该方法不需要标记数据,能够解决传统监督学习方法需要繁琐劳动和难以获得各个类别的平衡数据集的问题。然而这种检测通常局限于表层缺陷,而内部细微缺陷则难以捕捉。X 射线成像技术能透视三维封装芯片内部结构,提供细节丰富的内部图像<sup>[9]</sup>。Yuan 等<sup>[10]</sup>提出了一种利用磁场成像和高分辨率三维 X 射线显微镜来检测 TSV 三维封装芯片中开路缺陷的方法。他们采用高分辨率三维 X 射线显微镜进行多次分区扫描,实现亚微米级别的分辨率。但辐射剂量可能对芯片长期性能造成影响<sup>[11]</sup>,X 射线产生的电离辐射会对芯片中的敏感电子元件产生损害。Eva 等<sup>[12]</sup>利用扫描声学显微镜来检测三维封装中的金属化缺陷方法,通过分析干涉图案可确定是否存在缺陷。该检测技术具有非接触、无损、高分辨率等优点,但耦合剂残留可能对微细的电子构造造成腐蚀,导致检测后的清理和维护成本增高。Jeon 等<sup>[13]</sup>研究者将红外成像与深度学习技术相结合,进行电路板元件的故障检测。该研究使用卷积神经网络来识别电路板中的缺陷。然而,由于分辨率限制该方法在稳态条件下难以区分正常和故障状态<sup>[14]</sup>。Nie 等<sup>[15]</sup>提出一种基于系统内集成传感器的高密度 TSV 三维封装在线检测方法,对 TSV 三维封装芯片进行电热激励复合条件下的缺陷诊断。然而该方法成本较高,难以进行实际工程应用。综上所述,目前 TSV 缺陷检测技术已取得一定进展,仍需针对大规模工程实际应用开发出无损且更为高效的检测方法。

基于当前 TSV 缺陷检测技术的局限性,本文提出了一种基于温度传感阵列的 TSV 封装内缺陷检测方法。该方法采用外部温度传感阵列采集工作过程中的芯片表面的时序温度信号,并将所采集的数据输送至计算机系统进行深

入分析。此方法作为一种非侵入式检测方法可以避免对芯片内部造成影响,同时可以实时监测芯片工作时的温度变化,有效地进行缺陷分类及识别。本文通过综合理论分析与仿真模拟,深入掌握缺陷如何影响温度场的分布和变化,并据此指导实验设计;由于微小缺陷引起的温度场变化非常小,肉眼难以直接识别这些细微差别,故通过深度学习方法对温度数据进行多类别识别,并构建出一套分类识别模型;本文还包括 TSV 样品制备和测试平台搭建,模拟 TSV 三维封装芯片的实际工作,并通过温度传感阵列收集温度分布数据,在时间序列上建立温度分布矩阵,进而利用分类模型实现缺陷检测。这种检测方法无需破坏芯片即可对 TSV 内部缺陷进行高效诊断,并且成本低廉、检测迅速,预示着它在实际应用中具有广阔的发展潜力。

## 1 检测原理及方法

### 1.1 检测原理

TSV 三维封装芯片在通电工作时,其内部的热平衡状态被扰乱<sup>[16]</sup>,需要借助建立导热微分方程来表达 TSV 三维封装芯片内部热传导的规律<sup>[17]</sup>。根据一维热传导公式,对于  $x$  方向上:

$$\frac{\partial T}{\partial t} = \alpha \frac{\partial^2 T}{\partial x^2} \quad (1)$$

其中,  $T(x, t)$  是温度的空间和时间分布;  $t$  是时间;  $x$  是空间坐标;  $\alpha$  是热扩散系数。将  $x$  扩展到三维空间坐标  $x, y, z$  同时考虑三维温度分布  $T(x, y, z)$  可得出三维热传导方程:

$$\frac{\partial T}{\partial t} = \alpha \left( \frac{\partial^2 T}{\partial x^2} + \frac{\partial^2 T}{\partial y^2} + \frac{\partial^2 T}{\partial z^2} \right) \quad (2)$$

这个方程描述了温度随时间和 3 个空间坐标的演化。在这个方程中,  $\alpha$  仍然是热扩散系数,它是与材料的热导率  $k$ 、密度  $\rho$  和比热容  $c$  相关的量,即:

$$\alpha = \frac{k}{\rho c} \quad (3)$$

当 TSV 三维封装芯片内部存在缺陷时,缺陷区域的热物理性质与完好部分有所不同,会导致热导率  $k$  和比热容  $c$  在缺陷邻域内的变化。由于这些物理量直接决定了热扩散系数  $\alpha$ ,缺陷的出现会使得热传导方程的某些参数在空间上呈现非均匀性。因此,存在缺陷时,热传导方程应为

$$\frac{\partial T}{\partial t} = \nabla \cdot [\alpha(x, y, z) \nabla T] + q(x, y, z, t) \quad (4)$$

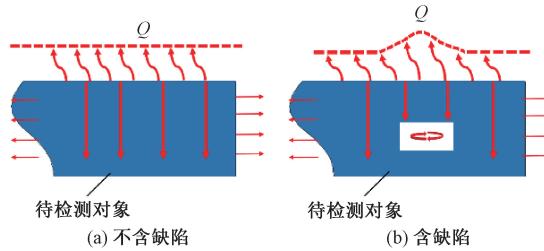

其中,  $\alpha(x, y, z)$  反映了由于缺陷造成的热扩散系数的变化,  $q(x, y, z)$  表示缺陷导致的局部内热源。由式可知,缺陷降低了局部区域的热传导能力,使得相应区域积累或散失热量的速度不同于无缺陷区域,导致局部温度升高或降低。如图 1(a)和(b)所示,分别为不含缺陷和含缺陷的待测对象的传热示意图。基于该理论分析,本文考虑使用外置温度传感阵列采集芯片表面的温度信号,并对不同缺

陷下芯片的差异温度信号进行分析处理,从而可对芯片内部缺陷进行定性分析及定量评价。

图1 缺陷对芯片表面温度影响示意图

## 1.2 检测方法

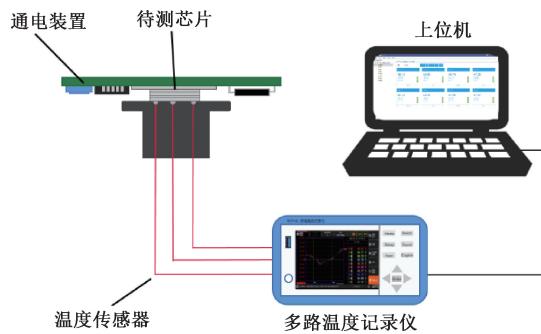

为检测三维封装芯片内的TSV缺陷,本文依托于芯片在运行中因电流通过引起的耗散热量,以此揭示温度特征信息。在TSV存在填充缺失时,相应的硅通孔不会负载电流,导致该区域的热特征差异。类似地,当TSV中存在铜柱底部空洞时,电流载荷的变化将影响热能的耗散。这两类结构性缺陷都有可能妨碍芯片达到预期的处理能力或改变其电路响应顺序,从而引起功耗速率的改变<sup>[18]</sup>。这些变化最终表现为芯片表面温度随时间的差异,可通过其大小和分布的差异来进行识别。为了辨识TSV内部不同的隐藏缺陷,本文设计了一个综合检测系统。如图2所示,该系统由3个关键模块组成:1)供电模块,用于向芯片提供稳定的电流;2)温度传感模块,负责实时采集芯片表面温度数据;3)信号分析模块,用于处理采集到的数据并进行缺陷分类识别。在整个检测流程中,供电模块通过施加电压激活芯片至正常工作状态,以诱发那些隐藏缺陷的热反应。采集到的温度数据被温度传感模块收集,并被送至信号分析模块,以进行后续的数据分析,实现对内部缺陷的精细分类与识别。这一连贯的检测过程能够准确定位并识别TSV缺陷。

图2 基于温度传感阵列的检测系统

为了提高实验数据的准确性,最小化测量误差对检测系统的干扰,本文提出了一种高频率的数据采集方案。具体实践中,本文设置系统以次/s频率采集温度数据,连续进行60 s,获得了一个完整的含有60个时间点的温度数据序列,并将这些数据实时传送至信号分析模块进行深入的数据处理。

考虑到采集的温度信号中的微弱差异难以通过肉眼观察直接分辨,本文采用深度学习的方法来对实验数据进行处理。该方法能够对不同类型的缺陷做出精确的识别和分类,从而提升检测系统的效能。

## 2 仿真分析

### 2.1 模型建立

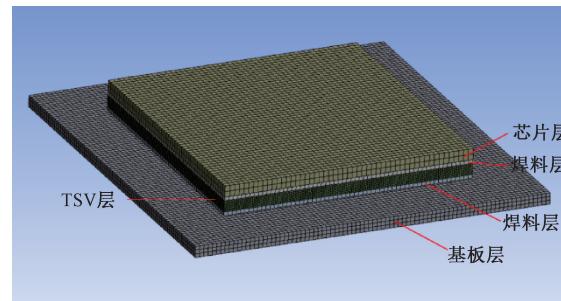

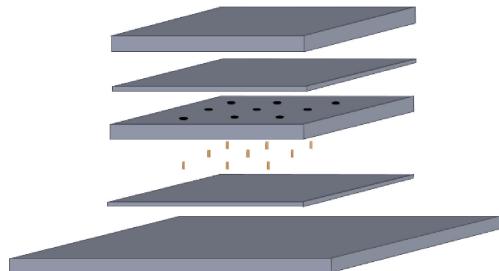

为验证本文提出的基于温度传感阵列的TSV内部缺陷检测方法的可行性,探究工作电信号下不同缺陷类型对TSV温度场分布的影响,本文建立了一个基于TSV三维封装制造工艺的模型,使用有限元分析软件进行仿真分析。模型结构如图3所示,顶层是以硅为核心材料的芯片层;其次是上下对称分布的、由树脂材质构成的焊料层;然后是内含3×3的TSV铜柱阵列TSV层,以硅为填充材料;最后是以硅为主要材料的基板层。TSV三维封装模型的仿真物理参数如表1所示。

图3 TSV三维封装仿真模型结构

表1 模型材料的物理属性

| 材料   | 长/mm | 宽/mm | 高/ $\mu\text{m}$ | 半径/ $\mu\text{m}$ |

|------|------|------|------------------|-------------------|

| 铜柱   | —    | —    | 300              | 50                |

| 硅芯片  | 7    | 7    | 300              | —                 |

| 基板   | 10   | 10   | 300              | —                 |

| 焊料   | 7    | 7    | 100              | —                 |

| TSV层 | 7    | 7    | 300              | —                 |

### 2.2 计算求解

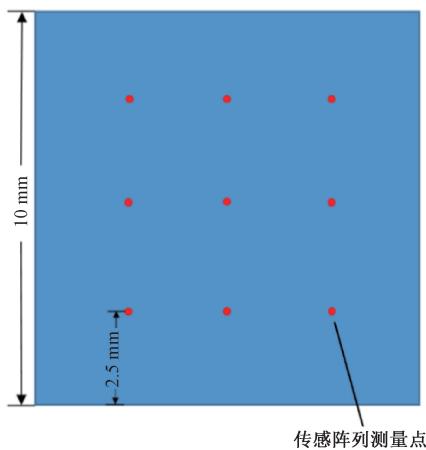

在芯片层上表面施加1.5 V的电压,对TSV层的各铜柱底面施加零电位。为了全面捕捉基板层底部的温度变化趋势,本文对温度传感阵列的采集点进行了均匀分布的设计。在平衡效能最大化与经济成本之间,本文选择了在模拟过程中温度变化幅度较大的区域作为温度采集点。这个策略反映了基板底部的温度变化,并确保数据的代表性和准确性。因此,本文选择在基板层四等分点处设置传感阵列测量点,具体位置如图4所示。

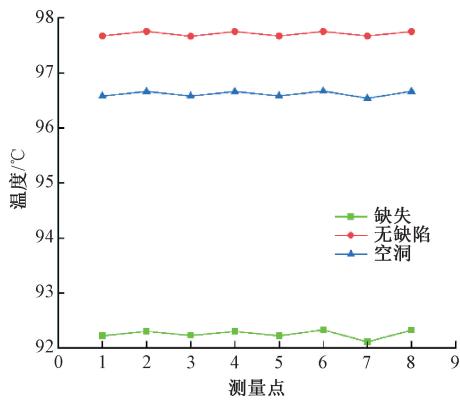

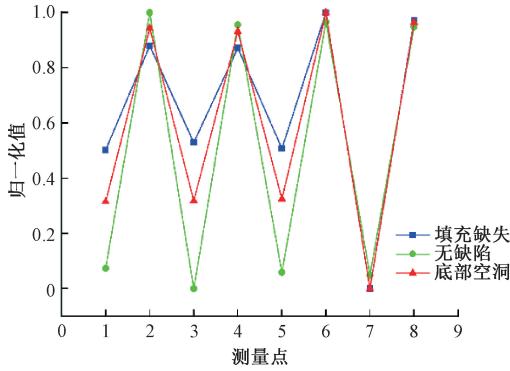

在经过有限元求解后得到了无缺陷、填充缺失和底部缺陷3种TSV三维封装模型基板层的测量点温度数据,如图5所示。针对不同缺陷下的8个测量点温度数值进行了

图 4 传感阵列测量点示意图

归一化处理,以消除不同特征之间的量纲影响和数值范围差异。从而得到了不同缺陷下测量点温度序列的归一化值,如图 6 所示。通过图示,可以清晰地观察到正常与不同缺陷下的 TSV 三维封装芯片在有限元求解后各测量点之间的温度变化趋势差异。初步验证了本文提出的基于温度传感阵列的 TSV 内部缺陷检测方法的可行性。在下一步的研究中,本文计划通过设计基于温度传感阵列的 TSV 内部缺陷检测实验进一步证明该方法的有效性。

图 5 TSV 三维封装模型测量点温度

图 6 归一化值

### 3 实验验证

#### 3.1 实验样品设计与制备

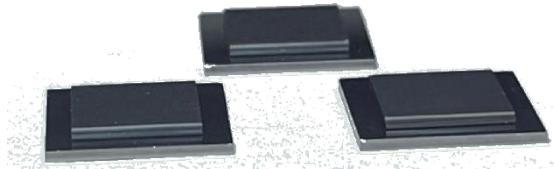

为进行基于温度传感阵列的 TSV 内部缺陷检测实验,本文制备了 TSV 三维封装缺陷样品,样品各层结构如图 7 所示,部分实验样品实物如图 8 所示。根据 TSV 内部缺陷的种类可分为底部空洞、填充缺失以及无缺陷 3 种。为了模拟 TSV 芯片正常工作产生热量以表达温度特征信息,本文在 TSV 层和芯片层之间引入了聚酰亚胺发热膜。填充缺失缺陷表现为 TSV 层上激光刻蚀半径 50  $\mu\text{m}$  的通孔,而底部空洞缺陷则表现为 TSV 层上激光刻蚀半径 50  $\mu\text{m}$  的盲孔。

图 7 TSV 三维封装芯片结构图

图 8 部分实验样品图

各层芯片制备完成后,执行键合操作。为了保证实验与仿真的对比一致性,构造了一个由芯片层、聚酰亚胺发热膜、TSV 层、基板层按顺序组成的完整结构。TSV 层位于模型的中心位置,其上下两侧分别通过焊料层与芯片层和基板层进行连接。

#### 3.2 基于温度传感阵列的检测实验

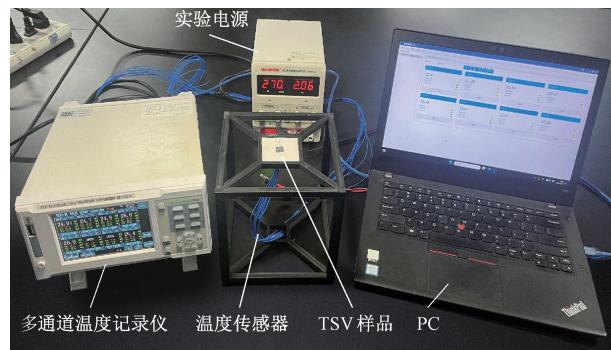

搭建的温度传感阵列实验系统如图 9 所示,包括温度记录仪、待测样品、移动实验电源、温度检测台、K 型热电偶丝以及上位机。在实验中,本文选择 TCP-XL 温度采集仪,该记录仪支持同时进行多通道温度采集,最小采样周期可达 100 ms。8 根 K 型热电偶丝嵌入温度检测台,形成了温度传感阵列。为了使样品的稳态温度与实际芯片正常工作时的温度相匹配,设置输出电压为 3.3 V,以将样品的稳态温度维持在约 50 °C。

在实验过程中,本文将环境温度控制在 25 °C。样品通过聚酰亚胺发热膜施加固定电压,模拟通电发热。通过安装在温度检测台中的热电偶丝采集样品底部的温度阵列。上位机控制温度采集仪,采集温度数据进行后续的测试和分析。检测过程如下:

图9 温度传感阵列实验系统图

1)放置样品。将样品稳定置于温度检测台中央,使得温度传感器阵列对准要测量的区域。

2)通电工作。调整实验电源,为样品施加电压,以模拟真实工作状态下的热响应。

图10 各通道测量温度

### 3.4 基于长短期记忆网络的数据处理

#### 1)模型构建

本文聚焦于TSV三维封装芯片内部隐藏缺陷的分类与识别问题。在实际检测过程中所采集的数据表现为时间序列数据矩阵。由于缺陷隐藏于TSV三维封装芯片内部,其信息表征不够明显。为了有效解决这一问题,本文采用了深度学习网络以进行精确的分类识别<sup>[19]</sup>。在时间序列分类(time series classification, TSC)领域,长短期记忆网络(long short-term memory, LSTM)表现出了比较好的应用效果<sup>[20]</sup>。LSTM作为一种特殊类型的循环神经网络(recurrent neural network, RNN),能够捕捉时间序列数据中长期的依赖关系<sup>[21]</sup>。因此,本文选择了长短期记忆网络作为核心检测模型,长短期记忆网络结构如图11所示。模型中的LSTM层负责从数据中提取关键特征。为防止模型过度拟合训练数据,引入了Dropout策略,该策略能够随机丢弃部分LSTM层输出。利用LSTM网络的高效特征提取能力,结合Dropout提高泛化,对内部缺陷实现高精

3)数据采集。按预设频率,通过温度记录仪和计算机系统收集温度数据,形成用于分析的时间序列温度矩阵。

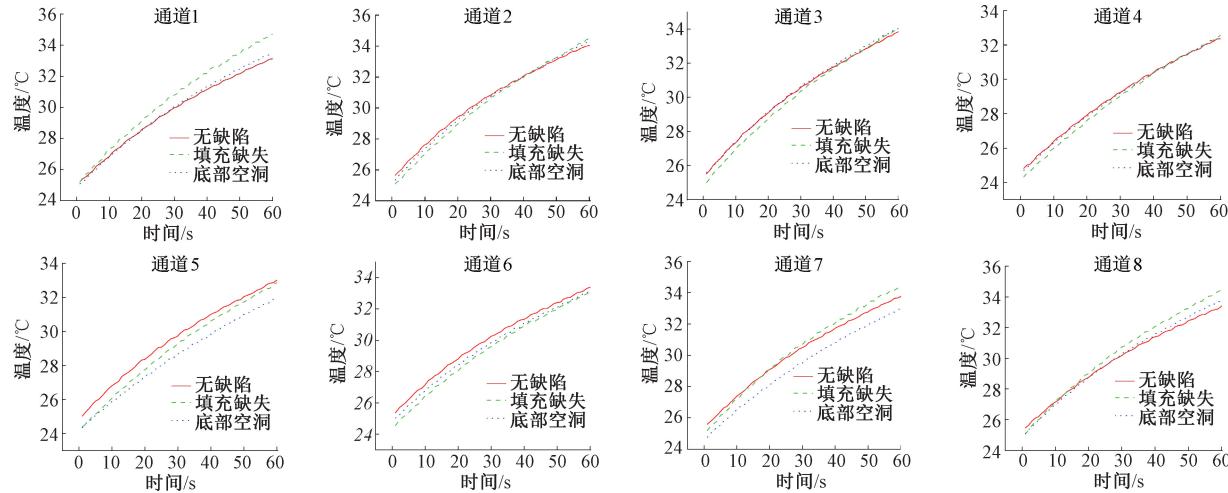

### 3.3 实验结果分析

实验采集的各通道温度数据如图10所示,分别展示了在不同情况下的温度信号:包括无缺陷的芯片样本、存在填充缺失以及底部空洞的样品。由图可知,随着持续的工作电信号,可以观察到各个通道的温度都在持续上升。然而,由于缺陷的存在,各个通道的上升趋势发生了明显变化,初步呈现出可区分的特征。举例来说,底部空洞样品与无缺陷样品相比,通道5的温度超过了通道4,通道8的温度超过了通道7,与无缺陷情况下相反;而填充缺失样品与无缺陷样品相比,通道7的温度高于通道3,通道1的温度最高,与无缺陷情况下通道2的情况相反。这些观察结果为初步判别和区分不同缺陷类型提供了有力的依据,为之后通过算法进一步识别和分类缺陷类型奠定了基础。

图11 LSTM网络结构

#### 2)缺陷识别与定量分析

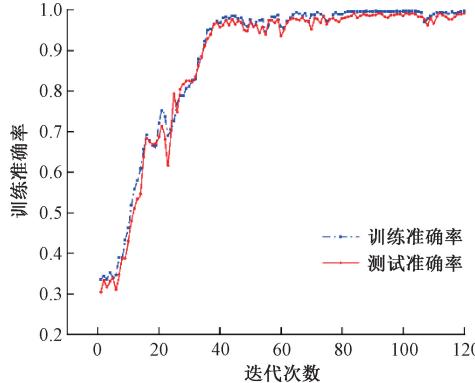

实验采集的数据构建了一个包含3个类别的实验数据集,总计2400组温度数据矩阵。每个类别包含800组温度数据矩阵,按照7:3的比例随机划分为训练集和测试集,即每个类别的测试集包含240组温度数值矩阵。用LSTM分类模型进行训练,并针对实验数据的特点进行了超参数调整,其中batchsize设置为128,learning-rate为 $3 \times 10^{-5}$ ,epoch为120。

在该模型下,训练和验证的准确率变化如图12所示。

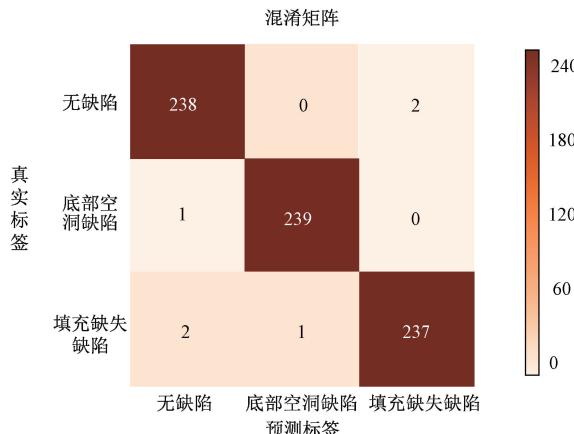

训练准确率和验证准确率均呈稳健上升并趋于平稳。使用混淆矩阵作为检测效果的评价指标,图 13 展示了横坐标为预测标签,纵坐标为真实标签。模型对于数据的预测类别与其真实类别相同时即为分类正确。据计算,该网络对于仿真数据的各类型缺陷分类识别准确率可达 99.17%。

图 12 LSTM 模型训练过程

图 13 混淆矩阵

结合有限元求解结果、实验数据以及 LSTM 网络对实验数据的分类效果,可以得出以下总结:1) 基于热传导理论的有限元分析揭示,在 TSV 三维封装芯片内部的铜柱存在缺陷时,通电工作引起整个三维封装系统热平衡的变化,对芯片表面温度产生显著影响。在热电耦合场的影响下,有限元分析呈现了不同缺陷下芯片模型表面温度信号的显著差异,初步证实了基于温度传感阵列的 TSV 内部缺陷检测方法的可行性。2) 实验进一步证实了该检测方法的可行性。通过制备无缺陷、底部空洞、填充缺失 3 种芯片样品,在搭建的实验平台上执行设计好的实验方案,成功采集了实验数据并进行了结果分析。这一步骤为有限元分析提供了实际验证,巩固了方法的可靠性和实用性。3) 利用实验所得数据构建了实验数据集,并且用 LSTM 网络进行分类,其分类准确率可达 99.17%,表明该方法能够有效地辨别 TSV 三维封装芯片内部的隐藏缺陷

类型。该方法与当前在 TSV 三维封装芯片缺陷检测领域应用较多的 X 射线检测法相比<sup>[22]</sup>,X 射线法可检测出 TSV 三维封装芯片内置铜柱缺陷最小直径可达 50  $\mu\text{m}$ ,而本方法目前检测缺陷的最小直径为 100  $\mu\text{m}$ ,然而本方法无需特殊制样,检测效率较高,且检测系统结构简单,环境兼容性好,易于与产线结合,因此更适用于工程大规模应用。

## 4 结 论

本文聚焦于 TSV 三维封装内部隐藏缺陷的检测问题,提出了一种创新的基于温度传感阵列的检测方法。首先对 TSV 内部的热传导机制进行深入分析,基于此分析建立 TSV 三维封装模型,并采用有限元方法对不同缺陷类型进行了精确模拟。通过实验平台的建立,执行带有模拟在线检测的实验,激励芯片样本并捕捉其热特征以揭示内部缺陷。利用实验所采集的数据创建了涵盖 3 种缺陷类型的温度时序数据集,通过 LSTM 神经网络模型实现了对数据的高准确率分类。这种方法相较于传统技术,不仅准确度高,速度快,且无需直接干预芯片,减少了损坏风险,为三维封装可靠性分析领域提供了一种低成本、高效能的解决方案。

## 参考文献

- [1] 王伟, 杨国兵, 方芳, 等. 通过面积扩张和散热硅通孔的 3DIC 热量的优化[J]. 电子测量与仪器学报, 2014, 28(7): 748-754.

- [2] SHEN H A S, KIM B J, KIM J H, et al. Microstructure evolution and defect formation in cu Through-silicon vias (TSVs) during thermal annealing[J]. J Electron Mater, 2012, 41(4): 712-719.

- [3] 谢俊, 黄春跃, 梁颖, 等. 三维堆叠封装 TSV 互连结构热扭耦合应力分析与优化[J]. 电子元件与材料, 2023, 42(9): 1129-1135, 1142.

- [4] PAN Y X, LI F, HE H, et al. Effects of dimension parameters and defect on TSV thermal behavior for 3D IC packaging[J]. Microelectronics Reliability, 2017, 70: 97-102.

- [5] SHEN J J, CHEN P F, SU L, et al. X-ray inspection of TSV defects with self-organizing map network and otsu algorithm[J]. Microelectronics Reliability, 2016, 67: 129-134.

- [6] 杨桂华, 唐卫卫, 卢澎澎, 等. 基于机器视觉的芯片引脚测量及缺陷检测系统[J]. 电子测量技术, 2021, 44(18): 136-142.

- [7] LIU J, CHENG S, CHEN T, et al. A self-biased current reference source-based pre-bond TSV test solution[J]. IEEE Transactions on Very Large Scale Integration(VLSI) Systems, 2023: 1-8.

- [8] PARK S, KO J H. Robust inspection of micro-LED chip

- defects using unsupervised anomaly detection[C]. 2021 IEEE International Conference on Information and Communication Technology Convergence (ICTC), 2021: 1841-1843.

- [9] 徐伟峰, 胡俊武, 叶佳佳, 等. 基于视觉检测的口罩枕包并联机器人动态抓取[J]. 国外电子测量技术, 2022, 41(3): 152-157.

- [10] CHEN Y, LAI P, HONG-ZHONG H, et al. Open localization in 3D package with TSV daisy chain using magnetic field imaging and high-resolution three-dimensional X-ray microscopy[J]. Appl. Sci. 2021, 11, 8148.

- [11] HUGHES H L, BENEDETTO J M. Radiation effects and hardening of MOS technology: Devices and circuits[J]. IEEE Transactions on Nuclear Science, 2003, 50(3): 500-521.

- [12] KOZIC E, HAMMER R, ROSC J, et al. Metallization defect detection in 3D integrated components using scanning acoustic microscopy and acoustic simulations[J]. Microelectron. Reliab, 2018, 88-90: 262-266.

- [13] JEON M, YOO S, KIM S W. A contactless PCBA defectdetection method: Convolutional neural networks with thermographic images [J]. IEEE Transactions on Components, Packaging and Manufacturing Technology, 2022, 12(3): 489-501.

- [14] ZHANG Q, ZHANG M, GAMANAYAKE C, et al. Deep learning based solder joint defect detection on industrial printed circuit board X-ray images [J]. Complex & Intelligent Systems, 2022, 8 (2): 1525-1537.

- [15] NIE L, HUANG Y, LIU M. Internal defects inspection of TSV 3D package based on thermal distribution analysis[J]. AIP Advances, 2021, 11(8).

- [16] 姜也, 黄一凡, 熊美明, 等. PCBA 板载 DDR 芯片焊点缺陷检测研究[J]. 仪器仪表学报, 2023, 44(2): 129-137.

- [17] 张路. 基于 RCP 封装的芯片模型电热模拟[J]. 电子测量技术, 2015, 38(3): 92-95.

- [18] YU Y, SI X, HU C, et al. A review of recurrent neural networks: LSTM cells and network architectures[J]. Neural computation, 2019, 31(7): 1235-1270.

- [19] LALAPURA V S, AMUDHA J, SATHEESH H S. Recurrent neural networks for edge intelligence: a survey[J]. ACM Computing Surveys(CSUR), 2021, 54(4): 1-38.

- [20] GUAN S Y, ZHANG W Y, JIANG Y F. A surface defect detection method of the magnesium alloy sheet based on deformable convolution neural network[J]. Metalurgija, 2020, 59(3): 325-328.

- [21] 李晟, 邓江云, 周兴龙, 等. 基于 LSTM 的电子系统间歇故障严重程度识别方法[J]. 电子测量与仪器学报, 2022, 36(3): 139-148.

- [22] WOLZ B C, JAREMENKO C, VOLLNHALS F, et al. X-ray microscopy and automatic detection of defects in through silicon vias in three-dimensional integrated circuits[J]. Engineering Reports, 2022, 4(9).

### 作者简介

聂磊(通信作者),博士,教授,主要研究方向为电子制造工艺可靠性。

E-mail: leinie@hbut.edu.cn

于晨睿,硕士研究生,主要研究方向为三维封装可靠性。

E-mail: 102210062@hbut.edu.cn

张鸣,硕士研究生,主要研究方向为三维封装可靠性。

E-mail: 2219641163@qq.com

骆仁星,工程师,主要研究方向为特种装备制造。

E-mail: 510607908@qq.com