# 基于 FPGA 和 STM32 的多通道超声信号同步采集系统设计

陈源林<sup>1</sup> 孙尚民<sup>2</sup> 许西宁<sup>3</sup>

(1. 北京交通大学机械与电子控制工程学院 北京 100044; 2. 同方威视技术股份有限公司 北京 100084;

3. 北京交通大学机械与电子控制工程学院 北京 100044)

**摘要:** 使用超声阵列探头进行无损检测时,为了保证检测的精度和准确性,检测系统需要对阵列探头各个通道的超声信号进行同步采集。该多通道超声信号同步采集系统以 FPGA 与 STM32 微处理器为核心,FPGA 芯片负责数据的同步采集和缓存,最多可以进行 32 通道超声信号的同步采集,STM32 作为系统主控芯片,负责发送控制信号和数据传输。该系统结合了 FPGA 和 STM32 微处理器的功能特点,使系统具有良好的工作性能,对各通道 A/D 进行并行控制,完成超声信号的同步采集,并将缓存的数据经由以太网接口传输到上位机进行保存、显示以及后续的数据处理。使用该系统对阵列探头的各个通道进行数据采集,采集的数据有很好的同步性,能够满足多通道超声检测数据同步采集的要求。

**关键词:** 超声检测; 多通道; 同步采集; FPGA; STM32 微处理器

中图分类号: TN806 文献标识码: A 国家标准学科分类代码: 510.40

## Design of multi-channel ultrasonic signal synchronous acquisition system based on FPGA and STM32

Chen Yuanlin<sup>1</sup> Sun Shangmin<sup>2</sup> Xu Xining<sup>3</sup>

(1. School of Mechanical, Electronic and Control Engineering, Beijing Jiaotong Universit, Beijing 100044, China;

2. Nuctech Company Limited, Beijing 100084, China;

3. School of Mechanical, Electronic and Control Engineering, Beijing Jiaotong Universit, Beijing 100044, China)

**Abstract:** When using ultrasonic array probes for nondestructive testing, in order to ensure the accuracy and accuracy of the detection, the detection system needs simultaneous acquisition of ultrasonic signals from each channel of the array probe. The multi-channel ultrasonic signal synchronous acquisition system is based on FPGA and STM32 microprocessor, FPGA chip is responsible for simultaneous data acquisition and cache, as the master chip of the system, STM32 is responsible for transmitting control signals and data transmission. the system could collect 32 channels of ultrasonic signals synchronously at most. The system combines the advantages of FPGA and STM32 microprocessors, it has good working performance, parallel control of each A/D channel, synchronous acquisition of ultrasonic signals, through the Ethernet interface, the data is transmitted to the host computer for storage, display and subsequent data processing. The system is used for data acquisition of each channel of the array probe, the data has good synchronization, and can meet the requirements of synchronous acquisition of ultrasonic testing data.

**Keywords:** ultrasonic testing; multi-channel; synchronous acquisition; FPGA; STM32 microprocessor

## 0 引言

超声检测作为无损检测的重要手段之一,因其检测准确度高、方便快速等优点,已经被应用于许多行业<sup>[1]</sup>。进行超声检测时,为了提高检测精度与准确性,有时需要阵列探

头进行多路同步检测,对多路超声导波信号进行同步采集是超声检测一个重要的环节,数据采集速度和同步性直接影响超声检测的精度和准确性。目前常用的数据采集系统,一般使用单片机或 DSP 来控制 ADC、存储器以及其他外围电路完成数据采集工作,传统的数据采集系统受到

处理器指令周期和处理速度等因素的影响,满足不了多通道数据同步采集的要求<sup>[2-3]</sup>。本系统采用FPGA和STM32为中心硬件构架,FPGA编程灵活性高,在其内部有丰富的触发器和I/O管脚,有较强的并行处理能力;STM32系列单片机是一种带有精简指令集的CPU,其运算速度快,性能优越,功耗低。将FPGA与STM32微处理器相结合使用,可以实现功能互补,大大降低硬件电路的复杂性,提高系统可靠性<sup>[4]</sup>。本系统可以实现多通道超声数据的同步采集,能够提高阵列超声检测数据采集的精度和准确性,对促

进阵列超声检测的发展起到积极地作用。

## 1 系统整体结构设计

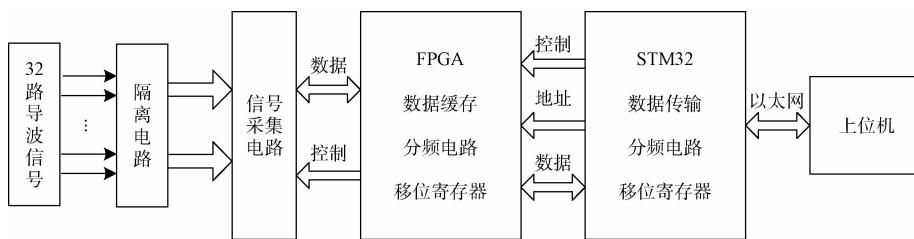

为了满足对超声信号进行同步采集的要求,使用STM32和FPGA作为主CPU设计超声信号同步采集系统。超声信号同步采集系统主要由STM32芯片、FPGA芯片、隔离电路、信号采集电路、数据传输模块、上位机等部分构成,系统结构如图1所示。

图1 超声信号同步采集系统整体结构

多路超声信号通过BNC接口进入系统,通过隔离电路实现对现场信号的隔离;每路信号分别进行放大、滤波等信号调理,提高了系统对信号幅值大小的自适应性;放大后的数据进入A/D芯片进行模数转换;每个通道设计两个A/D芯片,交替控制使能信号,可以提高通道的采样率;多通道信号采集数据量大,数据经由FPGA进入SDRAM缓存,并联使用2片SDRAM,方便多通道数据快速同时存入;缓存的数据经由I/O传接口输至STM32,STM32通过控制以太网接口将数据传送到上位机,对数据进行显示、保存<sup>[5-6]</sup>。

## 2 系统硬件设计

### 2.1 STM32与FPGA接口电路

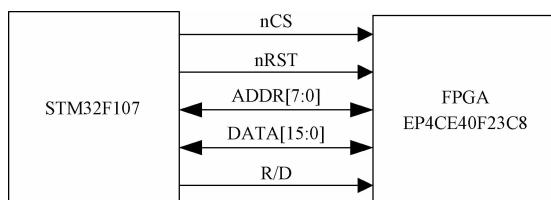

STM32与FPGA有多种数据传输方式,能够并行传输,也可以串行传输,有串行通信总线和外部总线等接口。本系统要进行多路超声信号的同步采集和传输,数据量较大,需要较快的传输速度,选用通过I/O口进行并行传输模式,且容易实现,FPGA与STM32连接方式如图2所示。

图2 STM32与FPGA连接

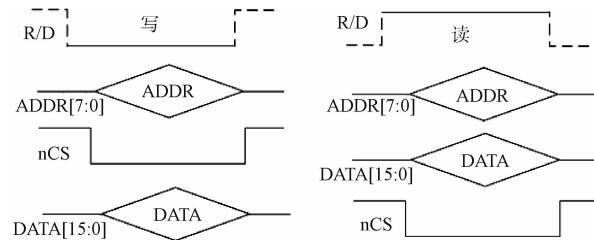

nCS是片选控制信号,低电平时选通;R/D是读写信号,高电平时进行读操作,低电平时执行写操作;通过地址

线ADDR[7:0]、数据线DATA[15:0]完成地址和数据传输。此时FPGA相对于STM32为外部存储,STM32通过编写RAM读写程序能够完成对FPGA的访问<sup>[7-8]</sup>。

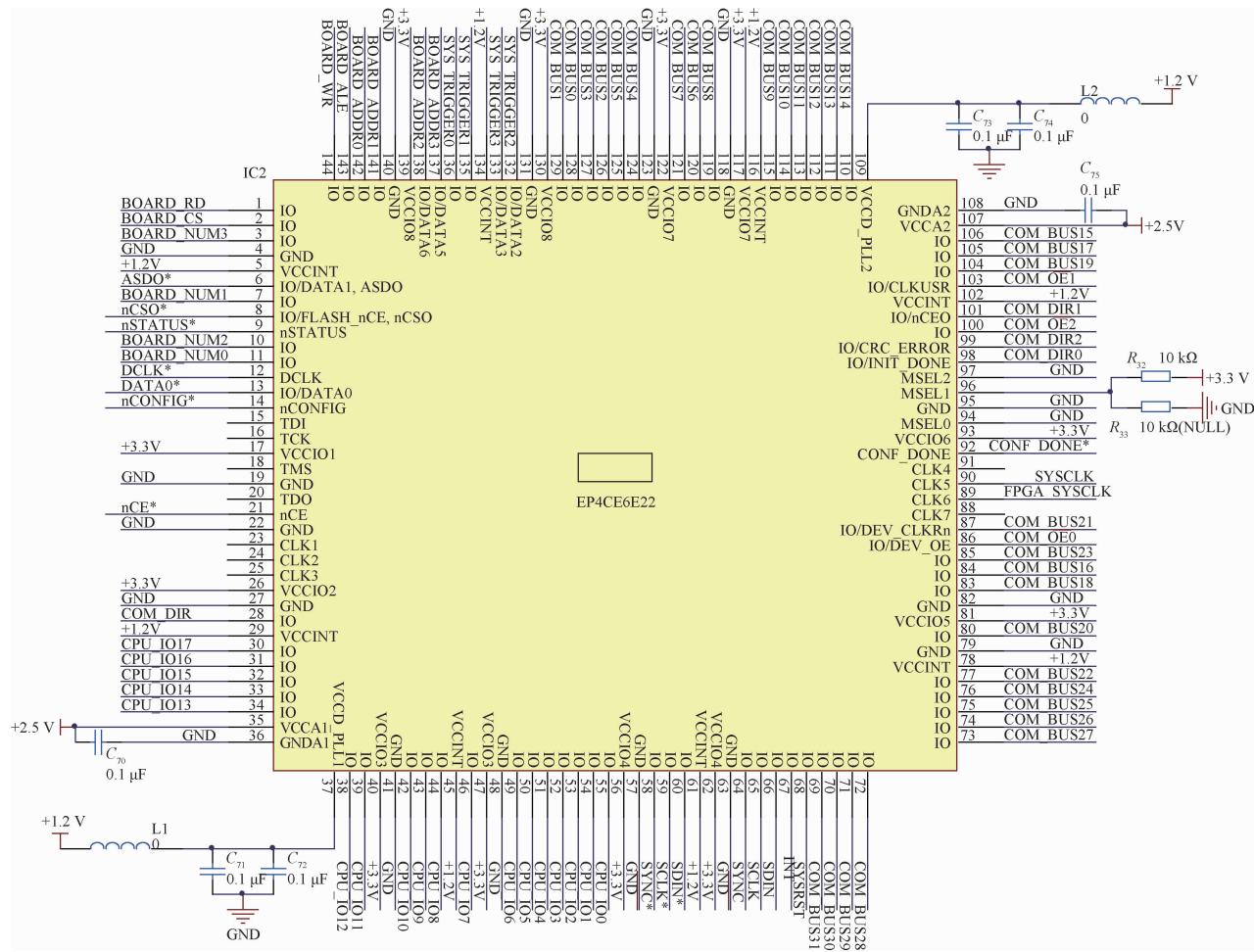

### 2.2 FPGA外围电路设计

FPGA即现场可编程门阵列,属于专用集成电路范畴内一种半定制电路,FPGA有丰富的内部资源和I/O引脚,具有设计周期短,编程灵活的特点,能够解决定制电路的不足和原有可编程器件门电路数有限的问题,非常适用于多路数据的并行采集。FPGA芯片主要由基本可编程逻辑单元、可编程输入输出单元、嵌入式RAM单元、完整的时钟管理模块、内嵌底层功能单元、内嵌专用硬核和丰富的布线资源7个部分组成<sup>[9]</sup>。

系统设计最多能够进行32通道超声信号同步采集,为了满足超声信号采集的实时性和同步性要求,需要选择时钟频率较高、内部延时小的FPGA芯片,因此选择了Cyclone系列的EP4CE40F23C8芯片,该芯片包含39 600个逻辑单元,116个9 KB的RAM块,4个时钟管理网络和20个全局时钟网络,可以支持多达328个用户I/O。该芯片丰富的片上资源配置灵活的编程方式能够满足系统的使用需求,FPGA的输入输出接口主要有以下几个:与DA相连的12位数据输出,为DA提供时钟的2个PLL输出,触发信号的输出,与配置器件及JTAG接口的连接<sup>[10]</sup>,系统使用的FPGA芯片外围电路如图3所示。

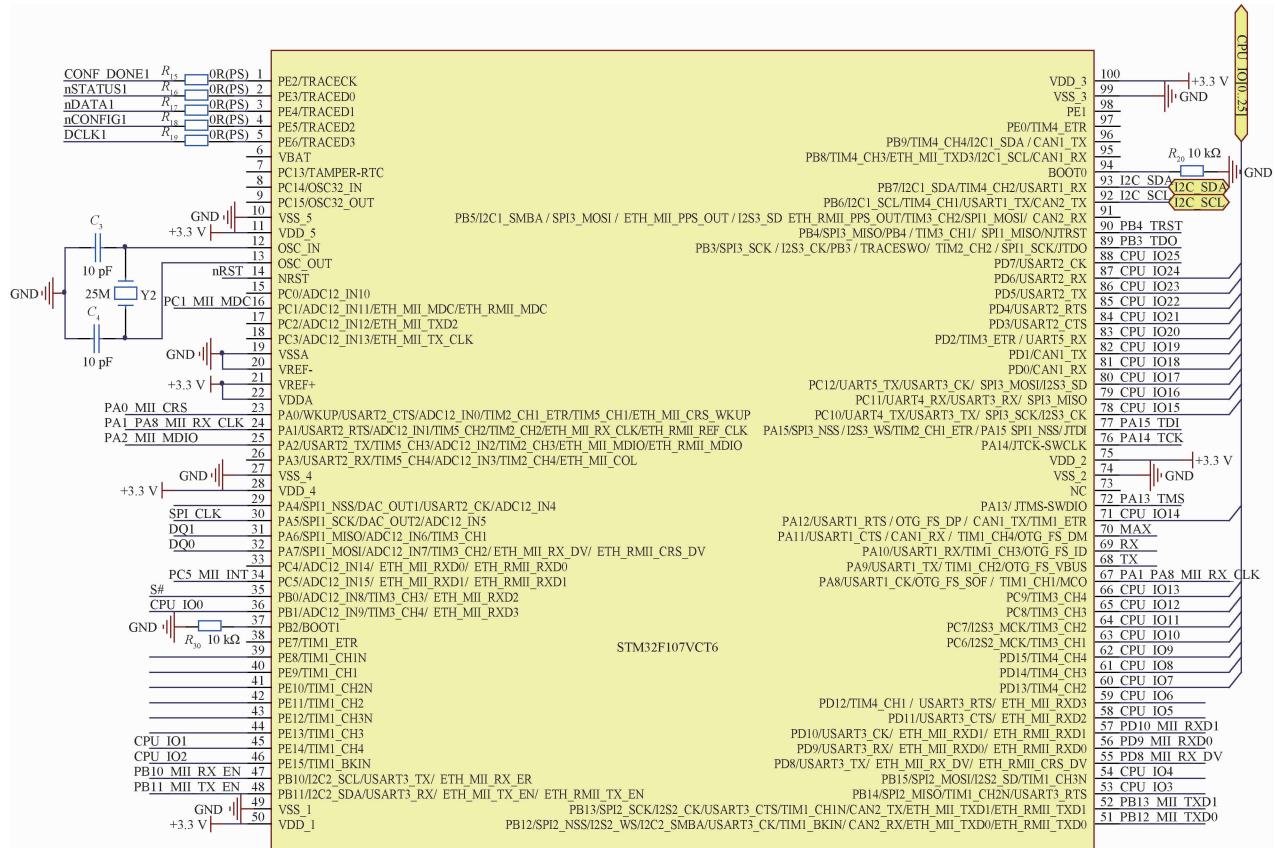

### 2.3 STM32F107外围电路设计

STM32F107作为系统的中央处理单元,通过以太网接口将数据传输上位机进行保存和显示。STM32F107是新型互连型微处理器,此系列的微处理器工作效率高,功耗低,能够满足系统通过以太网进行数据传输的要求,能够提高联网设备同步通信的能力,在其内部集成了32位

图 3 FPGA 外围电路

的高性能 ARM Cortex-M3 CPU,10 个定时器、两个 12 位模数转换器、两个 12 位数模转换器,具有多种工业标准接口,包括 2 个 I<sup>2</sup>C 接口、5 个 USART 接口和 3 个 SPI 端口等,选用此处理器可以满足本系统的使用要求,STM32F107 外围电路设计如图 4 所示<sup>[11]</sup>。

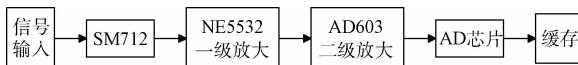

## 2.4 信号调理与模数转换电路

为了使输入信号达到进入 A/D 的要求,信号在进入 A/D 芯片之前需要进行整形、滤波、放大等操作,根据超声信号的特点,系统设计的信号调理电路如图 5 所示,原始信号为差分信号,各通道信号通过 BNC 接头进入采集系统,信号经过 1:1 变压器后转换成单端信号,使用 SM712 瞬态抑制二极管阵列对电路进行保护,能够有效防止电压及电流对系统的瞬态干扰,超声信号强度受很多因素影响,变化范围很广,使用放大器 NE5532 与 AD603 串联,对信号进行两级放大,二级运放可以提高系统对信号强弱的适应性,NE5532 是高性能、低噪声放大器,与 AD603 可调增益放大器级间耦合方式为电容耦合,经过一级放大后的信号幅值可能超过所选用 A/D 芯片的量程,因此必须使用二级运放来调整信号的幅值,使调理后的信号幅值处于

A/D 转换芯片的量程范围内。

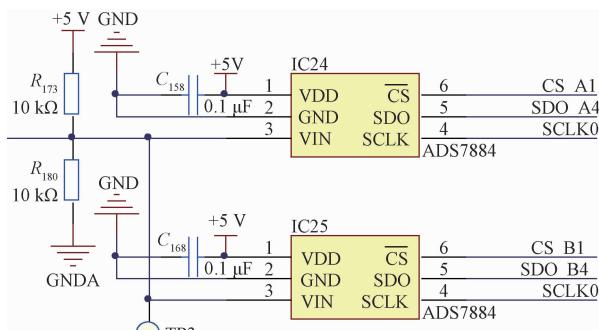

A/D 芯片连接信号调理电路与 FPGA,功能是将模拟信号转化为数字信号,再将数字信号传输给 FPGA 进行数据缓存和传输等操作。根据采样定理,采样频率至少为采样信号频率的 2 倍,在波形信号的实际采集中,采样频率至少要达到 5 倍才可以将波形信号相对完整采集出来。A/D 转换芯片作为整个数据采集系统的关键部件,它的性能决定了系统信号采集的精度,但采样频率越高,对应的数据量越大,会导致数据快速存储困难、影响波形传输完整性,根据上述条件,选用 ADS7884 作为系统 A/D 转换芯片<sup>[12]</sup>。

ADS7884 是一款逐次逼近型模数转换器,芯片尺寸小,电路设计时占用空间少,图 6 所示为其外围电路设计。此芯片拥有 10 位分辨率,采样频率为 3、48 MHz 串行输出。为了提高系统的稳定性和采样率,在模数转换电路设计时采用了冗余设计原则,每个数据采集通道放置 2 片 A/D 转换芯片,两片 A/D 芯片串行时钟 SCLK 共用 FPGA 上同一个 I/O,片选控制、数据接口分别接 FPGA 不同 I/O,交替片选使用。

图4 STM32F107外围电路

图5 信号调理与模数转换电路框图

图6 A/D芯片外围电路

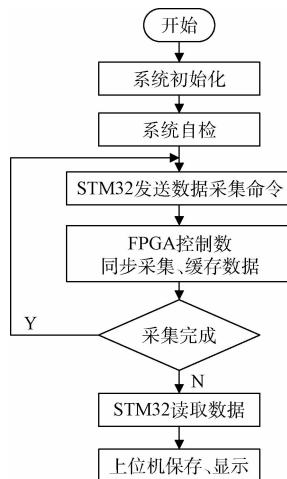

### 3 系统软件设计

系统的硬件设计采用STM32和FPGA相结合的设计方法,因此系统的软件部分使用C语言和Verilog编写,通过C和Verilog分别实现对STM32和FPGA周围芯片的

#### 数据读取控制。

系统上电后,首先进行初始化操作,自检结束后进入主程序,STM32发送数据采集命令,开始进行数据采集,FPGA控制AD芯片的读写,进行多路数据的同步采集,并将采集到的数据缓存进入2片SDRAM中,数据采集完成后,与STM32进行数据传输,STM32控制以太网接口,整个系统工作流程如图7所示<sup>[13]</sup>。

#### 3.2 FPGA整体模块设计

FPGA主要负责32通道数据的读取控制,将数据缓存进入SDRAM,并将数据传输到STM32内部。根据FPGA芯片在系统中的作用,其内部整体设计包括b-sdram模块、adc模块、a-sdram模块、com-module模块、dac模块、sys-ctrl模块6个部分。

adc模块主要进行32路A/D时序的控制,并将数据进行格式整理,分别进入两个SDRAM进行缓存;a-sdram与b-sdram模块分别控制两片SDRAM对数据的读写,并通过com-module的部分模块控制将数据写入STM32中<sup>[14]</sup>。

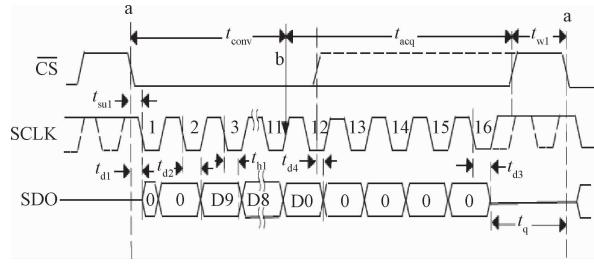

#### 3.3 模数转换信号控制

ADS7884为串行数据输出的模数转换器,具有10位分辨率,单通道采样频率有2.4和3.2MHz两种可以选择,模数转换之后数据的输出控制时钟SCLK为48MHz。

图 7 数据采集系统工作流程

通过相应的时钟和电源,AD 芯片可自行进行转换,数据读出时必须要严格依照时序图,如图 8 所示。

图 8 AD 芯片时序图

串行口 SDO 在片选信号 nCS 与串行时钟 SCLK 的共同作用下进行数据采样。数据在片选信号 nCS 的下降沿时被采样,随着 nCS 的下降沿,输入信号被采样,转换过程初始化,转换的同时数据开始输出<sup>[15]</sup>。

### 3.4 STM32 读写 FPGA 数据

STM32 主要接收来自 FPGA 的数据,并通过以太网接口将数据传送到计算机。STM32 与 FPGA 进行数据传输时,相当于 STM32 读写片外 RAM,数据采集时,多为读取 FPGA 数据的状态<sup>[16]</sup>。STM32 与 FPGA 连接主要有片选线 nCS,读写控制线 R/D,地址线 ADDR[7:0],数据线 DATA[15:0]。在进行写操作时,R/D 为低电平,给出地址,拉低片选,写入数据,拉高片选;进行读操作时,R/D 为高电平,给出地址,读出数据,片选拉低再拉高,操作时序如图 9 所示。

## 4 实验分析

完成多通道超声信号采集系统硬件和软件设计后,对整个系统的工作性能进行验证。在实验室环境下搭建了多通道超声信号采集实验平台。使用函数发生器发出正弦波信号,通过高压放大器对原始信号进行放大后,激励

图 9 FPGA 与 STM32 数据读取时序图

超声发射探头产生超声信号,在波导介质上安装 32 路超声压电换能片进行数据接收,接收压电片经过转接板与数据采同步集板卡连接,实现多通道超声信号同步采集,试验系统如图 10 所示。

图 10 实验系统搭建

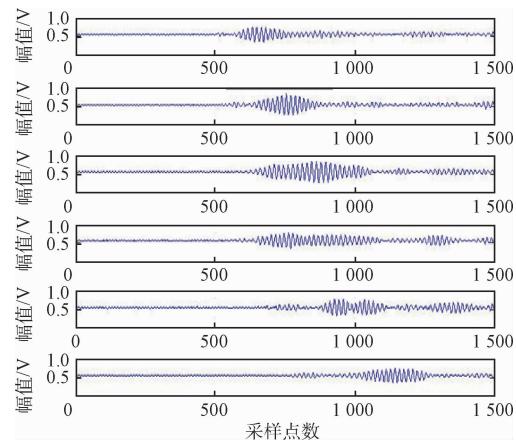

对每一个通道进行数据采集实验,通过采集板卡把接收到的数据传输到上位机进行保存和显示。由于通道数目较多,其中 6 个通道的原始数据波形如图 11 所示。

图 11 系统采集的原始波形

由图 11 可以看出,每个通道均能采集到有效的超声信号,并且由于压电片在波导介质上位置不同,采集的波形信号起振时间符合理论效果。

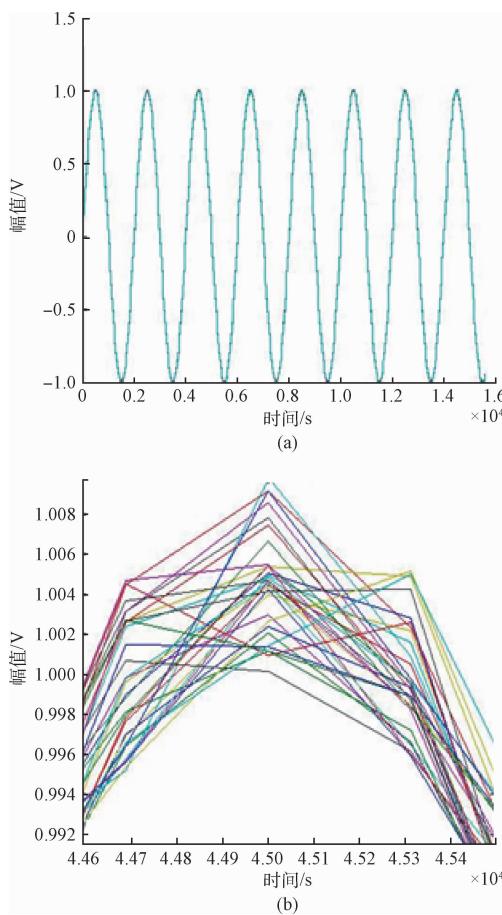

为了验证采集系统各通道数据的同步性,通过函数发

生器产生频率为50 kHz,峰峰值为2 V的正弦信号,连接到32路信号采集端口,采样频率设置为3.2 MHz,对同一位置的压电片进行超声信号同步采集,实验结果如图12所示。

图12 数据同步采集信号及局部放大图

图12(a)为32个通道采集到的数据重叠在一起的波形,图12(b)为信号峰值局部放大图,32个通道的峰值信号集中在同一时刻,各个通道波形没有明显的相位差,波形的同步性良好,达到了多通道超声信号同步采集系统的设计要求。

## 5 结 论

本文主要从硬件和软件两个方面,介绍了多通道超声信号同步采集系统。本系统采用的FPGA和STM32相结合的设计方式,利用STM32强大的内部资源和FPGA灵活方便的逻辑操控性能,对各通道AD进行并行控制,实现了多通道超声信号同步采集,能够满足采集精度高、传输速度快的采集要求。这种设计方法将FPGA和STM32的功能特点进行整合,实现二者功能互补,降低了硬件电路复杂程度并使其体积大大减小,使系统的整体功耗属于较低水平,提高了系统的效率和可靠性。通过实验可以看出,采集到的超声导波信号具有很好的同步性,能够满足多路超声导波信号的同步采集的要求,有很好的实用价值。

## 参考文献

- [1] 敬人可,李建增,周海林.超声无损检测技术的研究进展[J].国外电子测量技术,2012,31(7):28-30.

- [2] 李美花,闫卫平,王颖,等.微传感器阵列多通道数据采集和处理系统[J].电子测量与仪器学报,2016,30(2):311-317.

- [3] 吴宇,黄新迪,吴媚,等.基于DSP的高速数据采集处理系统的研究[J].国外电子测量技术,2016,35(5):62-65.

- [4] 曹彬乾,程远增,杨青.基于STM32+FPGA的数据采集系统的设计[J].计算机工程与设计,2014,35(4):1231-1235.

- [5] 林伟,王毅男.基于FPGA与STM32的低功耗数据采集系统[J].化工自动化及仪表,2016,43(2):210-214.

- [6] 张博,段哲民.基于FPGA的数据采集系统设计[J].电子设计工程,2012,20(7):86-88.

- [7] 张淑梅.基于ARM+FPGA的高精度数据采集系统设计[J].国外电子测量技术,2014(11):62-65.

- [8] 徐虎.基于FPGA与STM32的液晶检测电路设计[J].电子设计工程,2016,24(5):87-88.

- [9] 纪大伟,徐抒岩,胡君,等.基于FPGA的多通道高速数据采集系统[J].仪表技术与传感器,2011(12):69-71.

- [10] 张会新,吴学庆,蒋绍凤,唐亮.基于FPGA的多通道同步数据采集存储系统[J].国外电子元器件,2009,17(7):68-70.

- [11] 张旭,亓学广,李世光,等.基于STM32电力数据采集系统的设计[J].电子测量技术,2010,33(11):90-93.

- [12] 陈珏利,曾成志,郑海荣,等.基于ADS6122和FPGA的多通道信号采集系统的设计[J].电子器件,2012,35(4):406-411.

- [13] 孙士诚,皮佑国,等.基于STM32和FPGA的多路模拟量采集系统的设计[J].自动化与仪器仪表,2015(4):23-26.

- [14] 朱睨,沈祥华.基于FPGA的八通道超声探伤系统设计[J].电子设计工程,2013,21(9):164-166.

- [15] 吴小龙,吴杰.基于FPGA和STM32的空管雷达数据协议转换器设计[J].电子质量,2014(10):16-19.

- [16] 王勇,郝晓红.基于STM32+FPGA的航空继电器时间参数测试系统[J].仪表技术与传感器,2016(8):56-59.

## 作者简介

陈源林,硕士研究生,研究方向为无损检测及检测系统设计。

E-mail: 15121237@bjtu.edu.cn

孙尚民,硕士,现为同方威视技术股份有限公司产品设计制造本部总经理。

E-mail: sunshangmin@nuctech.com