# 基于 FPGA 的多通道大容量 FIFO 设计

徐洋洋

(连云港杰瑞电子公司 连云港 222006)

**摘要：**提出了一种基于 FPGA 的多通道大容量 FIFO 设计方案。在高速数据采集板卡中, 高速大容量 FIFO 决定了数据采集的深度与速度。为了满足高速数据采集板卡 FIFO 速度高、容量大以及体积小的要求, 采用 SDRAM 与 FPGA 联合设计的方案。取 SDRAM 价格低、存储空间大、速度快的特点, 同时利用 FPGA 解决 SDRAM 接口控制逻辑复杂的问题, 将存储空间封装为 FIFO 接口。完成了 SDRAM 状态控制器、FIFO 地址管理器以及 FIFO 逻辑接口的设计与实现。在 Modelsim 平台上完成了基于 Micron Technolog 公司 SDRAM 模型的数据读写仿真。最后, 在一块 PXI 板卡上完成了实物测试, 分析了时钟频率、延时参数以及读写速率对误码率的影响, 并给出调整方案。实现了 8 路 16 M 存储深度 16 bits 位宽异步双口 FIFO, 读写速度可达 128 Mbps, 为高速数据采集系统提供可靠的数据存储平台。

**关键词：**SDRAM; FPGA; FIFO; PXI; 高速采集系统

中图分类号：TN79<sup>+1</sup> 文献标识码：A 国家标准学科分类代码：510.4030

## Design of multi-channel FIFO with mass storage facility based on FPGA

Xu Yangyang

(Lianyungang JARI Electronics Co., Ltd Institute, Lianyungang 222006, China)

**Abstract:** proposed a method of Multi-channel FIFO with mass storage facility based on FPGA. In the high-speed sample board, the speed and capability of the system depend on the FIFO. In order to fulfil high-speed sample board requirements high-speed, huge facility and little volume, selected SDRAM and FPGA to accomplish. The SDRAM has high-speed, huge capability and low-cost but complex. Taking the advantage of FPGA to make up the complexity of SDRAM, use the FPGA to make the logic of the FIFO, accomplished the SDRAM state controller FIFO address management and FIFO Interface logic. Then accomplished simulation on the Modelsim with a SDRAM model designed by Micron Technolog. At last, applying this method on a PXI board. Analysed the influence of clock frequency, delay parameter and read-write Frequency to Bit Error, then gave the rectify solution. Realized eight channel FIFO with 16 M storage deep, asynchronous dual-port, 16 bits wide and a speed of 128 Mbps. Providing a reliable data storage platform for the high speed data acquisition system.

**Keywords:** SDRAM; FPGA; FIFO; PXI; high-speed sample system

## 0 引言

高速数据采集系统广泛的应用于雷达、虚拟仪器、示波器、图像处理设备中<sup>[1]</sup>。高速数据采集系统一般有采集系统、存储系统、数据处理系统<sup>[2]</sup>。其中采集系统完成短时间的高速数据采集; 存储系统完成与采集系统相匹配的高速存储, 以及与数据处理系统相匹配的低速输出; 数据处理系统完成后续的数据处理<sup>[3]</sup>。采集系统数据采集特点为时间短、速度高。目前 NI 最新的高速数据采集卡是 PXI-5154 数字化仪/示波器, 具有双通道最大同步实时采样率

2 GSa/s<sup>[4]</sup>。另外一般数据采集系统与数据处理系统属于两个时钟域。因此数据存储系统需要同时具备高速输入接口以及低速输出接口, 同时要满足不同时钟域的设计。

当前高速的数据存储方案有 Flash、高速 FIFO、IDE 硬盘以及 SDRAM 等<sup>[5]</sup>。其中 Flash 存储空间大, 可以长久保存。例如三星公司的 K9K8G08U0M 具有 8 G 的存储空间, 接口速度可以达到 40 MHz<sup>[6]</sup>, 其缺点为每次数据写入前需要执行擦除操作。擦除的周期为 20 ms, 因此总写入时间会较长。高速 FIFO 特点是写入速度快、双口异步 FIFO 内部集成了异步处理机制, 能够很好的完成跨时钟

域高速数据处理。其缺点是价格昂贵、同时存储空间小于 100 M, 不适合高速数据采集系统使用。IDE 硬盘具有非常丰富的存储资源, 很高的存储速度, 但体积巨大无法满足板卡的体积要求。

SDRAM 体积小、存储空间大, 缺点是控制逻辑复杂。针对高速采集系统多采用 FPGA 做采集逻辑控制, 利用 FPGA 强大的逻辑处理功能, 在不增加硬件成本和板卡空间的情况下可以很好地解决 SDRAM 控制逻辑复杂的缺点。

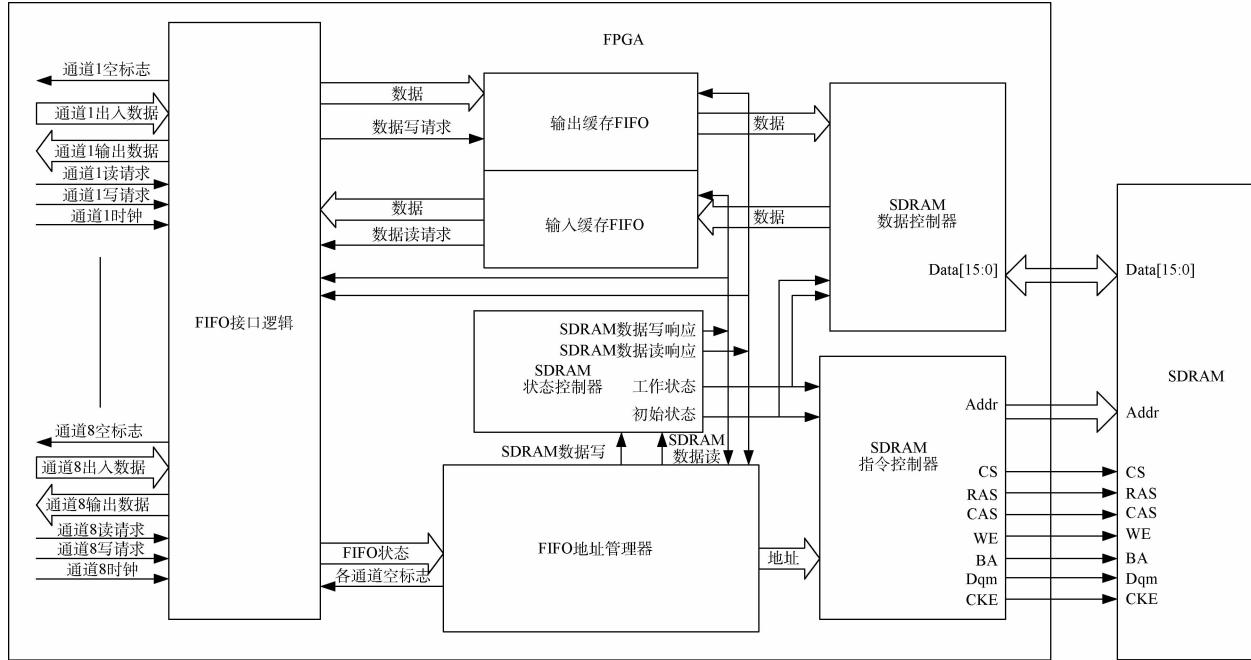

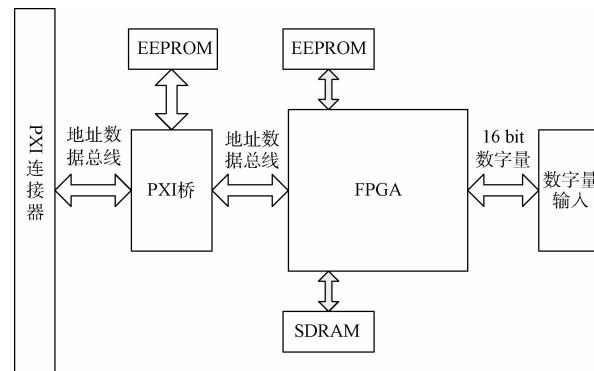

图 1 整体结构

### 1.1 SDRAM 状态控制器设计

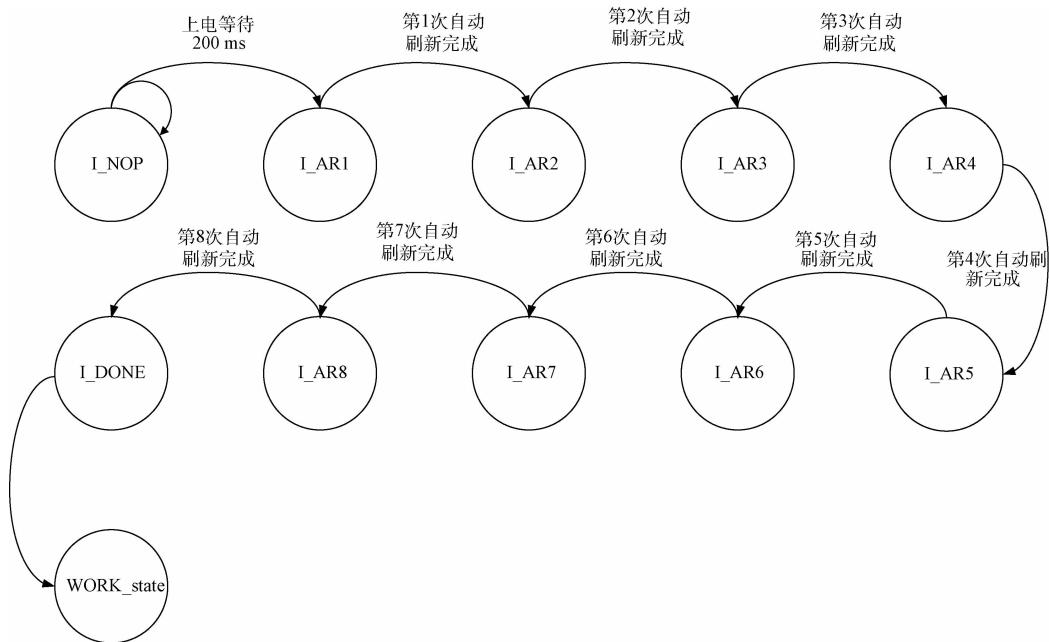

SDRAM 中文全称为同步动态随机存储器, 是一种大容量高速数据存取器件。为了达到高速、高集成度, SDRAM 内置逻辑控制单元, 用来解读外围指令完成数据存取功能。同时完成定时刷新工作, 例如 micron 公司的 MT48LC16M16A2 在每间隔 64 ms 就需要刷新一次, 刷新时间为 7.813  $\mu$ s<sup>[7]</sup>; 为了节约引脚, 其行地址与列地址共用总线。这些状态的转换控制都需要按照既定的状态进行<sup>[8]</sup>。因此设计了 SDRAM 状态控制器完成 SDRAM 状态控制。SDRAM 上电后应当首先进行自刷新之后进入工作状态。因此设计了两个状态机分别为自刷新状态机、工作状态机。

自刷新状态需要完成上电等待 200 ms 以及 8 次自刷新, 之后 SDRAM 就会进入工作状态, 自刷新状态机如图 2 所示。

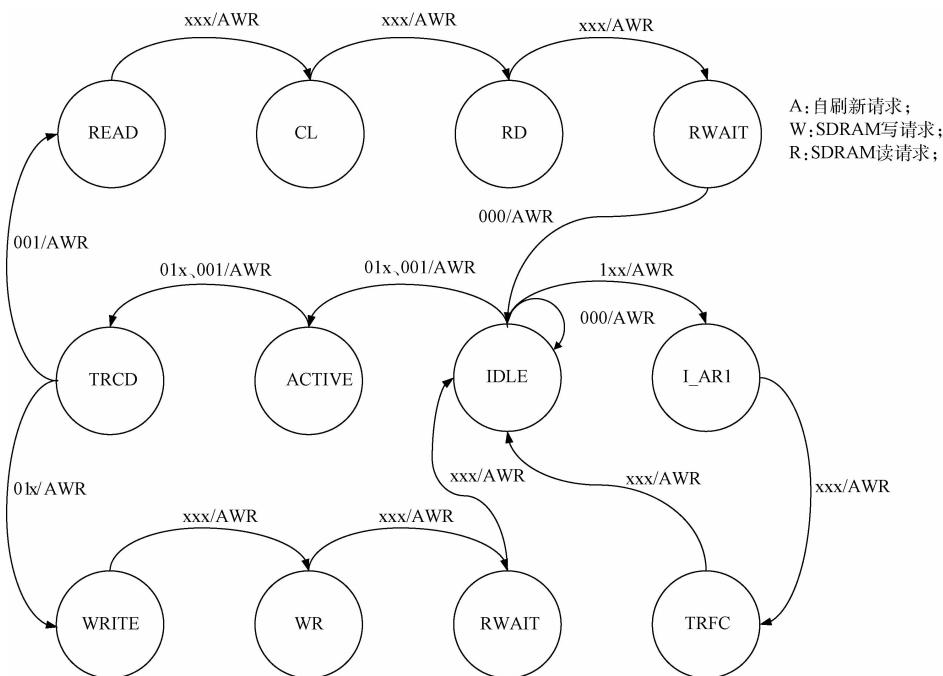

自刷新完成后 SDRAM 进入工作状态。工作状态包括空闲状态、读状态、写状态以及刷新状态几种。其中读状态包含的状态有行有效、行等待、读初始、读潜伏、读数据和读等待。写状态包含的状态有行有效、行等待、写初

### 1 架构设计

SDRAM 与 FPGA 联合设计的重点为 SDRAM 控制器以及 FIFO 接口电路。整体结构框图, 如图 1 所示。主要模块包括 FIFO 接口逻辑、输入输出缓存 FIFO、SDRAM 状态控制器、FIFO 地址管理器、SDRAM 数据控制器和 SDRAM 指令控制器。其中输入输出缓存 FIFO 主要完成数据的缓存; SDRAM 数据控制器与 SDRAM 指令控制器借鉴 Altra 官网设计。其他模块设计原理如图 1 所示。

始、写数据和写等待。刷新状态包含的状态有初始状态、刷新等待状态。综上, 所有工作状态包括, 初始状态 (IDLE)、行有效 (ACTIVE)、行等待 (TRCD)、读初始 (READ)、读潜伏 (CL)、读数据 (RD)、读等待 (RWAIT)、写初始 (WRITE)、写数据 (WR)、写等待 (RWAIT)、自刷新 (AR)、自刷新等待 (TRFC)。设计 SDRAM 状态机如图 3 所示。对于读写冲突的状态, 设定为写优先。当读请求、写请求同时发生时, 输入 AWR 为 011, 此时状态机在行等待 (TRCD) 会跳转到写初始 (WRITE), 从而优先处理写操作。状态的转移除了图中标示的 ARW 3 个输入信号以外还有计时器信号, 当计时器信号满足设计要求时, 状态自动进行转移。

### 1.2 FIFO 地址管理器设计

FIFO 地址管理根据 SDRAM 状态控制器的读写响应信号以及 FIFO 接口逻辑模块的状态以及读写信号完成 8 个通道的地址管理。内部将 SDRAM 分为 8 个相互独立的地址块, 每个地址块具有独立的写入地址寄存器、读出地址寄存器。根据 FIFO 状态判断当读写的通道数, 同时

图 2 自刷新状态机

图 3 工作状态状态机

更改响应的地址。并对 SDRAM 控制器发出读写指令。其中写入寄存器数值计算公式如下：

$$WR\_addr \equiv WR\_addr + 1 \quad (1)$$

其中  $WR\_addr$  为写入地址寄存器数据, 数据格式为无符号数;  $i$  表示通道标志, 为  $1, 2, 3, \dots, 8$ ;  $RD\_addr$  为读出地址寄存器。

读出寄存器数值计算公式如下：

*RD addr* =

$$\begin{cases} \text{WR\_addr}_i + 1 & (\text{WR\_addr}_i = \text{RD\_addr}_i) \\ \text{RD\_addr}_i + 1 & (\text{WR\_addr}_i > \text{RD\_addr}_i) \end{cases} \quad (2)$$

每当写入数据时更改写入地址寄存器, 进行式(1)、(2)的计算。考虑到数据溢出问题, 当数据写入写满整个存储空间时, 地址寄存器会由最大值变为零, 因此存在写入地址寄存器小于或者等于读出地址寄存器的情况。当写入寄存器等于读出寄存器时, 表示当前 FIFO 已经溢出, 此时应当将  $RD\_addr$  数据加一。这样就保证了 FIFO 可

以无限存储,且存储数据为最新。

### 1.3 FIFO 接口逻辑

FIFO 接口逻辑使用状态机控制,每个 FIFO 通道的读、写分别占用一个状态,空闲状态占用一个状态,共 17 个状态。只有当前状态为空闲状态时每个通道可以占用 SDRAM 读写权。为了防止数据溢出造成数据丢失,同时充分利用 SDRAM 突发读写页的特点,每个通道设置了一个一页大小和缓存 FIFO。

为防止数据阻塞,需要对 8 个通道同时写入数据的最坏情况进行数据流量分析。有如下公式:

$$T \cdot f_{wmax} \cdot 8 = \frac{(T - t_{ar} - t_{rfc}) \cdot f_{sdr\_clk}}{t_{active} + t_{rd} + t_{write} + t_{wr} + t_{wait} + t_{idle}} \cdot 512 \quad (3)$$

以 MT48LC16M16A2 为例,以上参数除最高写入频率  $f_{wmax}$  为计算值外其他均为芯片参数或设计参数。其中  $T$  为 SDRAM 刷新周期 64 ms;  $t_{ar}$  为自刷新需要周期,此处为 10 ns;  $t_{rfc}$  为自刷新等待周期,此处为 7.821  $\mu$ s;  $f_{sdr\_clk}$  为 SDRAM 设计频率,此处为 100 MHz,  $t_{active}$  为行有效周期,此处为 1;  $t_{rd}$  为行等待周期,此处为 1;  $t_{write}$  为突发写周期,此处为 512;  $t_{wait}$  为写入等待周期,此处为 3;  $t_{idle}$  为初始状态周期,此处为 1;由此计算得到  $f_{wmax} = 12.35$  MHz。同理

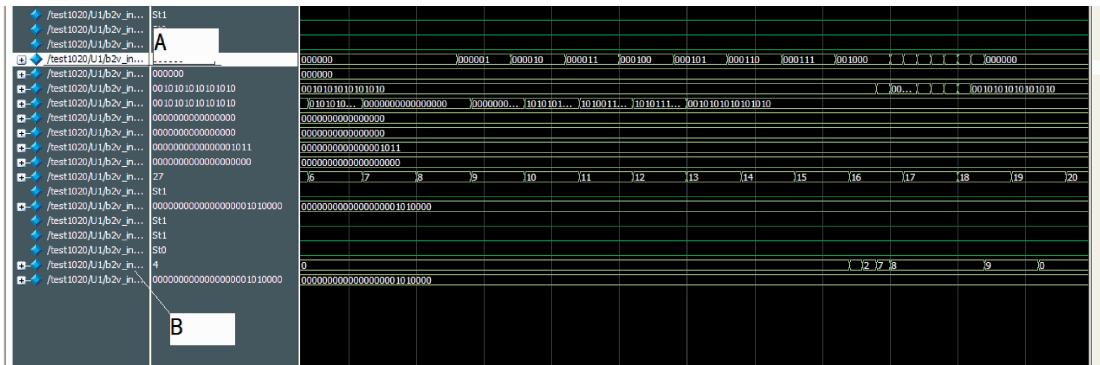

图 4 SDRAM 读写仿真波形

### 3 实物验证

实际使用中,由于 PCB 布线延时的影响,SDRAM 的读写情况会与仿真有所不同。主要是由 PCB 布线导致数据线、时钟线有一定的延时造成,因此实际应用中需要重新调试一套适合 PCB 的设计参数。这里完成了一块基于 PXI 的测试板。其框架如图 5 所示。

测试中由外部提供 16 bit 数字量,从 0×0000 到 0×ffff 依次写入到 SDRAM 中,然后再通过 FPGA 将写入的数据读出并通过 PXI 桥路芯片发送给上位机。通过上位机软件对数据进行分析,并记录每 65 536 个数字中误码的个数。分别调整数据 SDRAM 主时钟延时参数  $clk\_dl$ 、数据读写频率  $f_{fifo}$ 、SDRAM 主时钟频率  $f_{sdr\_clk}$  得到表 1。分析表 1 发现,调整 SDRAM 主时钟延时参数、改变 SDRAM

对于读速率有如下公式:

$$T \cdot f_{rmax} \cdot 8 = \frac{(T - t_{ar} - t_{rfc}) \cdot f_{sdr\_clk}}{t_{active} + t_{rd} + t_d + t_{read} + t_{rd} + t_{wait} + t_{idle}} \cdot 512 \quad (4)$$

其中  $t_d$  为读潜伏周期,此处为 3;  $t_{read}$  为突发读周期,此处为 512;  $t_{wait}$  为写入等待周期,此处为 3;由此计算得到:  $f_{wmax} = 10.31$  MHz。

考虑到时钟偏斜,以及数据处理余量此处设计 FIFO 输入输出频率  $f_{fifo}$  为 8 MHz。

### 2 仿真测试

仿真环境为 Modelsim se 6.5g。仿真器件为库文件为 Altera 公司的 altera\_mf、220model、cyc3\_atoms 等<sup>[9]</sup>。工程设计使用 cycloneiii 系列芯片。SDRAM 模型使用 Micron Technolog 公司 SDRAM BUS Fuctional 模型<sup>[10]</sup>版本为 V2.2. 写入并读出突发长度为 8,写入时钟为 8 MHz 时得到如图 4 所示波形。图中 A 为 SDRAM 数据引脚,B 为 SDRAM 状态控制器的状态变量。通过仿真可以看到设计达到了预定要求。同时在此处还进行了写入与读出频率为 10 MHz 的压力测试,数据并无溢出错误现象,说明在仿真环境下系统设计完全能够达到设计预期。

图 5 PXI 测试版框图

主时钟频率会改变数据的采样以及保持时间,进而调整数据正确率。

表 1 参数分析

| $clk\_dl/ns$ | $f_{fif_0} / MHz$ | $f_{sdr\_dk} / MHz$ | 误码    |

|--------------|-------------------|---------------------|-------|

| 0            | 8                 | 100                 | 2 865 |

| 3            | 8                 | 100                 | 364   |

| 3            | 8                 | 80                  | 0     |

| 3            | 8                 | 70                  | 7 211 |

同时也可以看到如果 SDRAM 时钟频率过低则会导致数据溢出使误码大幅增加。因此在工程中应当严格的约束 SDRAM 时钟、数据以及控制引脚的长度,增加设计可靠性。

## 4 结 论

本文设计了一种基于 FPGA 的多通道大容量 FIFO。给出了 SDRAM 控制器的状态分析,同时给出了多通道 FIFO 的地址分配方法以及地址防溢出算法。实现了 8 路互不耦合的高速大容量 FIFO。在高速数据采集板卡领域具有十分广泛的应用前景。

## 参考文献

- [1] 张磊,贺强民,包斌.一种用于筛选高可靠性 FPGA 的硬件测试电路[J].电子测量技术,2015,38(2):68-73.

- [2] 胡亚平. FPGA 与 CPU 高速接口的实现[J].国外电子测量技术,2013,32(4):66-68.

- [3] 汪铁华.浅谈电子测量技术和仪器的重要性[J].国

(上接第 192 页)

## 参考文献

- [1] 赵锐,钟榜,朱祖礼,等.室内定位技术及应用综述[J].电子科技,2014,27(3):154-157.

- [2] DONG R, QUAN R, HOU F, et al. New research trends on high-precision time transfer technology[J]. Instrumentation, 2015(4).

- [3] LIN C. Application of SDS-TWR technology in coal mine personnel positioning system[J]. Industry & Mine Automation, 2015.

- [4] 李奇越,吴忠,黎洁,等.基于改进卡尔曼滤波的 NLOS 误差消除算法[J].电子测量与仪器学报,2015,29(10):1513-1519.

- [5] 贺晶晶,姜平,冯晓荣.基于 UWB 的无人运输车的导航定位算法研究[J].电子测量与仪器学报,2016,30(11):1743-1749.

- [6] 王沁,何杰,张前雄,等.测距误差分级的室内 TOA 定位算法[J].仪器仪表学报,2011,32(12):2851-2856.

- [7] 郑学理,付敬奇.基于 PDR 和 RSSI 的室内定位算法研究[J].仪器仪表学报,2015,36(5):1177-1185.

外电子测量技术,2009,28(1):12-13.

- [4] 徐洋洋,高文政,徐大林.基于 DSP 的旋转变压器解算系统设计[J].电子测量技术,2015,38(1):54-58.

- [5] 李冰洋,贾银亮,张峰,等.基于 FPGA 的机载综合显示系统的设计与实现[J].电子测量技术,2016,39(2):76-79.

- [6] 陈瑞斌,唐惠玲,徐虎,等.基于 FPGA 的页快速命中 SDRAM 控制器的设计[J].现代电子技术,2015(13):63-66.

- [7] 王飞.基于 FPGA 的全数字化峰值时刻检测技术[J].电子测量与仪器学报,2015(6):914-919.

- [8] 汪伟,徐科军,方敏,等.一种气体超声波流量计信号处理方法研究[J].电子测量与仪器学报,2015,29(9):1365-1373.

- [9] 邓翔宇.修正非线性误差的宽量程多电桥电阻测量电路设计[J].电子测量与仪器学报,2016(9):1418-1424.

- [10] 美国国家仪器.运用示波器和使用者可设定的 FPGA 提高测量质量与速度[J].国外电子测量技术,2015,34(6):1-4.

## 作者简介

徐洋洋,1989 年出生,工学硕士,工程师,主要研究方向为数据处理、轴角解算算法研究等。

E-mail:sanshuiyu@csu.edu.cn

- [8] 胡泮,杨鹏,史旺旺,等.基于 WSN 的低功耗水稻土壤水分监测系统[J].农机化研究,2015(1):100-104.

- [9] 阳熊.基于超宽带的定位技术研究与应用[D].成都:电子科技大学,2015.

- [10] 梁旭,刘才慧.基于混合粒子群算法的在线检测路径规划[J].国外电子测量技术,2015,34(12):30-34.

- [11] 陈漠.用于最优化问题的改进粒子群优化算法研究[D].长春:吉林大学,2015.

## 作者简介

赵强,工学硕士,主要从事无线传感器网络的研究。

E-mail:zhaoqiangnuaa@yeah.net

王敬东,副教授,主要从事无线传感器网络、图像处理技术研究。

E-mail:wjd1291@nuaa.edu.cn

刘云霄,工学硕士,主要从事无线传感器网络研究。

E-mail:liuxiansheng999@foxmail.com

杨秀梓,工学硕士,主要从事无线传感器网络研究。

E-mail:xiuziyang@126.com