# 基于嵌入式 USRP 的无线通信实现<sup>\*</sup>

葛 煦 陈为刚

(天津大学电子信息工程学院 天津 300072)

**摘要:** 针对便携式无线通信应用, 基于嵌入式软件无线电平台 USRP E110 设计实现了以二进制相移键控(BPSK)为调制方式的无线通信系统。在该系统中, ARM 处理器作为处理核心, 实现全部基带信号处理; FPGA(field programmable gate array)与射频子板作为射频前端, 实现数字上下变频、中频与射频信号转换等; GNU Radio 开源框架作为软件开发平台, 以流图的形式实现各基带信号处理, 如加扰与解扰、BPSK 调制与解调等。实际测试结果表明, 该系统可实现数据收发, 并且可以灵活配置收发频率、发射功率等参数, 具有体积小、功耗低等优点。

**关键词:** 嵌入式软件无线电; USRP E110; BPSK

中图分类号: TN914.3 文献标识码: A 国家标准学科分类代码: 510.1050

## Wireless communication system implementation using embedded USRP

Ge Yi Chen Weigang

(School of Electronic Information Engineering, Tianjin University, Tianjin 300072, China)

**Abstract:** Using the embedded software defined radio platform USRP E110, a wireless communication system which uses binary phase shift keying (BPSK) as the modulation method is implemented for portable wireless communication applications. In this system, the ARM processor acts as the processing core, implementing all baseband signal processing; FPGA(field programmable gate array) and radio frequency daughter board act radio frequency front-end, where digital up convert or digital down convert and the transition between the IF signal and the radio-frequency signal are implemented on; and GNU radio acts as the software development platform, implementing the base band signal processing in the form of a flow graph, such as scrambling and perturbation, BPSK modulation and demodulation. The results show that, the system can transmit and receive data using various parameters such as RF frequency, transmitted power and so on, which is portable and low power.

**Keywords:** embedded software defined radio; USRP E110; BPSK

## 1 引言

随着无线通信的快速发展, 出现了众多应对不同需求的无线通信体制, 而不同通信体制的无线收发机都不相同, 这使得无线收发机的实现面临很多挑战。软件无线电作为实现无线通信系统的重要技术, 旨在利用通用射频前端, 借助模数/数模转换, 利用数字信号处理器或通用计算机以软件编程的方式完成诸如调谐控制、信道编码译码、调制解调等各种收发机功能, 从而快速实现支持各类标准的无线通信系统, 是验证各种无线通信体制的理想平台<sup>[1]</sup>。

Ettus 公司研制的通用软件无线电外设 USRP1、USRP N210 等作为软件无线电平台, 受到了广泛关注。然而,

USRP1 与 USRP N210 的使用需要通用计算机, 即采用通用计算机实现基带信号处理, 板上 FPGA (field programmable gate array) 实现数字上下变频的架构<sup>[2]</sup>。这种架构的软件无线电平台存在体积较大、功耗大等缺点。针对该问题, Ettus 公司研制了嵌入式软件无线电平台 USRP E110, 本文基于该平台设计实现了以二进制相移键控(BPSK)为调制方式的无线数据传输系统, 并开发了有关上层应用软件。

## 2 USRP E110 简介

USRP E110 是基于中频架构<sup>[3]</sup>的嵌入式软件无线电外设, 使用 ARM 处理器代替通用计算机, 控制 FPGA 完成

收稿日期: 2015-11

\* 基金项目: 天津市科技兴海项目(KJXH2011-2)资助

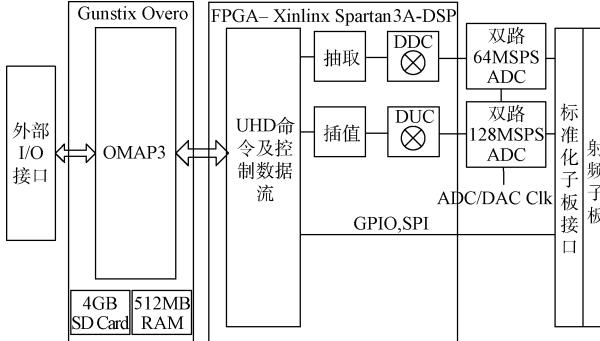

基带信号处理,从而使 USRP E110 的使用不再依赖通用计算机,非常适合应用于依赖小型化无线电设备的场景,如无线传感器网络<sup>[4]</sup>。如图 1 所示,USRP E110 由 ARM 处理器、FPGA、覆盖各种频段的射频子板以及外部 I/O 接口组成。

图 1 USRP E110 硬件结构

USRP E110 内置一个 800 MHz 的 OMAP3 ARM Cortex A8 处理器以及一个 TI C64 DSP 作为基带信号处理核心,内存容量为 512 MB,采用基于 Linux 内核并内建完整 GNU Radio 环境的 Angstrom 操作系统。同时它配备了 Xilinx Spartan 3A-DSP 3400 FPGA,可处理两路速率为 64 MS/s、精度为 12 bit 的模/数转换以及两路速率为 128 MS/s、精度为 14 比特的数/模转换,并可实现可变抽取速率下变频和可变内插速率上变频。

射频前端的射频子板与相应的天线实现中频模拟信号与射频模拟信号之间的转换。通过搭配不同的射频子板,USRP E110 的收发频率可达 DC~6 GHz。本文采用 WBX 宽带子板,其频率覆盖范围为 50 MHz~2.2 GHz。

USRP E110 的外部 I/O 接口主要有:1 个 10/100 Mbps 以太网接口、外部 TCXO 频率参考接口、USB HOST 接口、OTG 接口、串行配置接口、HDMI 接口和外部 MIMO 同步接口等。

USRP E110 采用的设备驱动为 UHD (universal hardware driver),软件开发环境是基于 GNU Radio 的开源软件框架<sup>[5]</sup>。UHD 为 USRP E110 提供宿主机驱动和应用程序编程接口;GNU Radio 提供实现不同功能的软件信号处理模块,并构建一套基于流图的信号控制和处理框架,能够快速高效地开发和拓展各种功能的无线通信系统<sup>[6-7]</sup>。

### 3 系统架构设计

#### 3.1 系统总体架构

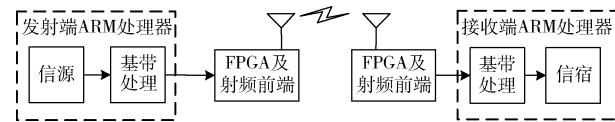

本文实现的基于 USRP E110 的无线通信系统的总体架构如图 2 所示。收发端的 ARM 处理器负责实现基带数字信号的处理;FPGA 及射频前端实现基带数字信号与射频模拟信号之间的转换。

图 2 系统总体结构

#### 3.2 系统收发机结构

本文采用 BPSK 作为调制方式设计实现的发射机与接收机的结构如图 3 所示。发射机的 ARM 处理器负责实现数据加扰、循环冗余校验(CRC)生成、BPSK 调制以及功率控制等基带信号处理,然后由 FPGA 及射频前端实现基带信号到射频信号的转换及发射;接收机首先由射频子板接收射频信号,然后将其转换为基带信号并交给 ARM 处理,由 ARM 处理器负责信道滤波、BPSK 解调、CRC 校验以及数据解扰,从而恢复出发端发送的数据。

图 3 收发机结构

#### 3.3 物理层帧结构

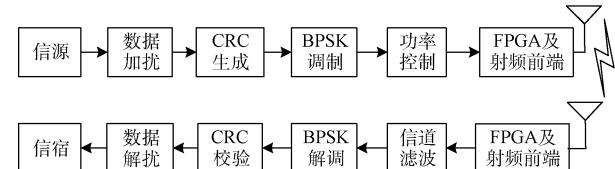

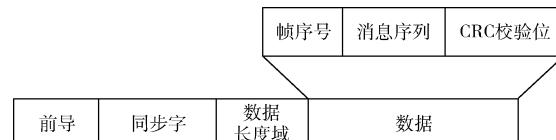

本文设计的物理层帧结构如图 4 所示,由前导序列、同步字、数据长度域以及数据域组成。

图 4 物理层帧结构

1)前导序列由 16 个比特序列组成,使自动增益控制模块(automatic gain control, AGC)在进行有用信号处理前快速达到稳定状态;

2)同步字为 64 bit 的伪随机序列,用于完成帧同步操作;

3)数据域长度占用 32 个 bit,单位为 Byte,表示数据域的长度;

4)数据域由帧序号、消息序列、CRC 校验位组成,帧序号与 CRC 校验位均占用 32 bit,信息序列的长度由用户输入数据决定。

### 4 系统实现

#### 4.1 数据加扰与解扰

当发送的信息比特流中存在较长的连“1”或连“0”子串时,接收机的同步性能将下降。因此发射机使用伪随机序列对数据进行随机化处理,使发送的比特流具有伪随机性,

从而缩短连“1”或连“0”子串的长度。

本文在收发端均存储了相同的扰码向量, 该扰码向量是一个由 15 阶线性反馈移位寄存器输出记录的长度为 32 768 bit 的 PN 序列, 并按 8 位封装成长度为 4 096 Byte 的向量。发送端根据扰码偏置和数据长度确定扰码序列, 和发送数据进行异或运算, 完成数据加扰; 接收端根据扰码偏置取定相同的扰码序列, 和接收数据进行异或运算, 恢复出原始数据。

#### 4.2 CRC 生成与校验

为对数据帧的传输正确性进行校验, 本文在发送端对加扰后的数据进行计算并附加 CRC 校验位。

本文采用的 CRC 参数模型为 CRC-32, 其生成多项式为:

$$g(x) = x^{32} + x^{26} + x^{23} + x^{22} + x^{16} + x^{12} + x^{11} + x^{10} + x^8 + x^7 + x^5 + x^4 + x^2 + x + 1 \quad (1)$$

在发送端, 利用生成多项式得到 CRC 校验位, 以 8 位数据的形式封装成字符串附加到信息序列末尾; 在接收端, 对接收数据中的信息序列再次生成 CRC 码, 将生成的 CRC 码与从接收数据中取出的 CRC 码相比较, 若二者相同, 则判定该帧传输正确, 都在判定该帧为误帧。

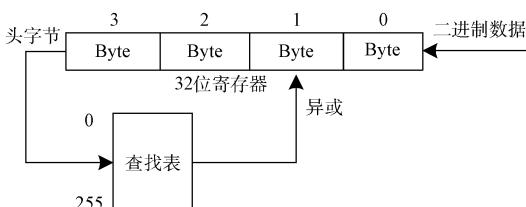

为提高运行速度, 本文采用查找表的方式生成 CRC 校验码<sup>[8]</sup>, 其原理如图 5 所示。根据生成多项式预先计算出高八位比特对应的校验码, 形成一张表。寄存器每次移位 1 Byte, 以寄存器的移出字节作为索引得到对应的校验码与寄存器异或并将结果存入寄存器中, 直到数据全部移入寄存器, 最后寄存器的值即为 32 位 CRC 校验码。

图 5 CRC 校验码的生成原理

#### 4.3 BPSK 调制

BPSK 调制由 BPSK 星座点映射、脉冲成形滤波组成, 如图 6 所示。

图 6 BPSK 调制过程

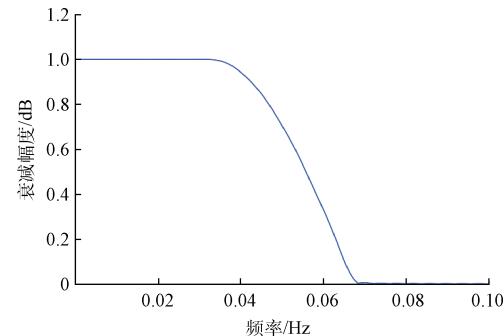

首先物理层数据通过 BPSK 星座点映射模块得到 BPSK 符号序列, 采用的星座映射方式为: 0 → 1; 1 → -1。然后, 利用脉冲成形滤波器对 BPSK 符号序列进行过采样与滤波, 从而生成 BPSK 基带脉冲采样序列。本文利用平方根升余弦滤波器实现脉冲成形模块<sup>[9]</sup>, 其中滚降系数

$\alpha = 0.35$ , 过采样率  $sps = 10$ , 平方根升余弦滤波器的幅频特性如图 7 所示。

图 7 平方根升余弦滤波器的幅频特性

#### 4.4 发送功率控制

FPGA 及射频前端首先将宿主机送入的以 16 bit 表示的 I、Q 两路基带信号转换为 14 bit 表示的信号, 然后分别进行 14 bit 位宽的数/模转换。因此基带输出信号的幅度与 DAC 的输出电流成线性正相关, 所以功率控制模块通过控制基带复信号的包络复信号的包络幅值, 进而控制发送功率。基带信号幅值因子  $Amp$  与 USRP 发射功率  $P$  (单位: dBm) 之间的关系如下:

$$Amp = 32\ 767 \sqrt{\frac{10^{P/10}}{100}} \quad (2)$$

#### 4.5 信道滤波

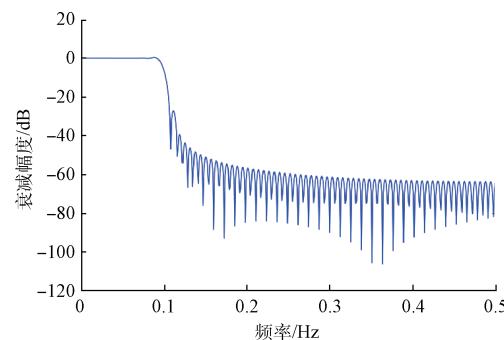

对接收机, 为滤除接收信号的带外噪声, 在 BPSK 解调之前, 首先经过一个低通滤波器。本文设计采用 Blackman 窗生成滤波器的抽头系数以获得更快的阻带衰减。基带过采样率为  $sps = 10$ , 截止角频率为  $\omega = 2\pi/10 = \pi/5$ 。本文实现的低通滤波器的幅频特性如图 8 所示。

图 8 信道滤波器幅频特性

#### 4.6 BPSK 解调

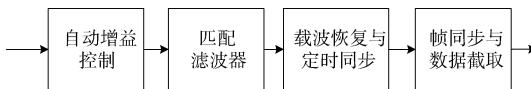

BPSK 解调主要包含 AGC、匹配滤波器、载波恢复与定时同步以及帧同步与数据截取这 4 个部分<sup>[10]</sup>, 如图 9 所示。

##### 1) AGC

在进行 BPSK 解调之前, 基带信号首先经过 AGC 模块

图 9 BPSK 解调过程

进行包络幅值调整,使信号的包络幅值稳定在 BPSK 解调器可接收的范围之内。设置 AGC 初始环路增益  $G = 1$ , 初始化参考电平  $Ref = 1$ , 达到稳态后, AGC 输出的复信号包络的幅度在 1 附近保持相对恒定。

#### 2) 匹配滤波器

匹配滤波器对 AGC 的输出信号进行匹配滤波,一方面使得 BPSK 解调器能够获得最大的信噪比,另一方面采用与发端脉冲成形相同的滤波器,两者形成级联效果,从而有效抑制码间串扰<sup>[11]</sup>。

#### 3) 载波恢复与定时同步

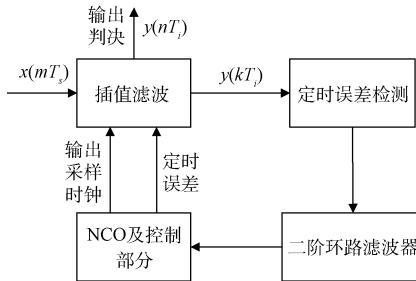

接收机采用数字锁相环技术<sup>[12]</sup>实现载波恢复与定时同步,从而解决由于信道时变特性导致的 BPSK 星座点的相位翻转问题<sup>[13]</sup>。数字锁相环结构如图 10 所示。

图 10 数字锁相环结构框图

图 10 中数控振荡器 (numerical controlled oscillator, NCO) 及控制部分为载波恢复模块,利用科斯塔斯环<sup>[14]</sup>实现残余频偏的估计和补偿。插值滤波、定时恢复和二阶环路滤波器组成定时恢复模块<sup>[15]</sup>,插值滤波器根据定时误差输入,进行插值计算并输出定时相位补偿后的时刻的采样值;定时相位误差检测器对输入信号的相位误差进行估计<sup>[16]</sup>;环路滤波器对相位检测器的输出相位误差进行滤波,实现环路带宽和阻尼系数的控制。本文定时误差检测的实现采用了改进的 Mueller & Muller 算法。进一步,取出载波与定时同步后输出复信号的实部并进行硬判决即可完成 BPSK 的硬解调。

#### 4) 帧同步与数据截取

为实现帧同步,确定消息序列的起始位置,本文实现的接收机在本地存储同步字序列 access\_code 并定义一个 64 bit 的线性移位寄存器 date\_reg。每次给 date\_reg 输入一位数据,然后将 date\_reg 中数据与 access\_code 进作异或运算,得到汉明距离。若汉明距离大于预设的阈值,则帧同步完成,并对输出的 8 位无符号字符型变量的次低位进行帧同步标记。

完成帧同步标记后,系统采用有限状态机的方式,根据数据长度和相关峰位置,完成数据的截取。状态机包含 3 个状态:同步搜索状态、同步状态和数据截取状态。

## 5 系统测试

### 5.1 测试平台与环境

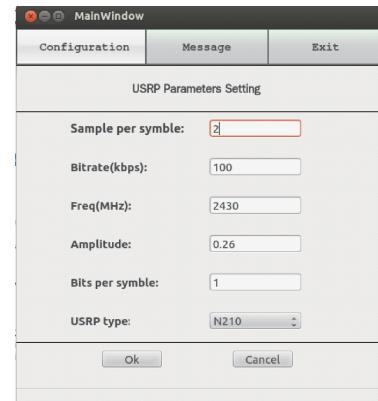

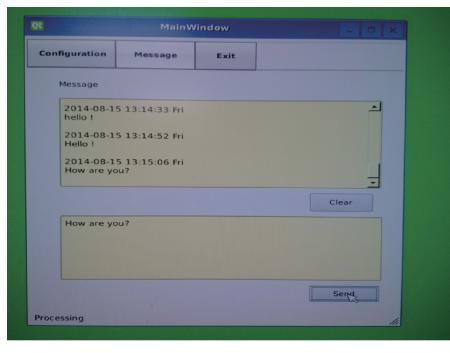

本文以 Qt 开发平台进行系统的软件开发。发射机的参数配置界面如图 11 所示,可以灵活地配置过采样率、比特速率、发射频率、发射功率、USRP 类型等参数,接收机的配置界面与之类似。

图 11 发射机参数配置界面

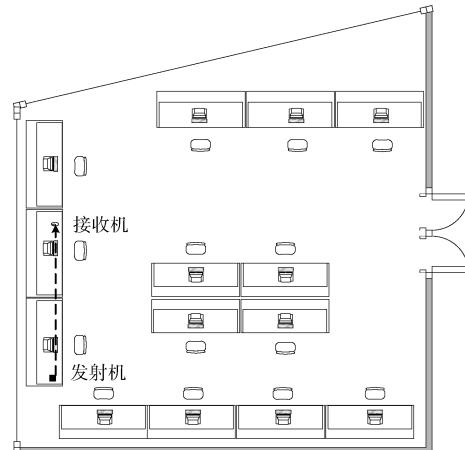

室内非视距路径的传输测试场景如图 12 所示,发射机和接收机之间的距离为 1.5 m。收发机参数设置如表 1 所示。

图 12 测试场景示意图

表 1 收发信机参数

| 参数        | 值       |

|-----------|---------|

| 符号采样率     | 10      |

| 比特速率      | 40 kbps |

| 发送频率/接收频率 | 560 MHz |

| 包络幅值(发射机) | 0.26    |

| 天线增益(接收机) | 45 dB   |

| 每个符号的比特数  | 1       |

| 传输距离      | 1.5 m   |

## 5.2 测试结果

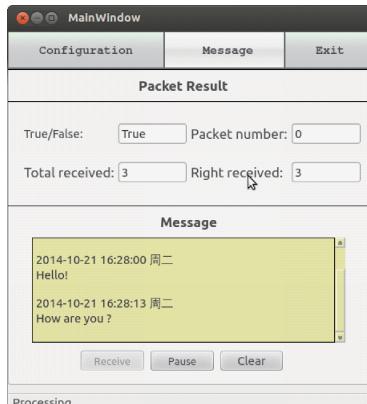

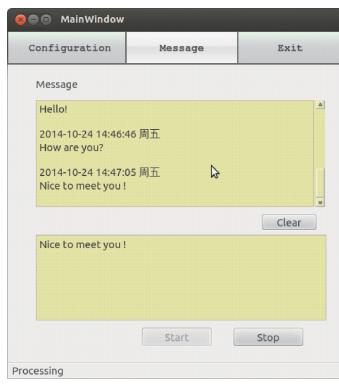

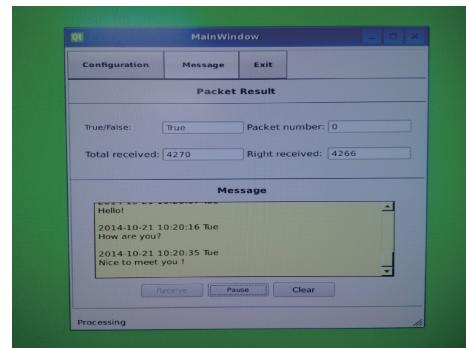

本文分别令 USRP E110 作为发射机和接收机进行测试以系统验证收发功能的正确性。测试时分为以下两种情形:1) USRP E110 为发射机、USRP N210 为接收机;2) USRP N210 为发射机,USRP E110 为接收机。

情形 1 测试结果如图 13 所示。情形 2 测试结果如图 14 所示。

测试结果表明,在表 1 所示参数情况下,基于 USRP E110 的无线通信系统可实现数据收发,并可对收发频率、发射功率、接收增益等参数进行实时配置。

(a) 发射机

(b) 接收机

图 13 情形 1 测试结果

(a) 发射机

(b) 接收机

图 14 情形 2 测试结果

## 6 结 论

基于嵌入式软件无线电平台 USRP E110 设计实现了采用 BPSK 作为调制方式的无线通信系统。系统以 USRP E110 内置的 OMAP3 ARM 处理器代替通用计算机作为处理核心,实现应用层操作处理和物理层基带信号处理,如数据加扰与解扰、CRC 生成与校验、BPSK 调制解调、信道滤波等,以 FPGA 与射频子板作为射频前端,实现信号的上下变频、数/模转换以及射频与中频信号之间的转换。测试结果表明,所设计的无线通信系统可实现数据传输,并可以灵活地配置收发频率、发射功率、接收增益等参数,具有便携性好、功耗低等优点,适用于需要小型无线通信设备的场景。

## 参考文献

- [1] ULVERSOY T. Software defined radio: Challenges and opportunities[J]. IEEE Communications Surveys & Tutorials, 2010, 12(4): 531-550.

- [2] REIS L G, BARROS A F, LENZI K G, et al. Introduction to the software-defined radio approach[J]. IEEE Latin America Transactions, 2012, 10(1):1156-1161.

- [3] 曾庆喜,王庆,杨英杰,等. USB 接口 GPS 中频信号采样器研究与实现[J]. 电子测量与仪器学报, 2012, 26(10): 883-888.

- [4] SHI W, JIANG Y, ZHAO Y. A backbone formulation algorithm in wireless sensor network based on cross-entropy method[J]. Instrumentation, 2014, 1(1): 38-48.

- [5] 杨晋生,李中品. 基于 USRP 的室内无线信道场强的仿真与测量[J]. 电子测量技术, 2015, 38(5): 131-134.

- [6] ZAKI G F, PLISHKER W, OSHEA T, et al. Integration of dataflow optimization techniques into a software radio design framework [C]. Asilomar Conference on Signals, Systems and Computers, Pacific Grove: IEEE Press, 2009: 243-247.

(下转第 189 页)