# AS5643 总线协议 IP 核设计与实现

吴嘉宝 张春熹 伊小素 王明

(北京航空航天大学仪器科学与光电工程学院 北京 100191)

**摘要:** AS5643 总线是为了满足航空飞行器中高速实时数据传输的应用需求而提出的一种高速总线技术,其以 IEEE 1394b 协议为基础并对该协议的实时性、确定性、可靠性以及消息传输机制进行增强改进。为了推动 AS5643 总线技术的应用,针对 AS5643 总线协议 IP 核进行研究,设计了基于 FPGA 的 AS5643 总线协议模块,并搭建了多节点的总线互联系统对 AS5643 总线协议模块的功能和性能进行测试。测试结果验证了所设计协议 IP 核满足 AS5643 协议规范,实现了高带宽的数据传输,能够满足航空飞行器的应用需求。

**关键词:** AS5643 总线; FPGA; IP 核设计

中图分类号: TP2 文献标识码: A 国家标准学科分类代码: 510.5020

## Design and implementation of IP core for AS5643 serial bus

Wu Jiabao Zhang Chunxi Yi Xiaosu Wang Ming

(School of Instrumentation Science of Opto-electronics Engineering, Beihang University, Beijing 100191, China)

**Abstract:** AS5643 high speed serial bus is proposed to meet the real-time high speed data transmission application requirements in aviation aircraft building upon the foundation of IEEE 1394b protocol which ameliorates and enhances its real-time capability, certainty, reliability and message delivery mechanism. To promote the application of AS5643 technology, a study is conduct on AS5643 protocol to design the AS5643 LLC IP core transmission node conformed to the protocol based on FPGA. We build an integrated system with several nodes to validate the functions and performances of AS5643 node by using the test equipment to monitor and analyse the transactions on the serial bus. The experiment and test results show that this AS5643 LLC IP core conforms with AS5643 protocol which can achieve reliable high bandwidth of data transfer in the aeronautic application field.

**Keywords:** AS5643 protocol; FPGA; IP core designing

## 1 引言

汽车工程师学会(society of automotive engineers)SAE AS1A3 Mil-1394b 任务小组于 2004 年提出的 SAE AS5643 协议<sup>[2]</sup>是专门针对军事航空领域的总线协议,是基于具有高带宽、高实时性和确定性的 IEEE 1394b(以下称 1394b)总线技术的改进,并已成功应用于美国的 F-35 联合战斗机(JSF)项目和 X-47B 无人机中。

目前针对 AS5643 协议的研究领域的权威是荷兰的 DAP 公司,与美国空军合作研制了完全基于自主知识产权的协议模块和高可靠产品,成果应用于 F-35 和 X-47B 中。国内对该领域的研究相对落后,目前处于样机研制阶段,大都采用在 1394b 链路层芯片上进行二次开发设计 AS5643 协议层的方式,导致硬件设计复杂、软件操作效率低、体积功耗大等缺点。为解决上述问题,本文

设计了直接基于 FPGA 的 AS5643 协议链路层,并对所设计的协议模块进行了详细的测试,验证了设计的正确性。

## 2 AS5643 协议介绍

SAE AS5643 具有高实时性、同时提供异步同步传输<sup>[3]</sup>、保证在特定时间内完成规定数据量的传输并且时间延迟低<sup>[4]</sup>等特性,更适用于军事和飞行器的网络传输数据总线。

### 2.1 传输机制

AS5643 在通信的确定性方面<sup>[5]</sup>做了以下限定:

1) 网络拓扑预分配

网络的拓扑根据应用的需求进行配置,并且在整个航电系统的生命周期内尽可能保持不变。

2) 强制根节点

在预配置的网络拓扑中,根节点指定到某一节点,不允许被更改。

### 3) 带宽预分配

每个节点都按照固定分配好的发送偏移时间来发送数据包,以达到分时复用<sup>[6]</sup>总线的目的,最大程度上保证了总线通信的确定性。

### 4) 通过帧开始包进行同步

该同步数据包由总线上的根节点按照预定义的固定周期发送,通知总线上所有的节点一个新的帧的开始。

### 5) 使用异步流数据包

异步流数据包在异步传输周期中的等时包,为周期性的非应答式通信,更适用于可靠的数据传输<sup>[5]</sup>。

### 6) 静态分配通道号

为总线上的节点分配固定地址,并且对于总线上非本地的数据包不接收的作用,进一步提高总线通信的确定性。

## 2.2 协议架构

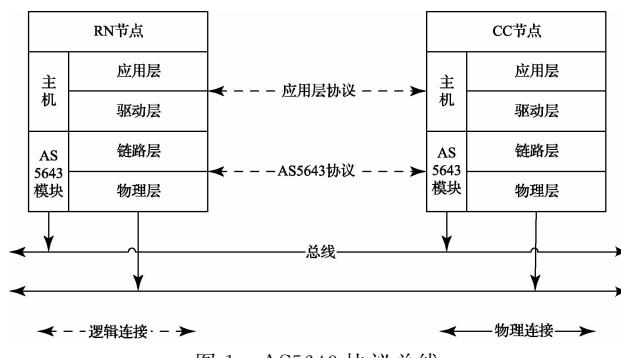

AS5643 协议节点包括两种:CC(control computer)节点充当根节点来管理总线上数据的传输;RN(remote node)节点是普通子节点。节点包括 3 个协议层:应用层、链路层和物理层。节点在符合 MIL-1394b 总线<sup>[7]</sup>上传输的具体架构如图 1 所示。

图 1 AS5643 协议总线

### 1) 应用层

应用层驻留在上位机中,应用软件通过调用驱动软件实现节点的功能<sup>[8]</sup>,例如节点的通道号分配和带宽预留等。

### 2) 链路层

提供了将事务层的请求和响应转化为相应操作,用广播包来统一总线上的信息和对异步数据流包的寻址、数据校验、数据格式处理等功能。

### 3) 物理层

物理层处理数据的编码、译码总线仲裁及传输和接收,确保所有设备可以正常访问总线<sup>[9]</sup>。

## 2.3 数据包类型

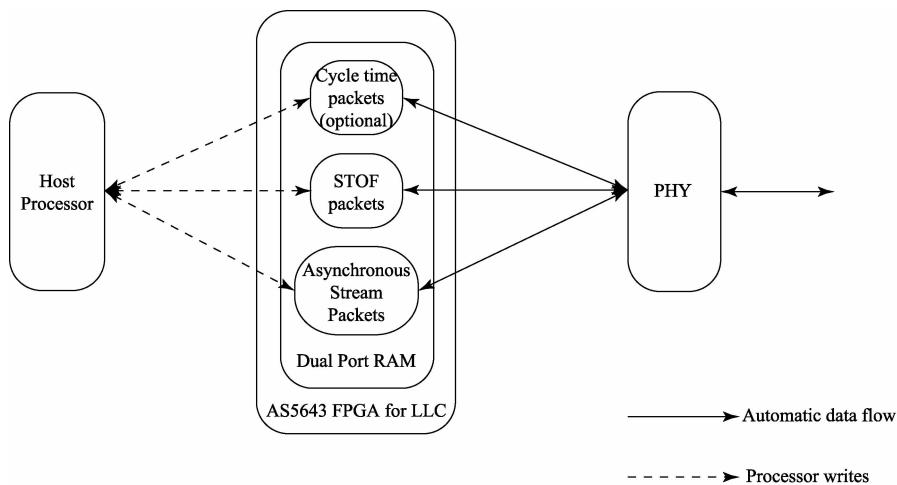

AS5643 协议定义的总线上从链路层传输到物理层的数据包可分为 3 种如图 2 所示。

图 2 AS5643 3 种数据包

### 1) 循环开始包

循环开始包为总线上的每个设备必须根据该值本地时钟,使用异步仲裁,周期为  $125 \mu\text{s}$ <sup>[10]</sup>。

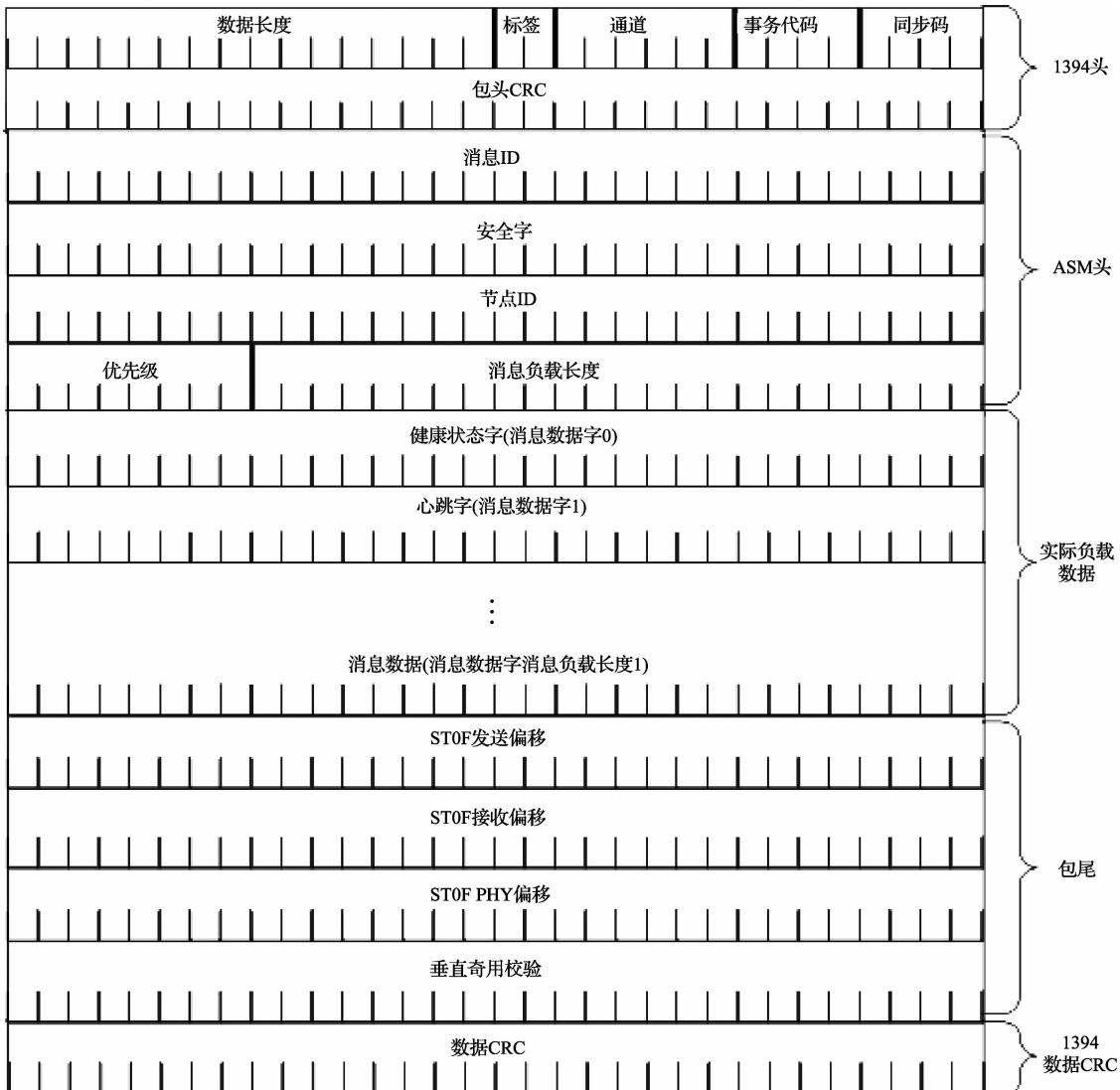

### 2) 异步流数据包

为了增强传输的可靠性,AS5643 使用异步流包进行

数据传输。异步流包使用异步仲裁,将 1394b 异步流包中的有效数据载荷部分进行了扩展,有效载荷长度减少了 40 字节,增加了匿名签署消息、健康状态字、心跳字、纵向奇偶校验和控制计算机状态字和包尾。异步流数据包,如图 3 所示。

图3 异步流数据包格式

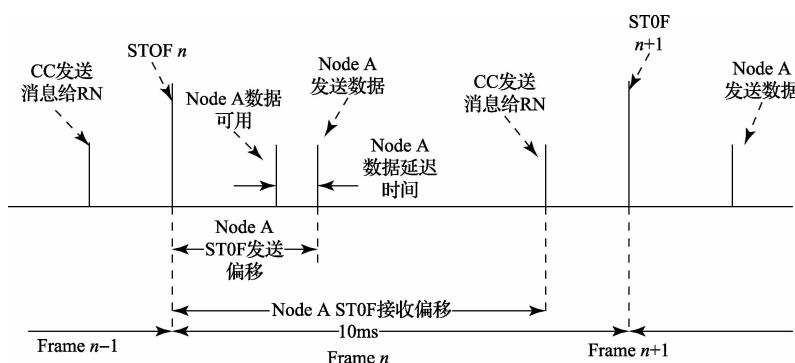

## 3) 帧开始包

AS5643协议中作为起始总线周期的固定长度为40字节的异步流包，用于进行网络同步广播。根节点按照固

定的帧速率周期(100 Hz)发送STOF包<sup>[11]</sup>，通道号为31。节点数据包发送同期如图4所示。

图4 节点数据包发送周期

### 3 AS5643 协议总体设计

AS5643 链路层 IP 核芯片通过 FPGA 实现,包括对数据的分析、打包和发送等。1394b 物理层协议芯片负责数据的传输,把 FPGA 处理的数据包进行编码和解码。

软件设计中,主机接口为应用程序提供控制信号的总线接口,链路层与物理层通过链路层请求 LREQ 和物理层请求 PINT 相互提供层与层之间数据传输的服务。

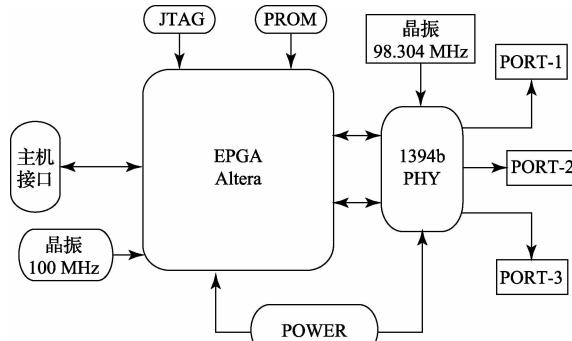

#### 3.1 硬件设计

硬件电路是实现通信的基础,一个完整的 AS5643 节点电路应由主机接口、FPGA 实现的链路层 IP 核、1394b 物理层芯片组成。AS5643 硬件设计模块如图 5 所示。

图 5 AS5643 硬件设计模块

由于 AS5643 相对于 1394b 的改进主要集中在链路层上,已有的传统的对 AS5643 协议的研究和设计都是将 AS5643 协议链路的设计建立在传统 1394b 链路层的基础上,也就是通过 FPGA 控制链路层对其进行二次开发。

AS5643 使用带宽为 400 Mbps 的 1394b 链路层芯片,节点含有两个 1394b 链路层物理层芯片和一个 FPGA 器件,增加了节点的体积,功耗也随之增大,降低了 AS5643 节点运行效率。而本设计则是使用 Verilog 语言,直接在 FPGA 中完成链路层和 AS5643 协议的同时设计,避免了二次开发,能够达到更高的带宽,提高系统的效率。而且,FPGA 对控制电路的设计采用直接译码,对 AS5643 中的控制寄存器进行读写以达到控制的目的,避免了由于在已有 1394b 链路层芯片上开发硬件造成的功耗大、效率低等缺陷,而且方便系统以后的设计<sup>[12-13]</sup>。本系统中,FPGA 采用的是 ALTERA 公司的 Cyclone II EP2C5。EP2C5 具有 4605 个逻辑单元,内部集成 26 个 RAM 块,总共 119 808 位的内部 RAM,两个锁相环(PLL)。

物理层选用 TI 公司的 1394b 物理层芯片 TSB81BA3,提供 1394b 数字串行信号的收发,带宽达到 800 Mbps<sup>[14]</sup>。每个线缆端口与两路差分线收发器通信,监控电路中总线的状态,并对其进行总线初始化和仲裁来控制数据包的传送和接收操作。FPGA 和物理层芯片之间的主要信号包括:控制信号 CTL[0 : 1]、数据信号 DATA[0 : 7]、链路层电源状态信号 LPS、链路层请求信号 LREQ、链路层开启信号 LKON、链路层时钟信号 LCLK、物理层时钟信号 PCLK 和物理层中断信号 PINT<sup>[15]</sup>。

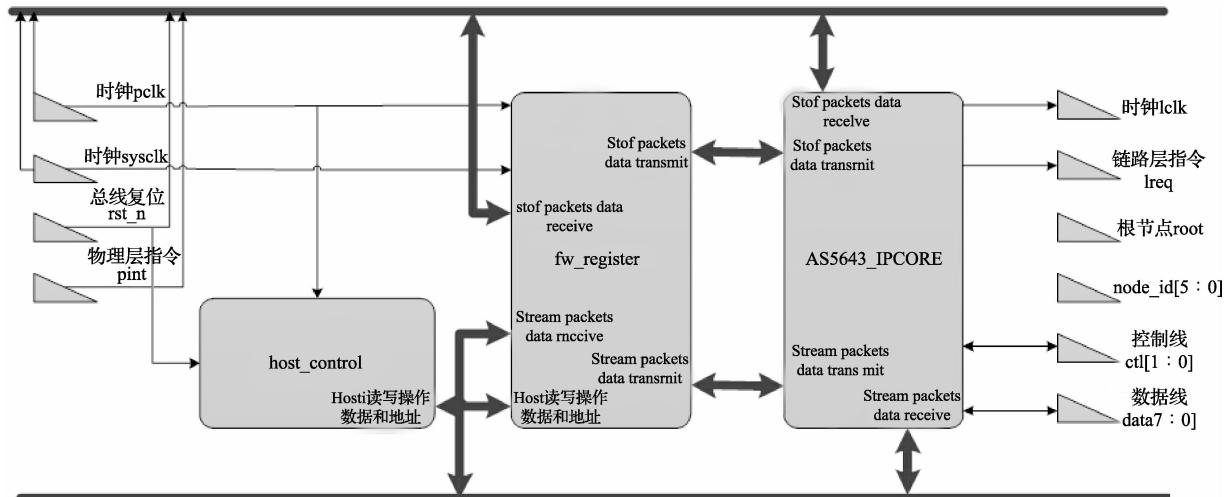

#### 3.2 软件设计

AS5643 节点的软件设计分为链路层协议 IP 核 (as5643\_ipcore) 模块、主机-链路层接口控制 (host\_control) 模块和寄存器 (fw\_register) 模块 3 部分。AS5643 节点软件设计如图 6 所示。

图 6 AS5643 软件总体设计

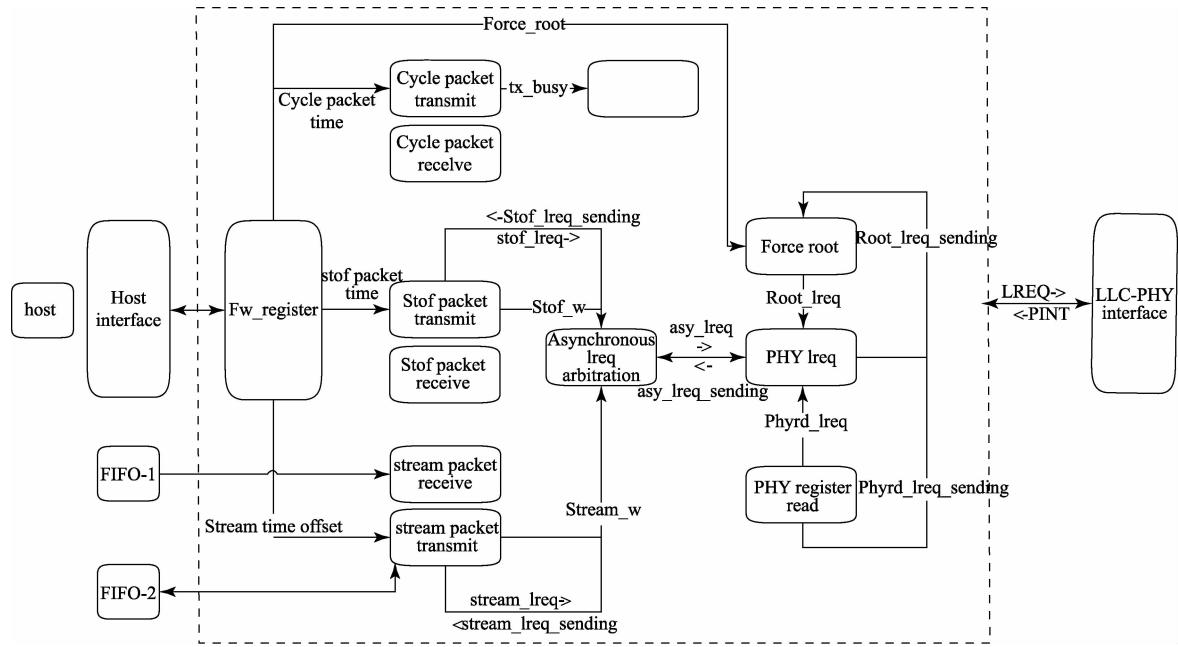

##### 3.2.1 链路层 IP 核设计

根据协议,AS5643 的 IP 核包含寄存器模块、循环开始包发送与接收模块、帧开始包发送与接收模块、异步流包发送与接收模块、总线状态模块、异步仲裁模块、链路层

请求模块、FIFO 缓存模块、读寄存器模块、强制根节点模块和链路-物理层接口。将软件设计模块化可提高设计的通用性;减少不同项目中同一功能设计、验证引入的工作量<sup>[16]</sup>。链路层 IP 核模块划分如图 7 所示。

图7 链路层IP核模块划分

其中,每个数据包的发送与接收模块都负责添加匿名用户消息和判断打包或解包的数据包是否经过了垂直奇偶校验;寄存器模块用于缓存数据包的相关信息;异步仲裁模块对整个数据的传输进行调控;FIFO缓存模块用于接收链路层数据包的读、写缓存等。

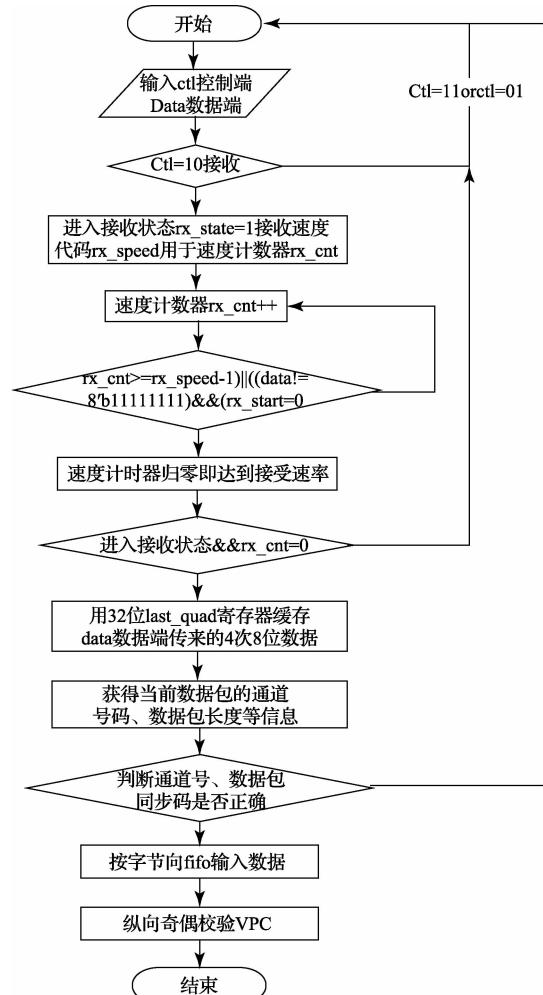

AS5643作为高速传输的总线协议,其链路层IP核中最首要的功能就是对数据包进行接收和发送,数据包的接收模块的程序流程图如图8所示。

首先根据CTL线和DATA线传来的数据,判断数据包长度length是否符合字节数、通道号等是否符合数据包格式要求等,再根据数据端传来的速度代码确定所兼容的速度,利用一个32位寄存器分步保存数据端传来的有效数据,并获得当前数据包的速度代码、通道号码、同步代码、数据包长度等信息,最后进行纵向奇偶校验,将接收到的帧开始包的时间信息转存到寄存器模块内。

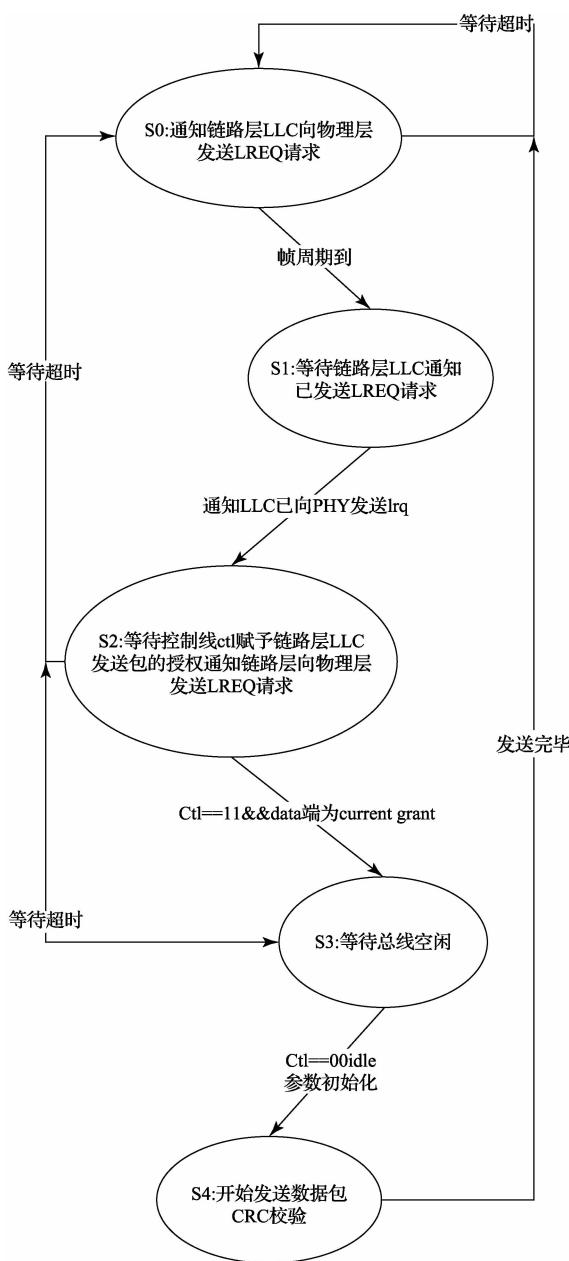

图9为数据包发送时的状态变化,当节点需要发送数据时,首先判断节点是否为根节点,是否需要强制根节点,若两者同时满足则在帧开始包时钟到达时向链路层请求模块申请向物理层发送LREQ请求,若链路层成功向物理层发送LREQ信息,那么在总线给予异步仲裁授权后,STOF包在经过CRC校验后发送给8位数据端。

其中,循环开始包发送和接收模块保留了1394b所使用的循环开始包机制,作为1394b的军用版本,AS5643虽然不再使用等时循环,但是为了保留完整的1394协议机制,本协议利用主机控制将1394的循环开始包发送与接收作为可选功能,可依据应用要求随时使能循环开始包功能。

图8 数据包接收程序流程

图 9 数据包发送状态机

### 3.2.2 主机接口设计

主机接口为主机提供控制总线接口, 提供主机访问 AS5643 IP 核通道, 包括与链路层 FPGA 同步的时钟、中断请求、主机读写使能端、读写数据段和读写请求地址端, 需

要通过对地址线数据线进行读写来访问内部寄存器。用户通过主机控制接口向总线上各个节点提出要求, 例如指定节点的中断请求、总线模式、异步流数据包中的控制字段、通道号和带宽偏移等。

例如, 总线在正常工作状态(非复位)中, 主机写使能为 1 时, 向 63 个 host\_register 寄存器一次按照地址传入控制信息; 在帧开始包发送周期到来时, 主机发送中断请求, 然后依次按照 stof\_time\_offset 记录的发送的帧开始包个数通过主机向寄存器依次为心跳字加 1。

#### 3.2.3 寄存器模块设计

AS5643 软件设计中的寄存器模块是我们在经过研究已有的军用 1394b 版本链路层芯片后, 自定义的能够存储节点信息、帧开始包和异步流包的各种控制与数据信息的寄存器组, 以保证总线复位发生, 就重新配置有关通信的链路层寄存器<sup>[17]</sup>, 及时更新内容。寄存器分为只读寄存器、待开发寄存器、可读可写寄存器、读写更新寄存器 4 种。

##### 1) 只读寄存器

记录 IP 和版本信息、总线的状态、根节点和节点标识、循环开始包和帧开始包的时间、模式与状态信息和所接收到的异步流包数据格式中的信息。

##### 2) 待开发寄存器

记录对物理层寄存器的读写操作的控制结果等信息和缓存 FIFO 的状态、控制和数据信息。

##### 3) 可读可写寄存器

若此时刻寄存器的地址为可写的, 那么就将主机控制模块传来的主机读写的数据传入地址对应寄存器中。

##### 4) 读写更新寄存器

记录中断的信息, 包括异步流包的发送与接收中断、帧开始包的发送与接收中断等。

## 4 测 试

### 4.1 测试环境搭建

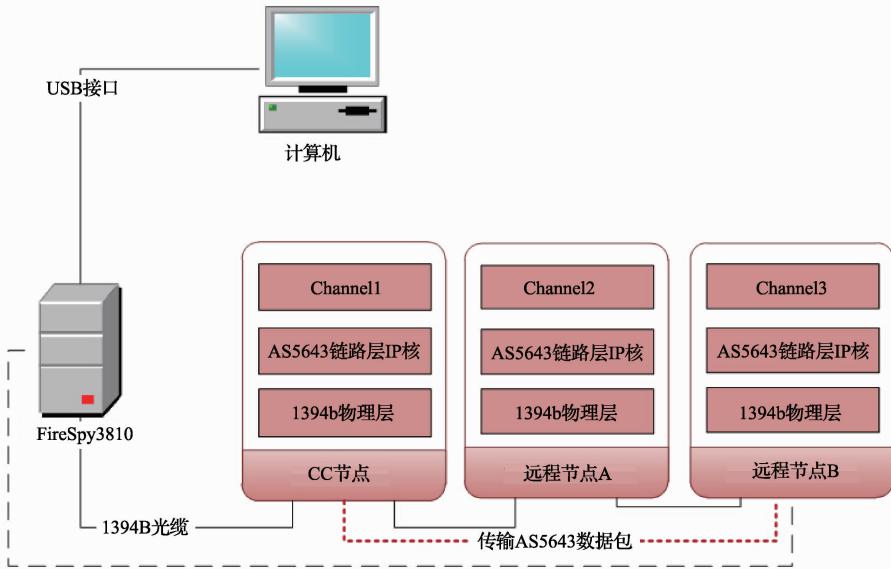

为了验证基于 FPGA 的 AS5643 链路层 IP 核设计的正确性, 建立了 4 个节点互联的通信系统。实验平台图 10 所示。实验系统由 3 个 AS5643 节点模块(其中一个配置为 CC 节点, 另外两个配置为远程节点 A 和 B)、FireSpy3810 协议分析仪和一台计算机组成。每个节点电路硬件是都安装一片实现 AS5643 协议链路层的 FPGA 和一个 1394b 物理层芯片。

图 10 实验组网连接

#### 4.2 测试结果

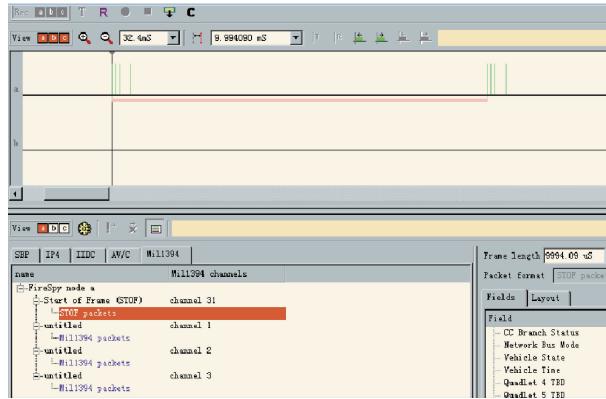

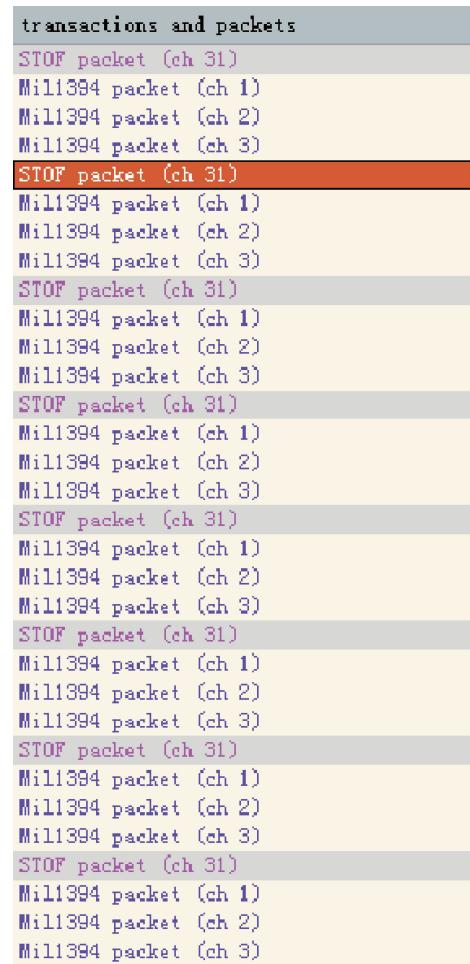

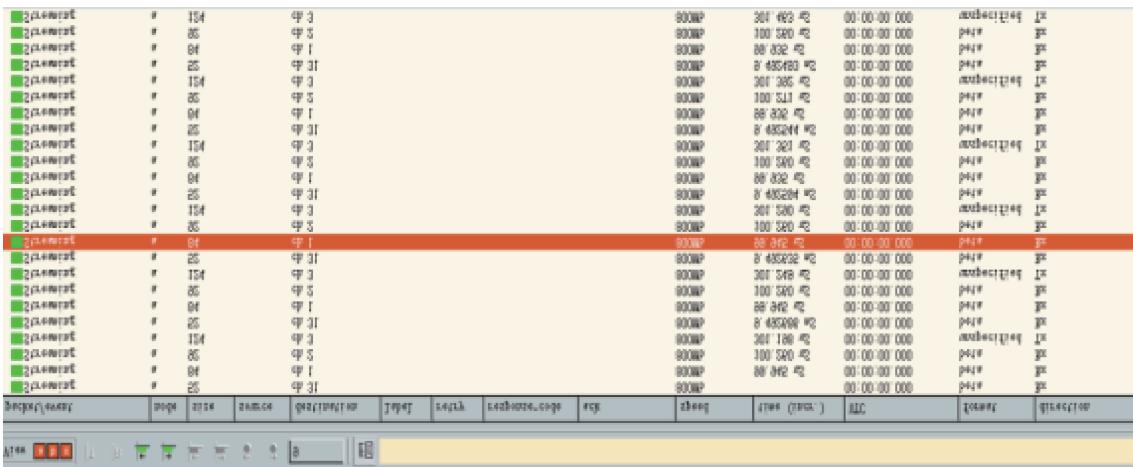

实验中,CC节点和两个远程节点的异步流包传输的通道号分别设置为1、2和3,其收发偏移值在AS5643链路层IP核的寄存器模块中已编码设置好。这里将CC节点、远程节点A和B的发送偏移分别设置为 $100\ \mu s$ 、 $200\ \mu s$ 和 $500\ \mu s$ ;CC节点每隔10 ms在Channel 31上发送一个STOF数据包。系统启动好,用IEEE 1394b协议分析仪FireSpy3810监测总线上的数据包,检测结果图11,在红色时间轴上,3个节点按照设定好的时间偏移以绿色线条显示。

图 11 各节点发送时间偏移

从实验中抓取的数据可以看出,如图12~15所示,节点传送的数据包格式、CC节点产生STOF包的周期、远程节点的传输偏移和各个数据包的传输速率都满足AS5643协议测试规范要求<sup>[18]</sup>,带宽达到800 Mbps,帧开始包、异步流包等数据包按照预先分配好的时间进行收发。

图 12 协议分析仪按时序抓取到的数据包

图 13 数据包传输速率

| Field                 | Value      |

|-----------------------|------------|

| CC Branch Status      | 8437780    |

| Network Bus Mode      | 0x40000000 |

| Vehicle State         | 0xFFE00000 |

| Vehicle Time          | 761990000  |

| Quadlet 4 TBD         | 0          |

| Quadlet 5 TBD         | 0          |

| Quadlet 6 TBD         | 0          |

| Quadlet 7 TBD         | 0          |

| Quadlet 8 TBD         | 0          |

| Vertical Parity Check | 0x8DF4348F |

图 14 帧开始包数据包格式

| Fields                        | Layout                       |

|-------------------------------|------------------------------|

| Field                         | Value                        |

| - Message ID                  | 101000001                    |

| - Reserved - Security         | 0                            |

| - Node ID                     | 127                          |

| - Priority                    | 15                           |

| - Message Payload Data Length | 40                           |

| Message Payload Data          |                              |

|                               | - Health Status 0            |

|                               | - Heartbeat 76198            |

|                               | - Data[0] 0xABCD0000 [.....] |

|                               | - Data[1] 0xABCD0001 [.....] |

|                               | - Data[2] 0xABCD0002 [.....] |

|                               | - Data[3] 0xABCD0003 [.....] |

|                               | - Data[4] 0xABCD0004 [.....] |

|                               | - Data[5] 0xABCD0005 [.....] |

|                               | - Data[6] 0xABCD0006 [.....] |

|                               | - Data[7] 0xABCD0007 [.....] |

| - STOF Transmit Offset        | 100                          |

| - STOF Receive Offset         | 100                          |

| - STOF Datapump Offset        | 100                          |

| - Vertical Parity Check       | 0xF6EBFB52B                  |

图 15 异步流数据包内容

5 结 论

AS5643 总线是一种具有高实时性、可靠性和确定性的高速航空总线技术，能够满足当今军用装备、航电系统对数据传输性能的苛刻要求，并以已经成功应用于美国

F-35战斗机和X-47B无人机等项目中。从传输机制、数据包格式和总线管理3个方面对AS5643协议进行分析，按照软硬件设计分别对链路层IP核、主机接口和寄存器模块进行开发，设计了AS5643总线协议模块，并且搭建了一套总线传输系统对所设计模块的功能及性能进行测试。经过实验测试证明，设计的AS5643协议链路层IP核符合AS5643协议规范，为AS5643总线在军用装备中的应用打下坚实的技术基础。

参考文献

- [1] IEEE 1394b-2002 IEEE Standard for a High Performance Serial Bus [S]. IEEE Computer Society, 2002.

- [2] 解文涛, 王锐. IEEE-1394 应用于航空安全关键系统的研究[C]//全国第五届信号和智能信息处理与应用学术会议专刊(第一册), 2011, 47(8s): 76-81.

- [3] MA Z F, SHEN J SH, SHI D L. A survey on high-speed serial data bus for aerospace onboard communication[C]//2013 Asia-Pacific Computational Intelligence and Information Technology Conference (APCIIT 2013), 2013.

- [4] Society of Automotive Engineers. IEEE 1394b interface requirements for military and aerospace vehicle applications [S]. SAE Aerospace Standard 5643.

- [5] WANG M, ZHANG CH X, YI X S. Performance evaluation of IEEE 1394b serial bus with Deterministic and Stochastic Petri Nets [J]. Communications, China, 2013, 10(2): 121-133.

- [6] GU G Y, ZHU L M, XIONG ZH H, et al. Design of a distributed multiaxis motion control system using the IEEE-1394 bus [J]. IEEE Transactions on

- Industrial Electronics, 2010, 57(12):4209-4218.

- [7] 张少峰,田泽,杨峰,等. 基于 AS5643 协议的 Mil-1394 仿真卡设计与实现[J]. 计算机技术与发展, 2013,23(8):168-171.

- [8] 赵彬,田泽,杨峰,等. 基于 AS5643 协议的接口模块设计与实现[J]. 计算机技术与发展, 2013,101(8):100-102.

- [9] 邱鹏,王广龙,陈建辉,等. 基于 IEEE 1394b 的光纤总线技术研究[J]. 仪表技术与传感器, 2010(11):38-40.

- [10] 田泽,李娜,程国建. 飞行控制系统中 Mil-1394b 仿真节点实现[J]. 电脑知识与技术, 2011, 7 (13): 3120-3124.

- [11] 程俊强,林坚. Mil-1394b 总线在飞行器管理系统中的典型应用分析[J]. 电脑知识与技术, 2014, 10(27):6504-6508.

- [12] 郭倩倩. 基于 FPGA 的 1394b 光纤总线接口设计[J]. 兵工自动化, 2010, 29(3):81-84.

- [13] 胡亚平. FPGA 与 CPU 高速接口的实现[J]. 国外电子测量技术, 2013, 32(4):66-68.

- [14] WANG M, ZHANG CH X, YI X S, et al. Modeling and performance evalution of a high speed serial bus [C]//2011 International Conference on Electronics and Optoelectronics (ICEOE 2011).

- [15] 朱榆涵,邵洪峰,伊小素,等. 基于 VersaPHY 的 IEEE1394 协议硬件设计[J]. 电子测量技术, 2012, 35(4):136-139.

- [16] 张松,李筠. FPGA 的模块化设计方法[J]. 电子测量

与仪器学报, 2014, 28(5):560-565.

- [17] 魏艳艳,田泽,王宣明. 一种 CCDL 的 FPGA 设计与实现[J]. 计算机技术与发展, 2014,24(5):120-124.

- [18] Society of Automotive Engineers. Test plan/procedure for AS5643 IEEE-1394b interface requirements for military and aerospace vehicle applications [S]. SAE-AS5657.

## 作者简介

**吴嘉宝**,硕士研究生,北京航空航天大学光学工程专业。主要研究方向为高速军用总线技术、光纤通信技术、信息融合技术。

E-mail:23788813@qq.com

**张春熹**,北航蓝天学者、光学工程学科责任教授,博士生导师。主要学术方向为光纤陀螺、新型加速度计、新源里新概念惯性器件;惯性导航与组合导航系统;光学传感技术与测量技术;精密仪器与光学仪器。

E-mail:zhangchuxi@buaa.edu.cn

**伊小素**,北京航空航天大学仪器科学与光电工程学院副教授。主要研究方向为光纤传感器(包括声压、速率传感),光电子器件,光纤陀螺空间应用技术。

E-mail:yixiaosu@buaa.edu.cn

**王明**,北京航空航天大学仪器科学与光电工程学院,博士生。主要研究方向为高速军用总线技术、光纤通信技术、空间网络技术。

E-mail:wangming@aspe.buaa.edu.cn

(上接第 71 页)

## 作者简介

**程龙**,1989 年出生,在读硕士研究生。主要研究方向电子学设计,光电跟踪与伺服控制技术。

E-mail:longcheng201304011@163.com

**王卫兵**,1986 年出生,硕士研究生,研究实习员,2013 年毕业于中国科学院长春光学精密机械与物理研究所,主要研究方向为光电跟踪控制技术。

E-mail:wangweibing10@126.com

**王挺峰**,1977 年出生,博士,研究员,硕士生导师,2005 年于中国科学院长春光学精密机械与物理研究所。主要

研究方向为光电测控与光电总体技术。

E-mail:wtfeng@sina.com

**郭劲**,1964 年出生,博士,研究员,博士生导师,2007 年于中科院长春光机所获得博士学位。主要研究方向为光电测控与光电对抗技术。

E-mail:guojin1964@126.com

**陈娟**,1961 年出生,博士,教授,研究员,博士生导师,2001 年于中国科学院长春光学精密机械与物理研究所。主要研究方向为光电跟踪与伺服控制技术。

E-mail:chenjuan@mail.ccut.edu.cn