DOI:10.19651/j.cnki.emt.1802358

# 高压大功率芯片封装的散热研究与仿真分析<sup>\*</sup>

杨勋勇<sup>1</sup> 杨发顺<sup>1</sup> 胡锐<sup>2</sup> 陈潇<sup>2</sup> 马奎<sup>1</sup>

(1.贵州大学大数据与信息工程学院 贵阳 550025; 2.贵州振华风光半导体有限公司 贵阳 550018)

**摘要:**以工作电压为70V、输出电流为9A的高压大功率芯片TO-3封装结构为例,首先基于热分析软件Flo THERM建立三维封装模型,并对该封装模型的热特性进行了仿真分析。其次,针对不同基板材料、不同封装外壳材料等情况开展对比分析研究。最后研究封装体的温度随粘结层厚度、功率以及基板厚度的变化,得到一个散热较优的封装方案。仿真验证结果表明,基板材料和封装外壳的热导率越高,其散热效果越好,随着粘结层厚度以及芯片功率的增加,芯片的温度逐渐升高,随着基板厚度的增加,芯片温度降低,当基板材料为铜、封装外壳为BeO,粘结层为AuSn20时,散热效果最佳。

**关键词:**封装散热;高压大功率芯片;散热效率;Flo THREM;TO-3封装;热导率

中图分类号: TN406 文献标识码: A 国家标准学科分类代码: 510.1050

## Thermal research and simulation analysis of high voltage and high power chip package

Yang Xunyong<sup>1</sup> Yang Fashun<sup>1</sup> Hu Rui<sup>2</sup> Chen Xiao<sup>2</sup> Ma Kui<sup>1</sup>

(1. College of Big Data and Information Engineering, Guizhou University, Guiyang 550025, China;

2. Guizhou Zhenhua Feng Guang Semiconductor Co. Ltd, Guiyang 550018, China)

**Abstract:** Take the high-voltage high-power chip TO-3 package structure with operating voltage of 70V and output current of 9A as an example, the three-dimensional package model is first established based on the thermal analysis software Flo THERM, and the thermal characteristics of the package model is simulated and analyzed. Secondly, comparative analysis is carried out for the presence/absence of substrates, different substrate materials, and different package materials. Finally, the temperature of the package is studied according to the thickness of the bonding layer, the power and the thickness of the substrate, and a package with optimized heat dissipation is obtained. The simulation results show that The higher the thermal conductivity of the substrate material and the package casing, the better the heat dissipation effect. As the thickness of the bonding layer and the power of the chip increase, the temperature of the chip gradually increases. As the thickness of the substrate increases, the temperature of the chip decreases. The heat dissipation effect is optimal when the substrate material is copper, the package casing is BeO, and the bonding layer is AuSn20.

**Keywords:** package heat dissipation; high voltage and high power chip; heat dissipation efficiency; Flo THREM; TO-3 package; thermal conductivity

## 0 引言

电子封装的作用主要是保护芯片、减小外界环境对芯片的影响,并为其提供良好的电气连接、机械支撑以及散热路径,对提高芯片的性能、使用寿命以及降低成本起到决定性的作用<sup>[1-4]</sup>。由于TO-3封装具有功率大、散热快、封装

工艺简单等特点,故高压大功率芯片大多采用TO-3封装。对于高压大功率芯片,因其工作在高电压、大电流的条件下,容易引起大量热量的积累而造成器件的失效,元器件的失效率随着结温的升高呈指数上升。结温每上升约10℃,器件的寿命就会减少一半<sup>[5-7]</sup>。因此,为了保证芯片的可靠性,对封装结构的热仿真分析变得越发重要<sup>[7-9]</sup>。

收稿日期:2018-11

\*基金项目:国家自然科学基金项目(61464002、61664004)、贵州省重大科技专项(黔科合重大专项字[2015]6006)、贵州省科技计划项目(黔科合平台人才[2017]5788号)、贵州省功率元器件可靠性重点实验室开放基金(KFJJ201504)项目资助

在散热方面,对于不同的结构和材料,需要考虑如下 4 个环节的散热问题,芯片到粘结层,粘结层到基板,基板到冷却装置以及芯片到封装外壳。这 4 个环节构成高压大功率的传热通道,其中任何一个环节失败都影响高压大功率芯片的散热,因此,要使封装体具有良好的散热特性并得到一个较好的散热方案,深入研究有无基板时两种封装结构的温度对比、不同基板材料、封装外壳材料对封装体散热的影响以及功率、粘结层厚度和基板厚度对封装结构温度的影响有重要的意义<sup>[10-13]</sup>。

本文首先针对高压大功率芯片设计其封装结构,基于 Flo THERM 热分析软件建立封装模型,然后对该模型的散热特性进行仿真分析。研究当采用不同基板材料、不同封装外壳材料和改变芯片功率时封装结构温度的变化,最后研究当采用 BeO 陶瓷材料作为基板、AuSn20 材料做粘结层、环氧树脂做封装外壳时,封装体的温度随粘结层厚度、基板厚度的变化。

## 1 封装结构的设计

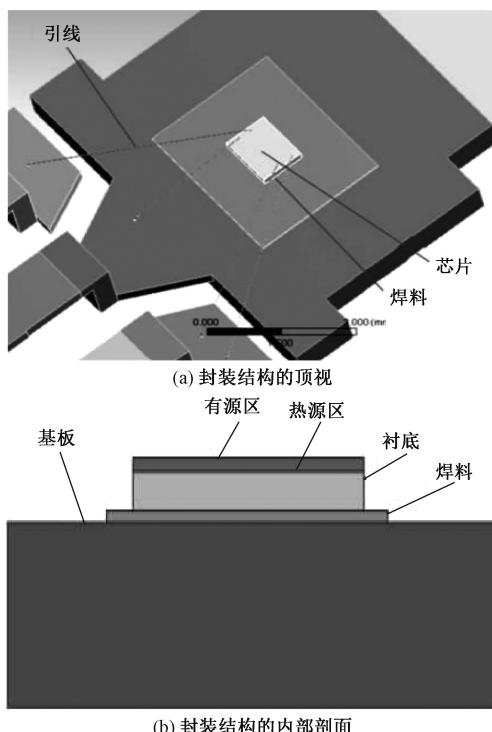

针对高压大功率芯片的封装结构,选用 TO-3 封装,其封装外形和封装结构的内部剖面图如图 1 所示。

图 1 TO-3 封装结构

芯片的封装是指利用微细加工技术,将芯片及其他相关部分固定在框架或基板上,引出接线端子并通过可塑性绝缘介质灌封固定,以构成整体立体结构的一种工艺。封装的基本工艺流程包括如下几步:芯片切割、芯片贴装、芯片键合、成型、上焊锡和打码等<sup>[14]</sup>。从图中可以看出,封装

结构主要由六部分组成,分别是基板、粘结层、芯片、引脚、引线和封装外壳<sup>[15]</sup>。

基于 TO-3 的封装结构,利用 Flo THERM 热分析软件建立封装模型,对模型进行仿真,为了简化仿真,这里做一个近似,实际封装中引线的形状是弯曲的,根据引线的实际长度进行简化,使其与坐标轴平行,并且由于引线的数量很多,详细建模会耗费太多的计算资源,通过 8 个具有各向异性的长方体(cuboid)来简化引线。模型中所设置的各组成部分的几何尺寸如表 1 所示。

表 1 模型各组成部分的几何尺寸 (mm)

| 组成   | 几何尺寸                          |

|------|-------------------------------|

| 基板   | $1 \times 1 \times 5$         |

| 有源区  | $6.3 \times 6.3 \times 0.075$ |

| 衬底   | $6.3 \times 6.3 \times 0.3$   |

| 粘结层  | $6.3 \times 6.3 \times 0.025$ |

| 封装外壳 | $1 \times 19 \times 0.8$      |

## 2 封装模型的热仿真分析

### 2.1 仿真条件的设置

基于实际的情况,仿真环境和边界条件分别设置为:1)环境温度为 27 ℃;2)采用强迫空气对流,芯片表面和基板表面都是通过风扇进行对流,忽略辐射散热,换热系数为 10 W/m<sup>2</sup>·K;3)热源的结构定义为  $6.3 \times 6.3 \times 0.075$  mm 的立方体,由于该芯片的工作电压为 70 V,输出电流为 9 A,静态功耗为 125 W,故定义模型中有源区的功率为 125 W。由于考虑基板和封装外壳的热传导,对基板和封装外壳进行网格约束,在基板厚度方向和封装外壳厚度方向至少设置 3 个网格,这里皆设置为 10,并且设置膨胀网格的距离为 5%,保证系统网格在各模块之间平滑过度。

### 2.2 不同的基板材料、封装外壳材料对芯片散热的影响

基于 TO-3 的封装结构,这里分别选取四种常用的基板材料和封装外壳材料,将四种基板材料或封装外壳材料依次嵌入仿真模型中进行仿真,当仿真不同的基板材料对芯片温度的影响时,除了基板材料,模型其它组成部分的具体参数不变,同理,当仿真不同的封装外壳材料对芯片温度的影响时,除了封装外壳材料,模型其它组成部分的具体参数保持不变,选取的四种基板材料和封装外壳如表 2 所示。

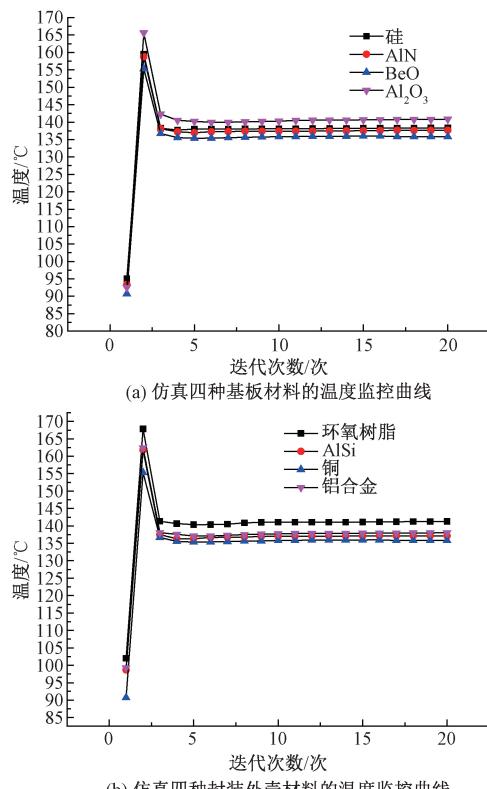

先仿真不同的基板材料对芯片温度的影响,将模型中基板模块的材料属性先定义为硅进行仿真,再定义为 AlN 进行仿真,然后又定义为 BeO 进行仿真,最后定义为 Al<sub>2</sub>O<sub>3</sub> 进行仿真;然后仿真不同的封装外壳材料对芯片温度的影响,以环氧树脂、AlSi、铜、铝的顺序分别进行仿真,仿真结果如图 2 所示。

表2 四种基板材料和四种封装外壳的参数

| 分类     | 材料名称                           | 热导率/(W/(m·K)) |

|--------|--------------------------------|---------------|

| 基板材料   | 硅                              | 150           |

|        | AlN                            | 250           |

|        | BeO                            | 290           |

|        | Al <sub>2</sub> O <sub>3</sub> | 25            |

| 封装外壳材料 | 环氧树脂                           | 0.418         |

|        | AlSi                           | 175           |

|        | 铜                              | 385           |

|        | 铝合金                            | 130           |

图2 仿真不同基板材料、封装外壳的温度监控曲线

从图2可以得到,当基板材料为Al<sub>2</sub>O<sub>3</sub>时,温度最高,为140.82℃,Al<sub>2</sub>O<sub>3</sub>的热导率是四种基板材料中最低的,基板材料为BeO时,温度最低,为135.815℃,BeO的热导率是四种基板材料中最高的;当封装外壳为环氧树脂时,封装体的温度最高,温度为141.272℃,环氧树脂的热导率是四种封装外壳材料中最低的,封装外壳为铜时,温度最低,为135.815℃,铜的热导率是四种封装外壳材料中最高的。因此,从图2中可以知道,材料的热导率越高,封装结构的温度越低,散热效果越好。

### 2.3 芯片温度随功率变化、基板厚度、粘结层厚度的变化

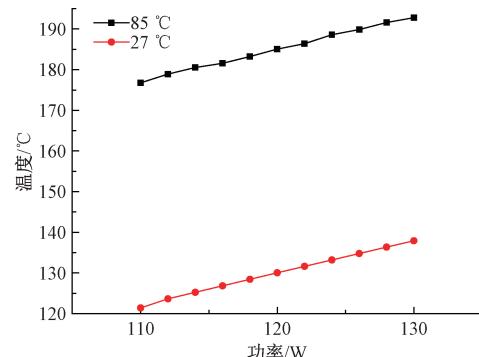

当芯片的功率发生变化时,芯片的温度会改变,设置芯片的功率从110 W变到130 W,分别仿真了环境温度为

27℃和85℃时芯片温度随功率变化的情况,仿真结果如图3所示。

图3 芯片温度随功率的变化

从图3知,封装体的温度随芯片功率的增加而升高,功率越大,芯片的温度越高。

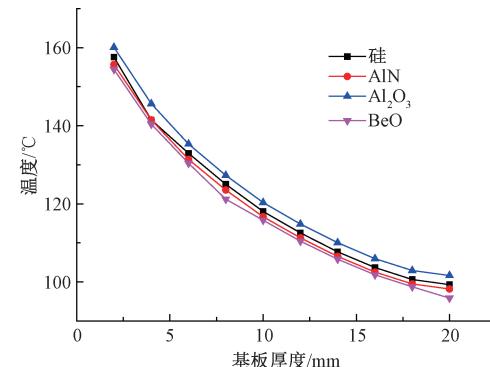

为了研究芯片温度随基板厚度的变化情况,这里设置基板厚度从1~20 mm,对表2中的四种基板材料进行仿真对比,结果如图4所示。

图4 芯片温度随基板厚度的变化

从图4得到,在1~20 mm之间,芯片的温度随基板厚度的增加而降低,基板越薄,芯片的温度越高,变化越急剧,随着基板厚度的增加,温度逐渐降低,且温度的变化越来越缓慢,从图4也可以看出,基板材料的热导率越高,散热特性越好。

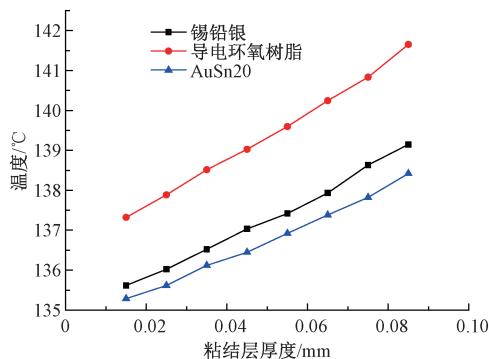

粘结层的作用是将芯片固定于封装基板上,由于其热导率较低,芯片散热受到很大限制,其厚度的改变对芯片的散热也有很大的影响,为了研究粘结层厚度对芯片散热的影响,设置粘结层的厚度从0.015 mm到0.085 mm,对模型进行仿真。并且这里选择了三种粘结层材料进行对比仿真,分别是锡铅银、导电环氧树脂、AuSn20,其热导率分别为50 W/(m·K)、0.8 W/(m·K)、57 W/(m·K)。仿真结果如图5所示。

从图5得到,芯片的温度随着粘结层厚度的增加而升高,并且粘结层材料的热导率越低,芯片的温度上升越快,材料的热导率越高,散热特性越好,芯片温度的变化相对缓慢。

图 5 芯片温度随粘结层厚度的变化

## 2.4 仿真结果的分析

由仿真结果知,芯片的温度随功率和粘结层厚度的增加而升高,随基板厚度的增加而降低;并且材料的热导率越高,其散热效果越好。从仿真结果得到,当模型中的基板材料为铜、封装外壳为 BeO,粘结层为 AuSn20 时,散热效果最佳,模型中各组成部分的具体参数如表 3 所示。

表 3 模型各组成部分的材料和热导率

| 组成    | 材料名称   | 热导率/(W/(m·K)) |

|-------|--------|---------------|

| 芯片    | 硅      | 150           |

| 引线及引脚 | 铜      | 385           |

| 粘结层   | AuSn20 | 57            |

| 基板    | BeO    | 290           |

| 封装外壳  | 铜      | 385           |

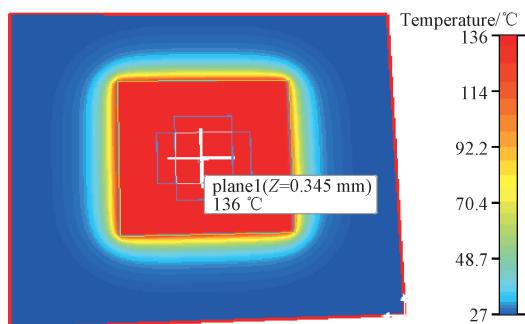

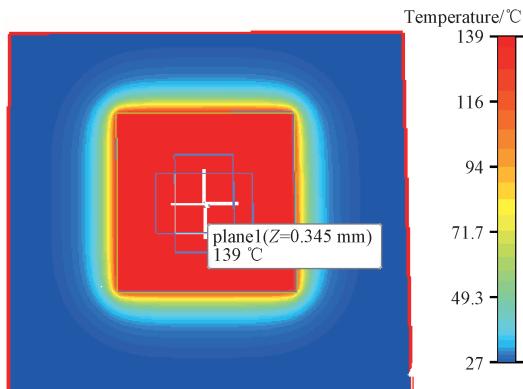

对模型进行热仿真,其温度显示平面图如图 6 所示。

(a) 整体封装结构温度显示平面顶视图

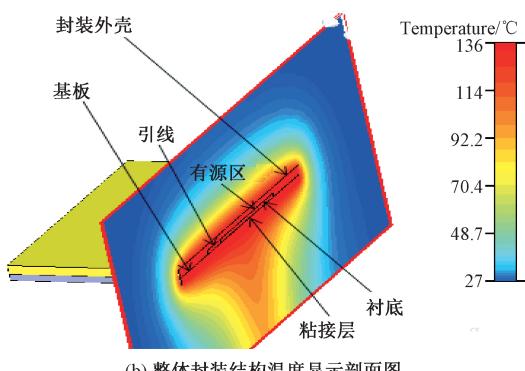

(b) 整体封装结构温度显示剖面图

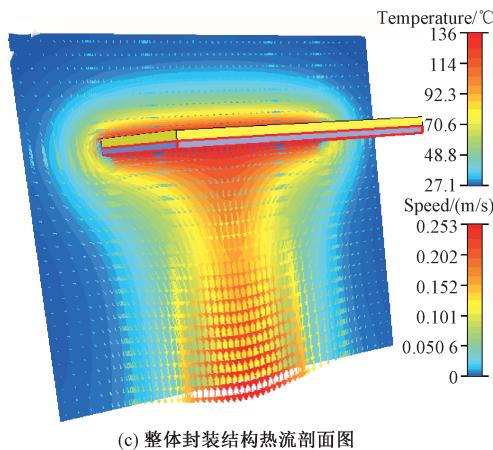

(c) 整体封装结构热流剖面图

图 6 整体封装结构的热场分布仿真结果

从图 6 可以看出,最高温度为 136 °C,位于芯片有源区的中央,向四周温度逐渐降低,从图 6c 可以看出,温度沿着基板方向逐渐降低,传热的路径为芯片到粘结层,粘结层到基板,最后传到环境中,图中红色表示最高温度区域。若把铜金属外壳换成环氧树脂外壳,其温度显示平面图将如图 7 所示。

图 7 模型中用环氧树脂做外壳时的温度显示平面图

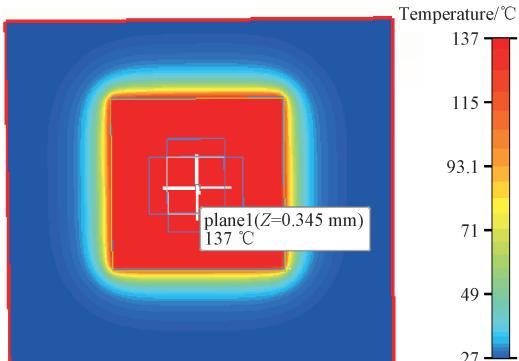

从图 7 可以看出,若把封装外壳材料换成环氧树脂,封装体的温度变高,从 136 °C 升到 139 °C,温度上升了 3 °C,环氧树脂的热导率比铜要低很多,热导率越低,传热越困难,芯片的温度越高。若把基板材料换为 AlN,其温度显示平面图将如图 8 所示。

从图 8 可以看出,当基板材料由 BeO 陶瓷基板更换为 AlN 陶瓷基板时,封装模型的温度变为 137 °C,比基板材料为 BeO 时升高了 1 °C,可以看出,基板材料热导率的高低对散热有很大的影响。在对模型整体结构的仿真过程中,各组成模块几何尺寸的设置如表 1 所示,由图 4、5 知,增加基板厚度和稍微减小粘结层的厚度,封装体的温度将会更低,根据实际封装的需要,选取合适基板的厚度、粘结层的厚度以及封装外壳材料,便可以得到一套散热效果较佳的封装方案。

图8 模型中用AlN做基板材料时的温度显示平面图

### 3 结 论

本文分别仿真了不同基板材料、不同封装外壳材料对芯片散热的影响以及仿真了芯片温度随功率、基板厚度以及粘结层厚度的变化,最后得出一个散热较好的封装方案。结果表明:基板材料和封装外壳的热导率越高,其散热效果越好;封装体的温度随基板厚度增加而降低,随功率的增加和粘结层厚度的增加而升高;最后得出散热效果最佳的封装方案为采用BeO陶瓷材料做基板、AuSn20材料做粘结焊料、铜做封装外壳。

### 参考文献

- [1] 龙乐. 电子封装技术发展现状及趋势[J]. 电子与封装, 2012, 12(1): 39-43.

- [2] KIM J, LEE K, PARK D, et al. Application of through mold via (TMV) as PoP base package[C]. Proceedings of the 58th Electronic Components and Technology Conference. Los Angeles, CA, USA, 2008: 1089-1092.

- [3] MAEDA T, SAKAI T, SAKEMI S, et al. Advanced soldering paste suitable for package on package process [C]. Proceedings of International Conference on Electronic Materials and Packaging. Los Angeles, CA, USA, 2006: 1-20.

- [4] CARSON F, LEE S M, YOON I S. The development of the fan-in package-on-package [C]. Proceedings of the 58<sup>th</sup> Electronic Components and Technology Conference. Los Angeles, CA, USA, 2008: 956-963.

- [5] PINJALA D, NAVAS K, XIE L, et al. Thermal design of heat spreader and analysis of thermal interface materials for multi-chip package [C]. 2002 Electronic Components and Technology Conference, 2002: 1119-1123.

- [6] WU X M, LIU X Y, MA H, et al. Low thermal resistance design for a 2.5D package [C]. 14th Int Conf Elec Packag Technol. Dalian, China, 2013: 431-434.

- [7] SOMASUNDARAM S, TAY A A O. Measurement of thermal resistance of TIMs, heat sinks and interfaces in thermal management [C]. 34th Int Elect Manufac Technol Conf. Melaka, Malaysia, 2010: 1-5.

- [8] SIM L T, DARAKORN S L. Thermal resistance enhancement by optimizing TO package thermal contact [C]. 34th IEEE/CPMT Int Elec Manufac Technol Symp. Melaka, Malaysia, 2010: 1-6.

- [9] 苏达,王德苗. 大功率LED封装散热技术研究[J]. 半导体技术, 2007, 32(9): 742-749.

- [10] 刘宗源. 大功率LED封装设计与制造的关键问题研究[D]. 武汉:华中科技大学, 2010.

- [11] 王剑峰,刘斯扬,孙伟锋. 基ANSYS的TO-220封装功率器件热特性校准及优化设计[J]. 电子器件, 2015, 38(4): 735-738.

- [12] LEE T S, DARAKORN S L. Thermal resistance enhancement by optimizing to package thermal contact [C]. 2009 11th Electronics Packaging Technology Conference, 2009: 1-6.

- [13] 吴懿平,丁汉,吴丰顺. 电子制造技术基础[M]. 北京:机械工业出版社, 2005.

- [14] 郑志强,程秀兰,TA F. 功率器件封装工艺中的铝条带键合技术[J]. 电子与封装, 2008, 8(12): 5-9.

- [15] 王成华,陈鑫,卜刚等. 集成电路设计基础[M]. 北京:北京航空航天大学出版社, 2011.

### 作者简介

**杨勋勇**,硕士研究生,主要研究方向为模拟集成电路设计和功率半导体器件。

E-mail: 3433372328@qq.com

**杨发顺**,博士,硕士生导师,主要研究方向为半导体功率器件与功率集成技术研究、半导体集成电路设计。

E-mail: fashun@126.com