DOI:10.19651/j.cnki.emt.1802228

# 8 通道数字信号时序分析实验装置设计

汪兴海 毕敬腾 孙雪丽

(海军航空大学航空基础学院 烟台 264001)

**摘要:** 为了丰富数字逻辑设计实验教学内容,拓展数字电路实验测试设备功能,基于 FPGA 设计 8 通道数字信号时序分析装置。该装置自带 8 路标准测试信号,通过 2 个按键实现 8 位触发字的设置,当 8 路输入信号符合触发条件时,使能片上 RAM 存储模块实现对 8 路数字信号的存储。存储器满时使能 DA 转换,通过生成两路模拟信号送入数字示波器 X、Y 通道,利用示波器的 X-Y 显示模式实现 8 路数字逻辑信号的显示;具备手动光标测试功能,能够通过 LED 显示光标所对应的 8 路逻辑信号。该装置解决了数字电路实验过程中依靠示波器无法同时观测多路逻辑信号的问题,同时能够作为一个工程实践案例引导学生基于 FPGA 进行数字系统设计。

**关键词:** FPGA; 逻辑分析; 李沙育图形; D/A 转换

中图分类号: TN89 文献标识码: A 国家标准学科分类代码: 510.10

## Design of 8 channel digital signal timing analysis experimental installation

Wang Xinghai Bi Jingteng Sun Xueli

(Naval Aeronautical University Aviation Foundation College, Yantai 264001, China)

**Abstract:** In order to enrich the teaching content of digital logic design experiment and expand the function of digital circuit experiment testing equipment, an 8-channel digital signal timing analysis device is designed based on FPGA. The device has 8-channel Standard Test signal, and the 8-bit trigger word is set by two keys. When the 8-channel input signal meets the trigger condition, the on-chip RAM is enabled. The storage module realizes the storage of 8 digital signals; when the memory is full, the DA conversion is enabled; two analog signals are generated and sent to the X and Y channels of the digital oscilloscope; the display of 8 digital logic signals is realized by using the X-Y display mode of the oscilloscope; it has the function of manual cursor test and can display the corresponding 8 logos through the LED cursor. Edit the signal. The device solves the problem that the oscilloscope can not simultaneously observe the multi-channel logic signal in the process of digital circuit experiment. At the same time, it can be used as an engineering practice case to guide students to design the digital system based on FPGA.

**Keywords:** FPGA; logic analysis; lissajous figures; D/A conversion

## 0 引言

近些年,随着部队装备数量以及训练频率的增加,设备之间的联通性故障时有发生,给设备操作人员带来了很大的麻烦<sup>[1]</sup>。设备之间绝大部分采用数字信号通信,因此培养学生在校期间掌握数字逻辑分析仪的基本原理和数字电子系统分析的技能愈发重要。目前基层部队和院校实验室大部分依赖示波器进行信号分析,学生对于多通道数字信号的分析理解缺乏硬件平台的保障<sup>[2]</sup>。目前大部分简易逻辑分析仪大都采用单片机+FPGA 模式设计,通过 TFT 实现数据显示,增加了显示环节的设计任务和成本,没有充分利用示波器的显示功能<sup>[3-4]</sup>。本设计充分融合示波器的信

号显示功能,以培养学生掌握多通道数字信号分析技能,理解逻辑分析仪基本原理和示波器显示原理,强化数字电路系统设计能力为目标,设计了 8 通道数字信号时序分析装置,拓展了实验设备功能,丰富了实验教学内涵<sup>[5]</sup>。

## 1 总体方案设计

数字信号时序分析装置需自带 8 路标准测试信号,同时具备信号采集与分析电路,实现对 8 路数字逻辑信号的采集与分析。需满足如下要求:

1)能够产生 8 路标准测试信号,8 路并行信号构成位宽为 8、状态数为 8 的循环移位序列码,如:00000101-00001010-00010100-…-10100000-01000001-10000010-0000

0101。每路信号位宽为  $10 \mu s$ , 周期为  $80 \mu s$ 。

2)能够手动设置触发条件,通过8位触发字来决定信号存储时刻。

3)通过示波器李沙育图形显示功能进行8路逻辑信号的显示,且显示时触发位置可调(即触发时刻位于屏幕中的位置,默认为最左边)。

4)通过精确控制两路D/A转换电路,输出两路模拟信号至示波器的X、Y通道,对示波器屏幕进行快速有序扫描,利用示波器的余晖效应实现8路数字逻辑信号的显示;

5)具有手动光标功能,可通过按键调节光标位置,并通过LED灯将光标所对应的8路信号的状态显示出来。

6)具有显示切换功能,可以控制屏幕显示一个或两个周期波形。

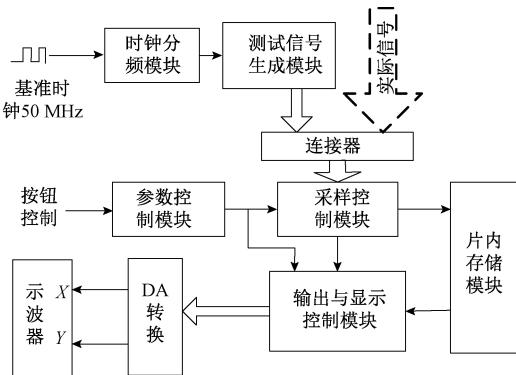

综合上述设计需求,确定了总体设计方案,如图1所示<sup>[6]</sup>。

图1 总体方案功能模块结构

**时钟分频模块:**由于标准测试信号位宽为  $10 \mu s$ , 该模块将晶振输入的  $50 \text{ MHz}$  信号转换为  $100 \text{ kHz}$ , 作为信号生成模块中的移位时钟输入。

**信号生成模块:**按上述要求产生8路数字信号,作为该装置的标准测试信号。

**按钮控制与参数控制模块:**将人机交互中的按钮输入转换为控制指令,主要包括触发字设置、触发位置设置、光标位置设置、采样控制、显示切换。具体对应关系如表1所示。

表1 按钮控制指令对应表

| 按/旋钮 | 功能        | 说明        |

|------|-----------|-----------|

| Key1 | 触发字高位控制   | 下降沿加1     |

| Key2 | 触发字低位控制   | 下降沿加1     |

| Key3 | 触发位置控制    | 居左、中、右三选一 |

| Key4 | 采样控制      | 下降沿有效     |

| Key5 | 显示切换      | 下降沿有效     |

| 旋钮   | 顺时针转动光标位置 |           |

|      | 右移,反之左移   |           |

**采样控制模块:**完成8路输入信号的采集控制,根据参数控制模块提供的参数对数据进行存储,存储完毕时告知输出与显示控制模块<sup>[7]</sup>。

**输出与显示控制模块:**在采样控制模块报告采样存储结束时,根据参数控制模块提供的参数对片内存储模块进行访问,并根据示波器李沙育图形显示原理对数据进行转换,向D/A转换电路提供数据。

## 2 硬件电路设计

系统基于FPGA设计,根据总体方案模块划分,硬件电路主要包括:FPGA最小系统板、双通道D/A转换电路、按/旋钮输入电路、LED显示电路等<sup>[8]</sup>。

**双通道DA转换:**基于8 bit高速DA芯片AD9708设计,配合滤波电路、幅度调节电路,能够输出  $10 \text{ Vpp}$  的模拟信号。

**按/旋钮输入电路:**按钮采用2脚微动开关,一端接地,另一端通过上拉电阻接FPGA;旋钮基于电位器和串行AD芯片TLC549设计,当电位器电阻最小时,TLC549向FPGA输出8 bit串行数据  $00H$ ,当电阻最大时,输出  $FFH$ 。

## 3 关键逻辑模块设计

### 3.1 参数控制模块设计

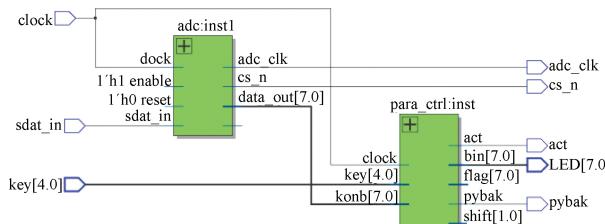

该逻辑模块主要由串行A/D数据读取与综合参数生成两部分组成,如图2所示。

图2 参数控制模块逻辑图

adc模块完成对外部串行AD转换芯片TLC549的读写控制,其中adc\_clk接TLC549的I/O时钟,频率设置为  $100 \text{ kHz}$ ;cs\_n接TLC549片选控制,sdat\_in为TLC549串行数据输入;data\_out为8位串并转换后的8 bit有效数据,作为屏幕显示时的光标位置参数。para\_ctrl模块中输入总线key连接外部5个微动开关,模块内部自带消陡程序用于检测下降沿;控制线act上升沿时表示发出开始采样指令;数据总线bin为8 bit触发字,数据总线flag为屏幕光标位置;控制线pybak输出一键切换控制指令,高电平时屏幕显示一个采样周期波形,低电平时同时显示两个采样周期波形;数据总线shift输出触发位置偏移指令,00和11时波形触发位置位于屏幕左侧,01居中,10居右。clock接晶振  $50 \text{ MHz}$  时钟输入<sup>[9]</sup>。

### 3.2 采样控制模块设计

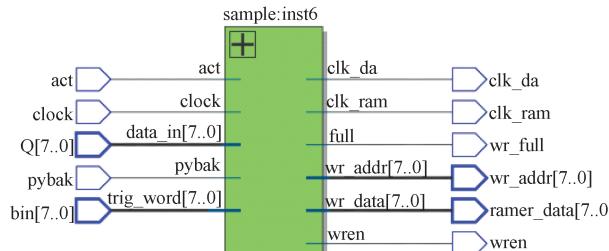

逻辑模块集成效果如图 3 所示。输入信号/控制线 act、pybak、bin 分别连接参数控制模块中对应的输出信号/控制线;输入数据总线 Q 为输入引脚读入的 8 路数字逻辑信号;clk\_ram 接片上存储器访问时钟,full 为存储器写满标志,高电平有效;wren 接片上存储器写使能控制线;wr\_addr、wr\_data 分别接片上 RAM 地址线和数据线。

图 3 采样控制模块

标准待测脉冲串信号位宽  $10 \mu s$ , 周期  $80 \mu s$ , 输入模拟信号采样读入的时钟设置为  $200 \text{ kHz}$ , RAM 存储时钟默认为  $3.2 \text{ MB}$ , 即对输入引脚读入的数字脉冲串每个位状态采集 32 个点, 每次采集产生一个字节的数据, 最高位为第 8 通道脉冲串状态, 最低位为第 1 通道脉冲串状态。片内 RAM 容量为  $8 \text{ bit} \times 256$ , 恰好采集 1 个脉冲串的 8 个状态<sup>[10]</sup>。

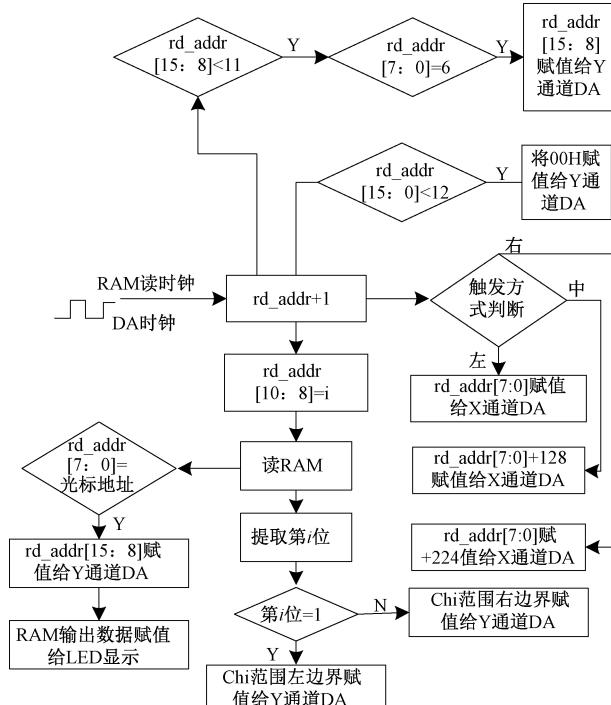

### 3.3 输出与显示控制模块设计

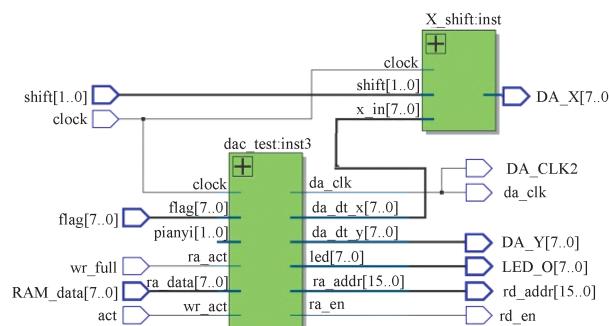

逻辑模块主要由输出数据生成与 X 通道偏移两部分逻辑构成, 如图 4 所示。

图 4 输出与显示控制模块逻辑图

数据/控制(总)线 shift、flag、wrfull、act 分别连接上述两个模块同名线路;RAM\_data 接片内存储器读输出总线,rd\_en 接片内存储器读使能;LED\_O 为 3.1 节所述光标位置所对应的 8 路逻辑信号的逻辑状态;da\_clk、DA\_CLK2、DA\_Y、DA\_X 为两路 DA 输出;X\_shift 模块根据 3.1 节所述 shift 提供的触发位置偏移指令对 X 通道 DA 数据进行偏移控制, 偏移量分别为 0(左侧触发)、128(中间触发)、223(右侧触发)。

#### 1) 内存读取控制逻辑

图 4 中 rd\_addr[7:0] 为片内存储器读地址, rd\_addr

[10:8] 用于指示需要读取的位地址。具体逻辑关系如表 2 所示。此外, rd\_addr[15:8] 用于光标的显示控制。

表 2 RAM 位读取控制线对应关系

| 地址线 | rd_addr<br>[7:0] | rd_addr<br>[10:8] |   |   |   |   |   |   |   |

|-----|------------------|-------------------|---|---|---|---|---|---|---|

|     |                  | 0~255             | 7 | 6 | 5 | 4 | 3 | 2 | 1 |

| 地址  |                  | 内容                |   |   |   |   |   |   |   |

| RAM | 0                | 0                 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

|     | 1                | 0                 | 0 | 0 | 0 | 0 | 1 | 0 | 1 |

|     | ...              | .                 | . | . | . | . | . | . | . |

|     | 254              | 1                 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

|     | 255              | 1                 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

采集到的 8 路数字信号, 由于片内 RAM 不具备位操作功能, 每次读取的数据为 rd\_addr[7:0] 所选中的 1 个存储单元的 8 bit 数据, 读取第一通道的存储数据时( $rd\_addr[10:8]=0$ ), 需要将 RAM 的整个存储空间(256 Byte)访问一遍, 并提取出最低位, 读取其他 7 个通道存储数据以此类推。因此, 要实现对 8 通道存储数据的读取需要对 RA\_M 读取  $8 \times 256$  次, 地址线 rd\_addr[10:8] 用于指示当前读取通道数并作为位提取逻辑的判断条件<sup>[11]</sup>。

#### 2) 示波器 8 通道显示逻辑

要将  $8 \times 256$  bit 存储单元的数据通过示波器屏幕进行 8 路数字逻辑信号显示, 需要用到示波器的 X-Y 显示模式, 即李沙育图形显示。本设计通过两路 DA 输出驱动示波器 X、Y 通道, 在示波器屏幕开辟一个分辨率为  $256 \times 256$  的矩形区域, 因为总共有 8 个通道, 所以垂直部分分为 8 行, 每行 32 个像素点高度, 波形显示范围为后 20 个像素点, 剩下 12 个像素点作为各通道的隔离部分; 其中第 1 通道的前 12 像素点作为触发标志“T”的显示。各通道的显示区域范围如表 3 所示, 0 对应 Y 通道输入模拟量 5 V, 255 对应 -5 V。

表 3 各通道显示区域范围

| 通道 | CH0     | CH1     | CH2     | CH3     |

|----|---------|---------|---------|---------|

| 范围 | 12~31   | 44~63   | 76~95   | 108~127 |

| 通道 | CH4     | CH5     | CH6     | CH7     |

| 范围 | 140~159 | 173~192 | 205~224 | 236~255 |

水平部分最左边对应 D/A 输出为 0, 最右边对应输出为 255, 对应的模拟信号分别为 -5 V 和 5 V。以显示第 1 通道为例, 显示控制逻辑如下<sup>[12]</sup>:

上述逻辑利用 FPGA 行为建模方式设计, 在 RAM 读时钟的控制下并发执行。

#### (1) 8 路逻辑量显示

rd\_addr 在 RAM 读时钟的驱动下进行累加操作, 逻辑块根据 rd\_addr[10:8] 的取值  $i$ , 对 RAM 输出进行位提取,

若为1,则给D/A模块Y通道赋值表2中的Chi左边界,反之赋值为右边界。同时将根据触发方式修正后的rd\_addr[7:0]赋值给X通道,用于确定波形显示的具体位置。流程如图5所示。

图5 显示控制逻辑图

### (2) 触发位置

rd\_addr[15:0]作为 $256 \times 256$ 个像素点的唯一标识,rd\_addr[15:0]等于0对应左上角像素点,rd\_addr[15:0]等于127对应右上角像素点。据此,触发标志“T”在默认显示模式为左边触发的条件下,应该在左上角 $12 \times 12$ 的像素方格内显示,即rd\_addr[15:0]等于0~11时画横线(Y通道模拟量0 V),rd\_addr[15:8]小于11且rd\_addr[7:0]等于6时画竖线(Y通道模拟量从0 V线性增加)。

### (3) 手动光标显示

由于光标显示需要在示波器屏幕上显示一条竖直亮线,即,当X轴输入rd\_addr[7:0]等于光标位置参数时,对应的Y轴输入涵盖了0~255的整个扫描区间。而rd\_addr[7:0]对应的RAM单元存储的8bit数据即为屏幕上光标所对应的8路逻辑信号的取值。

### (4) 扫描时间分析

RAM读时钟同时作为2通道D/A时钟,频率设置为25 MHz,则扫描显示1组8通道逻辑信号需要时间为 $1/25 \times 8 \times 256 \mu\text{s}$ ,即 $81 \mu\text{s}$ ;而扫描显示1根光标的时间为 $1/25 \times 256 \times 256 \mu\text{s}$ ,即2.621 ms;因此光标每完成一帧扫描显示,8路逻辑信号会完成32帧的显示,图像刷新频率均大于人眼分辨率24帧/s,可以达到8路同时显示的效果。

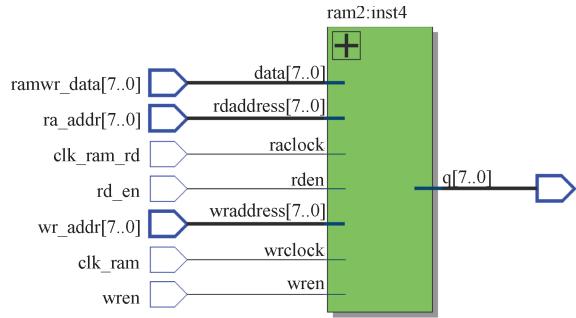

### 3.4 片内存储模块设计

片内存储模块采用8 bit $\times$ 256双口RAM实现,采用读/写双时钟设计,设置读/写使能端,功能模块如图6所示。其中ramwr\_data对应8位写数据线,ra\_addr对应8位读地址线,clk\_ram\_rd对应读时钟,rd\_en对应读使能,wr\_addr对应写地址,clk\_ram对应写时钟,wren对应写使能,q为读数据输出端。

图6 片上RAM接口逻辑图

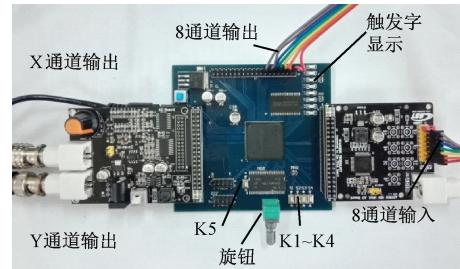

### 4 系统测试

根据系统方案设计,搭建了硬件验证系统,如图7所示。其中“8通道输出”为8路循环移位信号作为标准测试信号。

图7 系统测试平台实物图

为了验证触发显示,分别设置不同的触发字和触发位置按。照表1所示功能对参数进行设置,并观察显示效果:

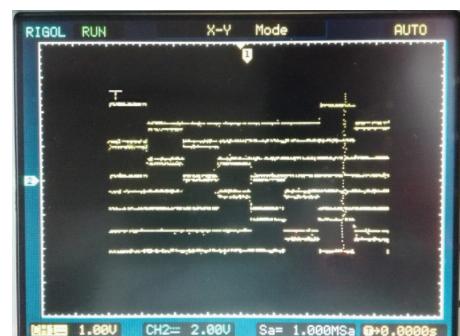

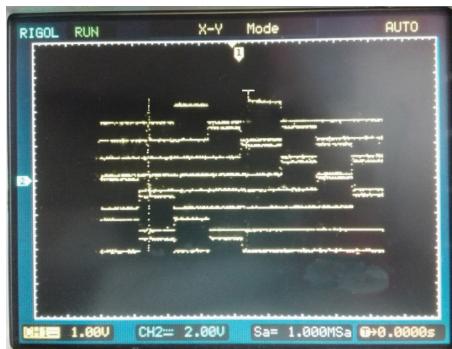

1) 触发字为00000101,触发位置为左边触发,测试结果如图8所示。其中竖直的点线为旋钮控制下的光标。

图8 左边触发显示效果

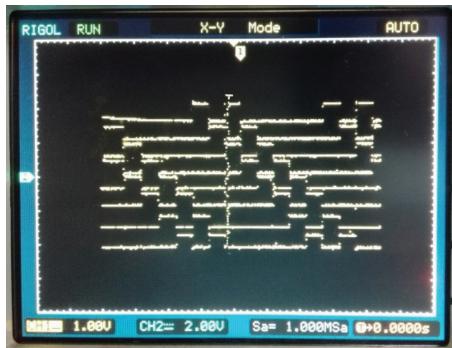

2) 触发字为 00000101, 触发位置为中间触发, 测试结果如图 9 所示。

图 9 中间触发显示效果

3) 一键切换显示两个周期, 测试结果如图 10 所示。

图 10 双周期显示效果

测试表明, 设计方案能够实现预定效果; 存在的问题主要是个别显示波形和手动光标显示不能够做到绝对的“横平竖直”, 原因主要是 D/A 转换输出存在一定的漂移, 且 D/A 转换输出做不到绝对的线性。

## 5 结 论

数字逻辑分析仪作为数字电路逻辑设计实验的测试工具, 同时也可以作为数字电路与可编程逻辑设计实践教学方面的典型案例。通过综合运用数字电路与可编程逻辑相关知识, 立足实验室现有硬件和设备条件, 设计开发 8 通道数字信号时序分析装置, 即拓展了实验教学内容, 将原来实验中的辅助测量工具示波器作为设计内容的一个显示模块进行应用, 有利于激发学生创造热情<sup>[13]</sup>。通过在实验室不断的应用自制设备和电路模块, 或者对现有货架产品进行改造升级和功能拓展, 能够增强实验教学的个性化和吸引力, 浓厚创新氛围, 丰富实验内涵, 在今后的实验教学研究

中, 将继续集思广益, 以实验室建设的个性化和创造性带动实验教学的特色化和吸引力<sup>[14-15]</sup>。

## 参考文献

- [1] 党一闻.先进的分布式飞机线缆测试系统设计[J].航空制造技术, 2016(4): 105-109.

- [2] 叶朝辉, 华成英, 张利伟, 等.基于 FPGA 的 SOPC 电子系统设计实验研究[J].实验技术与管理, 2018, 35(3): 161-164.

- [3] 许可行, 吴帅, 周晓华.基于嵌入式系统的简易逻辑分析仪设计[J].国外电子测量技术, 2017, 36(7): 77-81.

- [4] 刘俊杰, 师剑军, 周瑞钊, 等.便携式逻辑分析仪硬件平台设计[J].火力与指挥控制, 2017, 42(3): 132-136.

- [5] 王墨林, 戚昊琛, 鲁迎春, 等.FPGA 课程创新型实验教学体系的实践[J].实验科学与技术, 2018, 16(4): 134-139, 147.

- [6] 张松, 李筠.FPGA 的模块化设计方法[J].电子测量与仪器学报, 2014, 28(5): 560-565.

- [7] 张淑梅.基于 ARM+FPGA 的高精度数据采集系统设计[J].国外电子测量技术, 2014, 33(11): 62-65.

- [8] 谈良, 纪凌.基于 FPGA 的多通道数据采集系统设计与实现[J].电子测量技术, 2018, 41(5): 57-63.

- [9] 厉俊男, 杨翔瑞, 孙志刚.DrawerPipe: 基于 FPGA 的可重构分组处理流水线模型[J].计算机研究与发展, 2018, 55(4): 717-728.

- [10] 李进方, 许爱强.基于 FPGA 的脉冲信号参数测量[J].电子测量技术, 2018, 41(2): 119-123.

- [11] 石瑞.高精度数字逻辑分析设备的研究[J].机械设计与制造工程, 2014, 43(5): 51-53.

- [12] 苏阳, 赵英潇, 黄睿, 等.FPGA 的多路数据并行录取和时序资源优化[J].单片机与嵌入式系统应用, 2017, 17(7): 19-22.

- [13] 葛桂萍, 肖铁军, 陈才扣, 等.基于 FPGA 的“计算机组成原理”实践教学的改革[J].实验技术与管理, 2018, 35(4): 12-15.

- [14] 邢东洋.传统集成电路与 FPGA 相结合的数字电子技术综合实验平台的研制[J].科学技术创新, 2018(6): 173-174.

- [15] 陈彦, 金燕华, 王茜.高校数字逻辑设计课程考核模式的问卷调查与分析[J].教育教学论坛, 2015(15): 51-52.

## 作者简介

汪兴海, 硕士、讲师, 主要研究方向为信号检测与信息处理、嵌入式系统设计。

E-mail: marshallplan@126.com