# 基于 FPGA 的多功能飞行测试系统设计

薛伟何<sup>1</sup> 张会新<sup>1,2</sup> 刘利生<sup>2</sup>

(1. 中北大学微米纳米技术研究中心 太原 030051; 2. 山西中北测控科技有限公司 太原 030051)

**摘要:** 针对现有飞行器测试系统存在的外源数据兼容性差、现场配置迭代效率低、数据传输可靠性有限等问题,提出一种基于多总线协同架构的新型测试系统。系统以 FPGA 作为主控处理器,支持 RS422、1553B 和以太网 3 种总线接口数据的接收、融合与传输,利用千兆以太网通信模块设计实现配置指令的实时下发与程序存储器的在线更新,并为以太网通信模块设计支持处理 UDT 协议的功能模块。实验及仿真结果表明:系统支持采集并存储 RS422 数据和 1553B 总线数据,实现多总线数据协同记录功能;在线升级功支持在  $-40^{\circ}\text{C} \sim 100^{\circ}\text{C}$  温度环境实现,自检显示升级完成耗时均低于 1 s;通过监测实验过程数据传输情况,使用 UDT 协议传输数据时,平均传输速率可达到 454 Mbit/s,相比于 UDP 协议未出现数据丢失现象,显著提升数据传输可靠性。

**关键词:** 测试系统;多总线;在线升级;UDT;FPGA

中图分类号: TN06 文献标识码: A 国家标准学科分类代码: 510.1010

## Design of FPGA-based multifunctional flight test system

Xue Weihe<sup>1</sup> Zhang Huixin<sup>1,2</sup> Liu Lisheng<sup>2</sup>

(1. Micro-Nano Technology Research Center, North University of China, Taiyuan 030051, China;

2. Shanxi Zhongbei Measurement and Control Technology Co., Ltd., Taiyuan 030051, China)

**Abstract:** Aiming at the problems of poor compatibility with external data sources, low efficiency in field configuration iteration, and limited reliability of data transmission in existing aircraft test systems, an intelligent test system based on a multi-bus collaborative architecture is proposed. The system employs an FPGA as the core processor, supporting the reception, fusion, and transmission of data through three bus interfaces: RS422, 1553B, and Ethernet. A gigabit Ethernet communication module is designed to enable real-time configuration command delivery and online updates of program memory, along with a functional module for processing the UDT protocol. Experimental and simulation results demonstrate that the system can collect and store RS422 data and 1553B bus data, achieving multi-bus data collaborative recording. The online upgrade function operates successfully in temperature environments of  $-40^{\circ}\text{C} \sim 100^{\circ}\text{C}$ , with self-tests showing upgrade completion times consistently under 1 second. In simulated data input scenarios, using the UDT protocol achieves a data packet delivery accuracy rate of 99.8%, a significant improvement over the 87.5% rate of the UDP protocol, thereby enhancing data transmission reliability.

**Keywords:** test system; multi-mode; online upgrade; UDT; FPGA

## 0 引言

近年来,我国空军高精尖装备陆续列装,新式武器层出不穷,建设空军强国成绩斐然,这些成就依托于高精度飞行器的可靠保障。动态测试作为飞行器研制关键环节,通过采集参数、分析数据,实现排查故障与性能优化。作为测试核心,数据测试记录装置“黑匣子”应不断升级系统架构,优化性能指标,以应对复杂多样的数据采集场景以及严苛的时间、空间要求。

国外航空测试实验力学参数的测试能力和水平已达到成熟的应用状态,从 20 世纪 50 年代开始,欧美各国开始持续开展了发动机状态监测和故障诊断技术的研究。瑞士 Vibro-Meter 公司的通用发动机振动监测仪(UEVM)已获得了商业应用,支持实时监测整机振动强度、频率,同时实现远程监测及平衡调整<sup>[1]</sup>。CALCULEX 公司研制了 6601RIPR 型数据记录器,支持 MIL-STD-1553、Ethernet 以及光纤等接口,能够在复杂恶劣环境下使用,多种总线数据架构保证其数据多元性,记录容量高达 500 GB<sup>[2]</sup>。

国内对航空测试系统的研究最早可以追溯到 20 世纪 60 年代初,更多偏向于单总线系统中的功能升级。文丰等<sup>[3]</sup>的研究通过以太网接口实现 FPGA 程序的远程更新,简化了升级过程,但在传输速率和可靠性方面尚有提升空间。谈良等<sup>[4]</sup>开发了类似航空领域的多通道测控系统,使用 FPGA 平台可以对多通道音频和大时段雷达信号信号进行实时采集显示存储,提供了一种解决发动机测试中待测点数量多和采样率高的关键思路。韩子舟等<sup>[5]</sup>通过 1553B(military standard 1553B)总线进行 FPGA 在线升级,但 1553B 总线的数据传输速率较低,通常在 1 Mbps 左右,同时需要专用总线控制器以及接口电路,系统设计难度较大。党瑞阳等<sup>[6]</sup>提出了基于 FPGA 的自定义 DR\_UDP 协议千兆以太网远程在线升级技术,实现了千兆以太网高速通信,但未应用于独立测试系统,难以独立发挥在线升级在复杂测试环境中的实际应用价值。

基于国内外研究现状以及实际应用需求,本文提出一种基于 FPGA 的可在线升级的多总线飞行测试系统,系统集成 1553B、RS422 和以太网 3 种总线硬件配套电路,主控模块支持 IEEE 1588 精密时间协议,保证系统模块间时间基准同步精度,并设计数据优先级传输权重分配算法,应对实际测试时的不同总线时序和带宽要求,满足目前航空测试领域对于多源数据采集的需求;并参考 UDP 协议设计 UDT 协议传输模块,提供了一种高可靠性数据传输备用方案。

## 1 系统整体方案设计

系统主要实现对飞行器数据的采集、监测与存储,采用模块化架构实现多协议数据融合处理:构建多通道 RS422 全双工通信链路,集成高速 1553B 总线模块,采用时间精密协议与多总线数据权重分配算法,开发数据封装协议,完成数据融合编帧与存储;拓展基础以太网功能模块,支持 FPGA 固件程序在线升级功能,保证系统无间断式更新配置文件;设计基于以太网硬件模块的 UDT 协议解析模块,为数据传输提供高可靠性备用方案。

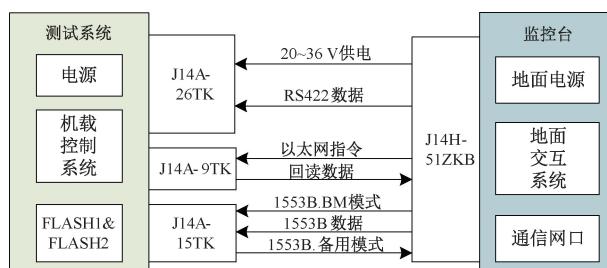

工作状态下,测试系统将配合监控台实现对飞行器数据的记录与监测。监控台为整体系统提供供电,输入数据以及指令。测试系统与监控台设备组成及连接关系如图 1 所示。

图 1 系统工作示意图

Fig. 1 Working schematic diagram of the system

设计思路中,监控台可用于飞行器的地面模拟飞行测试以及回读测试数据,测试系统实现对测试数据的接收与存储,由主控模块、存储模块、电源模块组成。测试系统供电来源为监控台 28 V 电源,系统内部通过电源模块二次转换后进行供电。本文将对测试系统的主要设计进行描述与验证,下文简称系统。

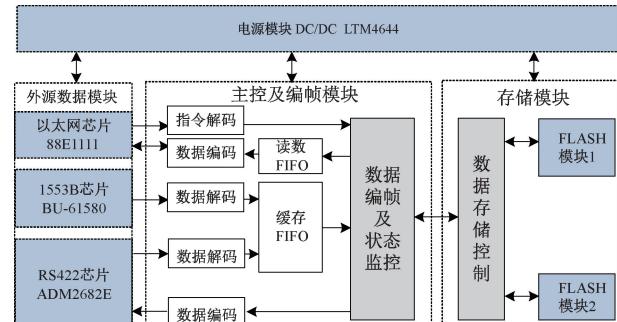

## 2 系统硬件设计

系统硬件电路主要包括 3 个模块,分别是电源模块、主控模块和存储模块。基于系统需求指标,选用 Xilinx 公司 XC7K325T-2FFG676I 型号作为系统主控 FPGA 芯片。系统总体组成及连接如图 2 所示,由电源模块、外源数据模块、主控及编帧模块以及存储模块组成,重点模块器件选型以及电路设计将在此章节中详细介绍。

图 2 系统硬件设计示意图

Fig. 2 Schematic diagram of system hardware design

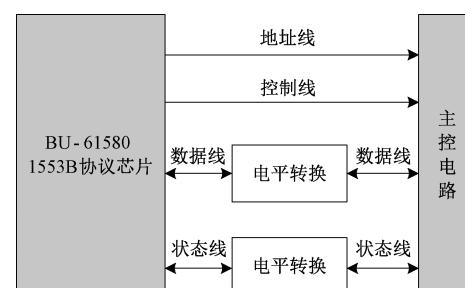

### 2.1 1553B 总线接口模块

系统选用 BU-61580 芯片作为 1553B 接口。1553B 总线协议芯片是实现 1553B 总线通信的核心,该协议芯片是一款双路 1553B 总线收发模块,内部集成了数字协议控制电路,具有完整的 1553B 远程终端 RT、总线控制器 BC 和监控终端 BM 功能<sup>[7]</sup>。BU-61580 芯片连接示意如图 3 所示。

图 3 BU-61580 接口图

Fig. 3 Interface diagram of BU-61580

1553B 总线接口电路采用协议芯片与 FPGA 协同工作的架构,其包含隔离变压器和电平转换芯片等关键组件。该设计针对总线通常所处的强电磁干扰、振动冲击等恶劣工作环境,采用变压器耦合方式实现物理连接,既确保了故障隔离能力,又显著提升了数据传输稳定性<sup>[8]</sup>。

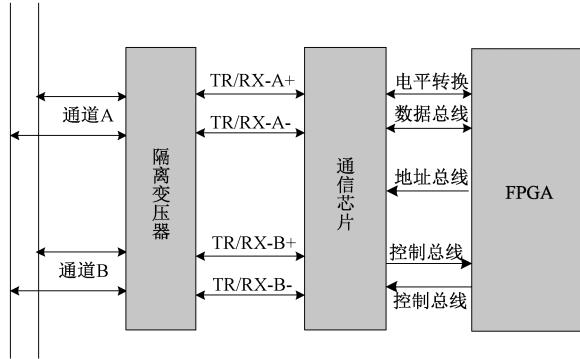

在实现过程中,协议芯片作为总线监控器 BM 承担核心通信功能,负责接收系统控制数据;FPGA 负责协议芯片的配置及总线接口设计;电平转换芯片负责 FPGA 与协议芯片间的电平匹配问题;隔离变压器则实现接口电路与 1553B 总线系统之间的电气隔离,设计示意如图 4 所示。架构设计既满足了恶劣环境下的通信需求,又通过各模块的协同工作确保了整体系统的稳定性。

## 1553B总线

图 4 1553B 整体示意图

Fig. 4 Overall diagram of the 1553E

## 2.2 RS422 接口设计

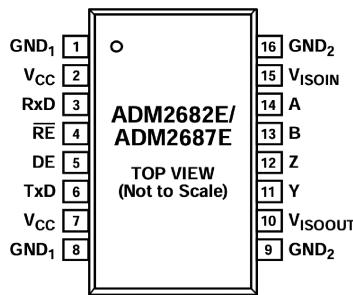

RS422 接口芯片选用内部集成隔离电路的隔离收发器 ADM2682E, 如图 5 所示。该芯片采用 3.3 V 工作电压供电, 集成高电压 ESD 保护, 支持 16 Mbps 数据速率传输<sup>[9]</sup>。芯片 Y、Z 引脚对应隔离发送器差分信号输出端, 为防止传输过程中线路发生短路, 设计串接限流电阻作为缓冲, 选用 51 Ω 电阻作为保护电阻, 防止过大的瞬时浪涌电压导致短路; 芯片 A、B 引脚是对应的隔离接收器差分输入端, 为了延长传输距离, 保证差分信号传输的稳定性, 在 A、B 引脚将分别上拉和下拉 1 kΩ 电阻, 同时为了优化信号的传输质量, 减小弹地噪声对芯片工作的影响, 在 A、B 之间引入终端匹配电阻。此外, 电源引脚和地引脚间分别并联一组电容, 从而降低噪声干扰、抑制纹波。

图 5 ADM2682E 引脚图

Fig. 5 Pinout diagram of ADM2682E

## 2.3 以太网接口设计

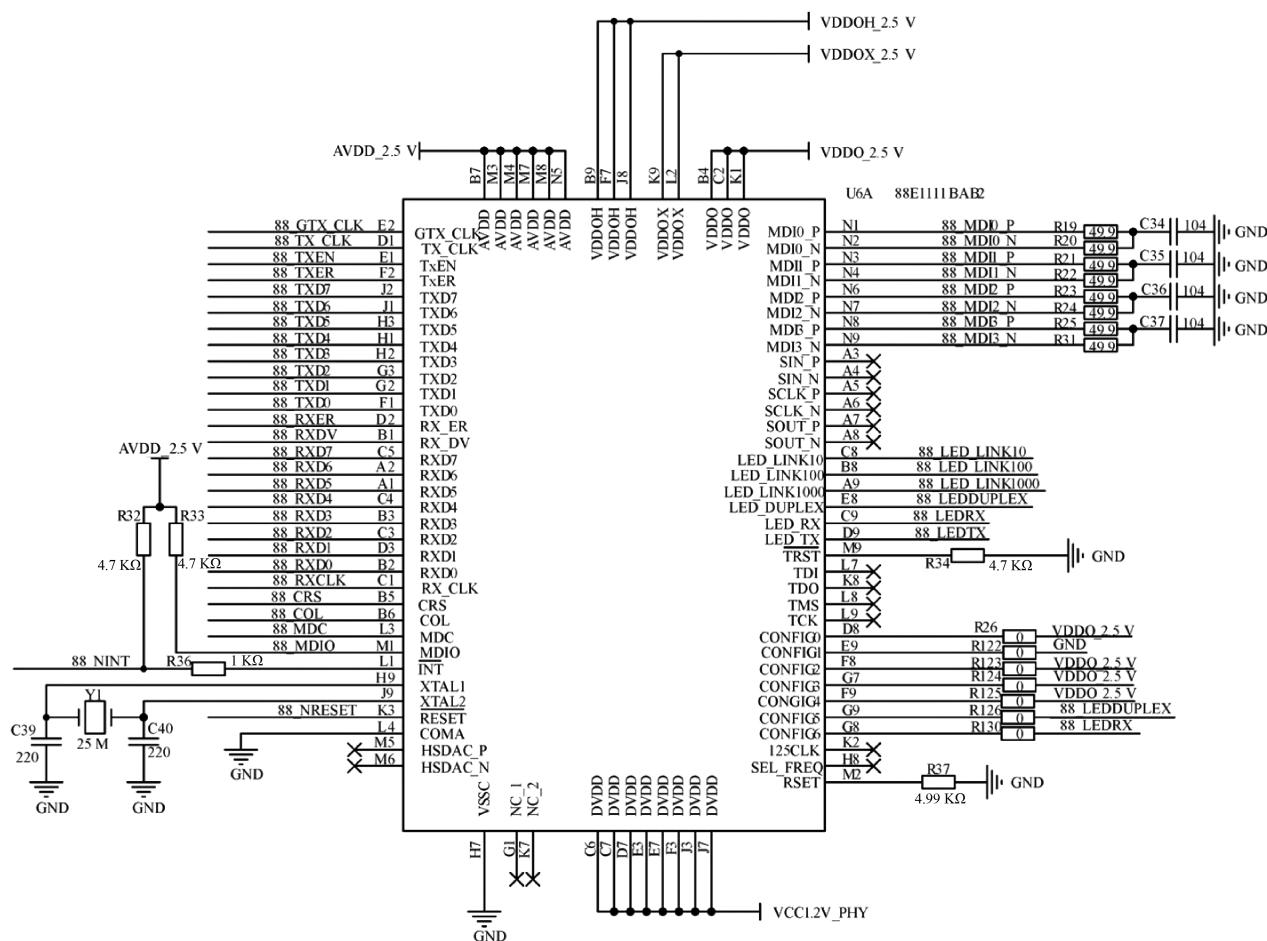

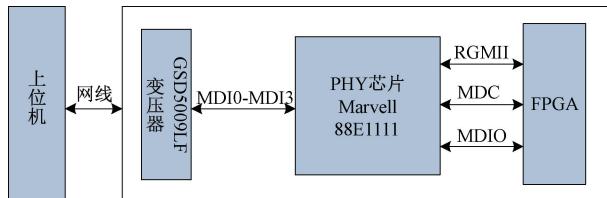

系统选用 Marvell 公司独立物理层 (physical layer, PHY) 芯片 88E111 实现物理层的收发, 支持介质访问控制

(medium access control, MAC)层功能,该款芯片具有连接硬件管脚配置和上电后寄存器配置两种配置方式<sup>[10]</sup>。设计中可通过硬件管脚进行外部高低电平的配置,实现芯片相应的工作模式。88E1111 的速率匹配可以自协商实现,支持多种接口与 FPGA 连接,包括 GMII、RGMII 和 SGMII 等,本系统选用 GMII 接口。以太网芯片配置电路图如图 6 所示。

系统选用的隔离变压器型号为 GST5009LF, 该变压器专门设计应用于千兆以太网全双工系统, 在降低共模发射和实现高效的信号隔离的同时, 确保电缆接口的稳定性和可靠性<sup>[11]</sup>。模块工作流程如图 7 所示。

### 3 系统关键逻辑

### 3.1 系统整体工作流程

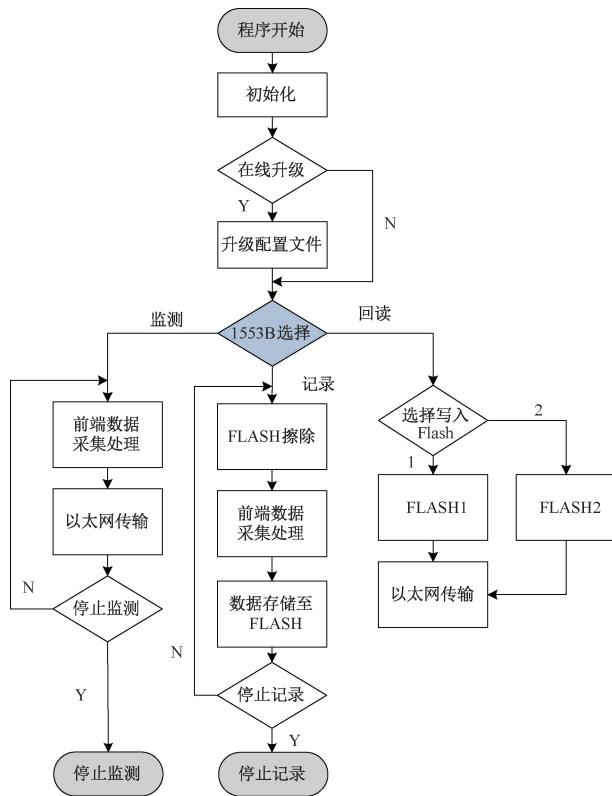

系统主程序可实现监测、回读和记录3种功能，工作逻辑流程如图8所示。上电复位后，FPGA先对系统初始化，上位机根据不同模式通过以太网发出相应指令，存储器主控芯片通过配置不同的寄存器实现系统不同功能。系统支持3种工作模式：在记录模式下，首先清空FLASH存储器中的残留数据，随后进行对前端传感器数据的调理存储，当数据达到触发阈值时，同步存储至FLASH1和FLASH2，直至接收到停止记录指令；在监测模式下，实时采集的数据通过千兆以太网传输至监控台实现监控，直至收到停止监测指令；在回读模式下，可选择读取FLASH1或FLASH2中存储的数据并回传至上位机。过程中所有指令均采用统一的数据格式，以便于设备调试和潜在的试后读数需求，其他关键功能描述详见下文。

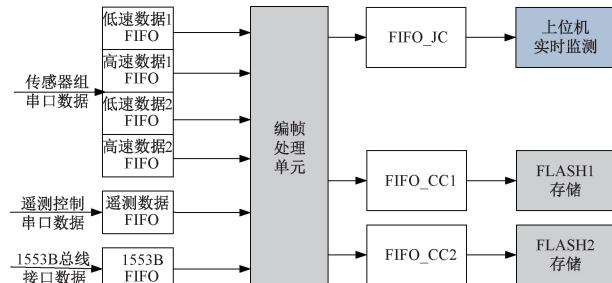

### 3.2 多路数据融合编帧技术

系统需要接收并存储多路数据,为了确保不同接口的数据完整有序地存入 FLASH,并支持后续数据回读分析,需对数据进行编帧处理。系统主控模块添加 Vivado 软件精密时间协议 IP 核 Ethernet Subsystem,其支持 IEEE 1588 协议实现对系统全模块提供微秒级别时间同步精度,模块通过主控主时钟和模块从时钟之间互传包含时间戳的时间报文,计算报文互传流程间的时间延迟后,对子模块从时钟产生反向偏置补偿,从而实现高精度同步。在总线数据处理模块中,编帧前的各缓存 FIFO 按照统一设定时长独立存储数据,由于不同总线带宽不同,控制模块增加跨优先级算法语句,按照不同权重对 3 种总线数据进行编帧处理,优先级依次为以太网,1553B 和 RS422。以太网数据主要为指令信息,因此在数据编帧中较少参与。具体编帧流程如下:首先,利用 FIFO 缓存对不同接口的数据进行暂存,随后将数据送入编帧处理单元。处理后的数据分为三路:其中两路作为备份存储至 FLASH,另一路则通过以太网传输至上位机进行实时监测。存储环节采用逐帧存储策略,监测数据则基于航空电子测试系统周期性和稳定性特征,采取间隔固定帧上传原则,以平衡存储完整性与传输效

图 6 88E1111 电路图

Fig. 6 Circuit diagram of 88E1111

图 7 以太网模块示意图

Fig. 7 Schematic diagram of Ethernet module

率。编帧整体示意如图 9 所示。

系统 1553B 总线数据传输速率接近 1 Mbps, RS422 总线数据传输速率为 1 845 Kbps 和 500 Kbps 两种。模块设置融合帧字长 25 000 字节, 存储速率为每秒 50 帧, 单字节长 8 位, 故编帧后数据存储速率为 10 Mbps。由于 1553B 芯片在监测模式下支持监测传输速率最大约为 1 Mbps, 因此监测数据间隔取每 10 帧传输一次。

融合后各总线数据仍保留部分自有数据结构,在每行数据传输完成后附加特定的控制字段,以便试后上位机拆分后数据识别。以 1553B 总线数据为例,其帧结构选用 50FC 作为帧头,随后为 2 字节的块状态字表示,之后依次

为2字节系统时间戳信息,2字节帧计数,2字节1553B配置信息命令字,18字节自用备份信息以及之后的采集系统数据。对于传输过程中的无效数据位,统一用0x00进行填充。

### 3.3 FLASH 分区在线升级技术

FPGA 的多重配置 (MultiBoot) 功能支持远程动态更新比特流映像 (bitstream images)，可实现比特流文件实时切换。MultiBoot 作为在线升级的功能实现基础，本质是对可编程资源进行复用，根据需求加载不同的配置文件，从而实现多重配置。

MultiBoot 功能通过增强型内部配置访问端 (internal configuration access port enhanced 2, ICAPE2) 执行内部编程指令 IPROG 实现。当重配置开始时, IPROG 指令由 FPGA 内部的 ICAPE2 模块发出, 使 FPGA 从 FLASH 的指定地址开始读取配置文件, 地址由重载起始地址 WBSTAR 寄存器决定。在 IPROG 指令发出后, FPGA 首先发送同步字 AA995566, 然后向 WBSTAR 寄存器中写入下一个比特流文件起始地址 00000000, 最后发送 IPROG 命令 0000000F<sup>[12]</sup>。IPROG 常见指令序列如表 1 所示。

图8 系统工作流程示意

Fig. 8 Diagram of the system workflow

图9 多路数据融合示意图

Fig. 9 Schematic diagram of multi-source data fusion

表1 IPROG 指令队列

Table 1 IPROG command queue

| 配置数据       | 源码描述                    |

|------------|-------------------------|

| FFFFFFFFFF | 填充字(空操作,多对齐或延时)         |

| AA995566   | 同步字(用于比特流同步,标识配置开始)     |

| 20000000   | 类型1 NOOP(无操作指令,维持当前状态)  |

| 30020001   | 类型1写操作(向WBSTAR寄存器写入1个字) |

| 00000000   | 热启动起始地址(需替换为实际加载地址)     |

| 30008001   | 类型1写操作(向CMD寄存器写入1个字)    |

| 0000000F   | 类型1 NOOP(无操作指令,确保配置完成)  |

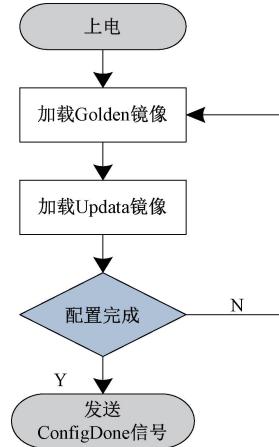

系统采用双镜像架构对FPGA配置程序进行存储与启动管理,将FLASH存储空间划分为两部分:起始地址

Address 0 用于存储作为出厂备份的“Golden 镜像”;后部地址 Address X 存储支持现场升级的“Update 镜像”。在线升级启动控制流程如图 10 所示。上电后首先加载 Golden 镜像,随后 ICAP 模块根据 WBSTAR 寄存器预设的跳转地址自动切换至 Update 镜像,待双镜像均配置完成后释放 ConfigDone 信号。当 Update 镜像校验失败时可自动回退至 Golden 镜像运行,其中 Address X 的取值可根据选用 FLASH 容量的阵势使用空间优化设定。

图10 MultiBoot 功能实现流程

Fig. 10 Implementation process of MultiBoot function

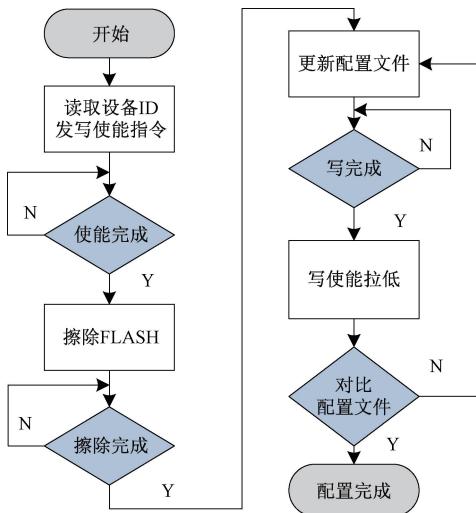

本系统在线更新实现流程如图 11 所示,FPGA 固件更新开始时,存储系统上电,上位机发送 FPGA 程序升级命令,FPGA 扫描并识别到设备 ID。完成识别后,通过状态存储器读取到写使能拉高,开始擦除 FLASH 指定地址数据,先擦除同步字,然后通过读取状态存储器的值检验是否完成擦除从而反馈上位机此时 FLASH 状态。当 FLASH 数据擦除完成后,FPGA 将接收的配置文件送入 FIFO 缓存,当 FIFO 不为空则将数据送入 FLASH,若判断到 FIFO 为 0 并连续等待 1 s 后 FIFO 依然为空时,判断更新结束,写使能拉低;写入 FLASH 数据时,先检验同步字,检测正确后先写入 FPGA 固件其他文件数据,最后再写入同步字。此时上位机软件从 FPGA 中读取下发的配置文件与原配置文件进行对比,若文件内容一致,表示配置成功,若不一致,设备则重新上电并再次更新。

### 3.4 自定义 UDT 协议处理功能

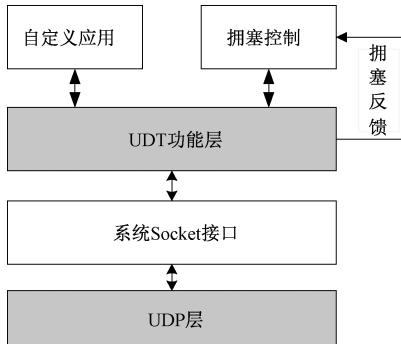

在航空测试数据传输环境中,TCP 协议由于拥塞控制过于保守导致带宽利用率低,速度受限;UDP 协议由于不支持握手机制与阻塞控制,其可靠性有限。UDT(UDP-based data transfer protocol)作为一种高性能的改进型协议,在用户空间(User Space)基于 UDP 协议实现,通过调用 UDP Socket API 函数实现数据传输,保障数据可靠传输,优化拥塞控制,并在功能上模拟传输层协议特性。

可靠性方面,UDT 采用接收端驱动的可靠性机制,通过固定间隔发送选择性确认包(SACK)实现数据确认,添

图 11 在线更新实现流程

Fig. 11 Update the implementation process online

加即时丢包检测,一旦发现数据包丢失立即向发送端反馈否定确认(NACK),这种设计显著提升了数据传输的可靠性<sup>[13]</sup>。拥塞控制方面,UDT 改进了传统 TCP 的拥塞控制算法,采用加性参数递减算法(DAIMD),该算法通过动态调整拥塞窗口增长参数,实现比传统 TCP 更精确的发送速率控制,在维持高吞吐量的同时避免了网络拥塞<sup>[14]</sup>。UDT 系统分层示意如图 12 所示。

图 12 UDT 系统分层示意

Fig. 12 Hierarchical diagram of the UDT system

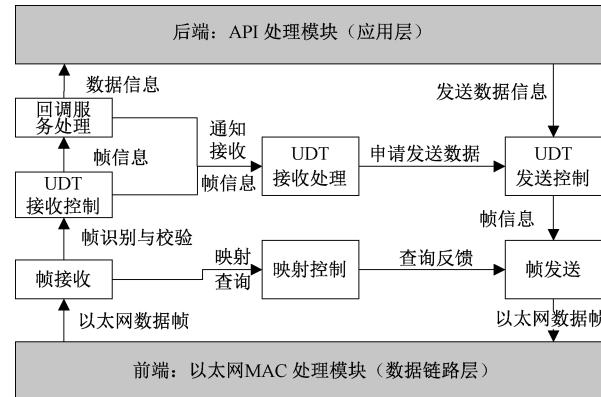

自定义 UDT 解析模块采用以太网通信,选择千兆网关接口(gigabit media independent interface, GMII)搭建数据链路层。模块使用 FPGA 将以太网 MAC 层接口以及通信协议包头封装为可配置 IP 核,数据经过 MAC 处理后进入 UDT 解析功能模块,继而对 UDT 数据开始解读。模块在通信处理链路中涵盖网络层和链路层,实现对 UDT 协议的数据解析。系统的 UDT 协议解析功能模块按工作流程分为 7 个子模块,按主体功能分为两种类别,一类为数据链路处理,一类为数据链路协调。数据链路处理功能分为数据接收与数据发送两种数据流向,分别对应数据信息在前端以太网 MAC 处理模块与后端 API 处理模块之间的收发。数据接收流向依次有帧接收,UDT 接收控制,回调服务处理

3 个模块,数据发送流向则为 UDT 发送控制,帧发送两个模块。数据链路协调功能由 UDT 接收处理,映射控制组成。自定义 UDT 解析模块工作流程如图 13 所示。

图 13 UDT 解析模块工作流程

Fig. 13 Workflow of the UDT parsing module

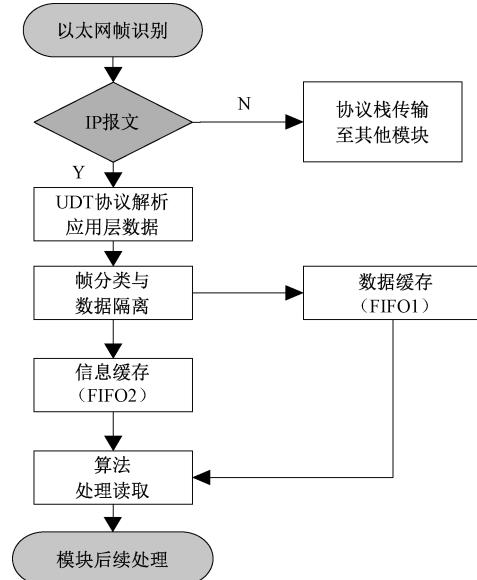

帧接收模块如图 14 所示,该模块可实现帧接收处理,帧解析与分类功能。模块首先根据以太网帧格式识别报文类型并提取五元组:若非 IP 报文或广播报文,则通过控制隔离逻辑转发至设备管理 CPU,不由本模块处理;若为 IP 报文,则进一步按照 UDT 协议解析应用层数据,提取帧类型(type)及操作信息。随后分离 UDT 数据帧的 payload 至数据 FIFO 队列,控制/命令信息写入信息 FIFO,供后续算法模块读取处理。

图 14 帧接收模块工作流程

Fig. 14 Workflow of the frame receiving module

UDT 接收处理模块内部采用分层协同架构:接收控制模块作为核心调度单元,根据报文类型触发差异化处理——握手报文提取版本号、UDP 头、IP 头等参数并更新流表;ACK/ACK2 报文计算 RTT 和窗口参数;NACK 报

文维护丢失序列;DATA 报文校验端口与协议后提取流 ID 等元数据。各子模块分工明确:数据包处理模块解析有效载荷,SACK/NACK 处理模块维护传输状态,握手响应模块生成连接确认包。定时器模块通过 RCTP(速率控制)、NAK(丢包检测)、EXP(重传)三类独立定时器依托多定时器协同机制实现闭环流量控制,RCTP 定时器通过周期自适应调整( $T=1/rate$ )直接控制发包周期,实现速率限制,保障阻塞控制,NAK 定时器以 4 倍 RTT 间隔主动探测丢包,触发重传以缓解拥塞。EXP 定时器则基于动态 RTO( $RTT+4 \times RTT_{var}$ )管理超时重传,确保重传及时,防止拥塞恶化。形成“报文解析→状态更新→定时反馈”的完整处理链。

接收 ACK 包时,模块触发拥塞控制管理。拥塞控制服务于发送端,其主要负责阻止过多的数据注入到网络,避免网络负载过大。滑动窗口用于反映探测网络拥塞程度,其初值为 1,每多收到 1 个 ACK 报文,窗口大小翻倍一次。本设计中,当发送端能接收到连续 3 个正确的 ACK 报文时,说明网络状况相对良好,则将滑动窗口阈值(ssthresh)设置为当前窗口值的 1/2,滑动窗口的大小设置为同 ssthresh 一致,然后开始执行拥塞避免算法,使拥塞窗口缓慢的线性增大。

接收 SACK 包与 NACK 包时,模块通过固定间隔发送 SACK 确认包和出现丢包时发送 NACK 确认丢包情况,对丢包情况产生反馈与抑制,提升可靠性。

UDT 报文类型和相关操作如表 2 所示。

表 2 UDT 报文类型和相关操作

Table 2 UDT message types and related operations

| UDT 报文类型 | 相关操作                                   |

|----------|----------------------------------------|

| 握手报文     | 提取序列号,UDT 版本号,最大流量窗口大小                 |

| ACK 报文   | 提取时间戳,序列号,socket-ID,最大报文长度,流量窗口大小,往返时间 |

| ACK2 报文  | 提取时间戳,序列号                              |

| SACK 报文  | 提取传输区间起始序号与结束序号,最后连续包的序号               |

| NACK 报文  | 处理丢失链数组                                |

除此之外,UDT 解析功能模块中,回调服务处理模块从 UDT 接收控制模块读取建链请求,构造报文发送给协处理器,分配流号后返回响应:成功则记录连接信息并计算传输参数返回 ACK;失败则触发 1 秒间隔的重传。通过流表管理和动态参数调整确保可靠连接。映射控制模块负责刷新应用流号与标识,并为应用流号与 UDT 唯一标识建立映射控制。UDT 接收模块与 UDT 发送模块实现对数据的解析与组装,后者最终通过帧发送模块重构 IP 头,MAC 头以及最终的数据封装。以上为自定义 UDT 协

议解析模块工作流程。

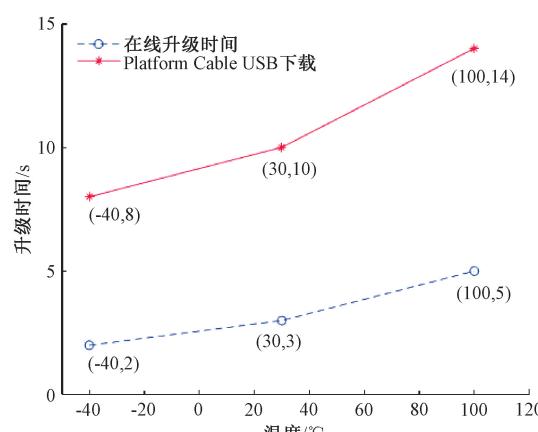

## 4 实验验证

测试系统数据验证环境如图 15 所示。测试系统实验数据验证思路如下:根据测试流程,单元测试后,对由总线数据回读数据进行拆分后的有效数据进行判读。经过实际的单元测试后,得到的判读结果会与设计进行比对,若符合则说明数据分析完毕并且正确;对于在线升级功能,将通过上位机控制在线升级功能前后的数据结构变化验证其在测试系统中的可行性,并在  $-40^{\circ}\text{C}$ 、 $30^{\circ}\text{C}$  和  $100^{\circ}\text{C}$  温度环境与传统 USB 配置方式耗时采取对比,验证其复杂环境可靠性以及实际应用便利性;自定义 UDT 协议模块将通过将测试实验中 UDT 协议传输的速率和丢包率与 UDP 协议对比,验证其可行性与传输可靠性。具体分析详见本节。

图 15 测试系统数据验证环境

Fig. 15 Test system data validation environment

### 4.1 总线数据验证

1553B 总线数据的监测需要先对 1553B 板卡进行配置,配置过程中依次发送指令字 083F,403F。根据数据编帧的内容可知,监测数据包回读数据的格式依次为帧头 50FC,块状态字,时间戳,帧计数数据,命令字以及之后的具体数据内容数据,数据使用 Hex Editor 软件解读,结果如图 16 所示。根据监测包数据回读结果可知,命令字与预先配置的相同,命令字中的终端地址与上位机状态字中终端地址相同。根据块状态字对应表,A 总线传输数据的结束标志字为 8 100,B 总线传输数据的结束标志字为 A100,与配置的通道相同。综上,1553B 数据回读与发送的相同,达到了监测数据的任务。

RS422 串口采集了 3 路高速组件路数据,由于读数软件显示数据旗下的限制,以第 1 路高速组件(传输速率 1 Mbps)为例,其数据帧结构开始为帧标识,其中传感器组件 1 帧标识为 55AA19。由于传输比特率较高,该路组件帧结构中无帧计数字节,直接在数据后接 1 字节的校验和,然后依次是 1 字节长时间戳计数和 6 字节长时间戳数据。回读结果如图 17 所示,分析可知回读数据与定义的帧结构相同,数据可靠。

### 4.2 在线升级功能验证

在线升级功能验证过程中,系统采用 FPGA 生成的数

1553BM接口.dat

| Offset(h) | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 0A | 0B | 0C | 0D | 0E | 0F |

|-----------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 00000000  | 50 | FC | 81 | 00 | CF | 16 | 00 | 01 | 08 | 3F | 00 | 00 | 00 | 01 | 00 | 02 |

| 0000004A  | 50 | FC | A1 | 00 | CF | 20 | 00 | 02 | 40 | 3F | 00 | 00 | 00 | 01 | 00 | 02 |

| 00000094  | 50 | FC | 81 | 00 | DB | 4B | 00 | 03 | 08 | 3F | 00 | 00 | 00 | 01 | 00 | 02 |

| 000000DE  | 50 | FC | A1 | 00 | DB | 56 | 00 | 04 | 40 | 3F | 00 | 00 | 00 | 01 | 00 | 02 |

| 00000128  | 50 | FC | 81 | 00 | E7 | 80 | 00 | 05 | 08 | 3F | 00 | 00 | 00 | 01 | 00 | 02 |

| 00000172  | 50 | FC | A1 | 00 | E7 | 8B | 00 | 06 | 40 | 3F | 00 | 00 | 00 | 01 | 00 | 02 |

| 000001BC  | 50 | FC | 81 | 00 | F3 | B5 | 00 | 07 | 08 | 3F | 00 | 00 | 00 | 01 | 00 | 02 |

| 00000206  | 50 | FC | A1 | 00 | F3 | C0 | 00 | 08 | 40 | 3F | 00 | 00 | 00 | 01 | 00 | 02 |

| 00000250  | 50 | FC | 81 | 00 | FF | EA | 00 | 09 | 08 | 3F | 00 | 00 | 00 | 01 | 00 | 02 |

| 0000029A  | 50 | FC | A1 | 00 | FF | F5 | 00 | 0A | 40 | 3F | 00 | 00 | 00 | 01 | 00 | 02 |

| 000002E4  | 50 | FC | 81 | 00 | OC | 1F | 00 | 0B | 08 | 3F | 00 | 00 | 00 | 01 | 00 | 02 |

帧头 块状态字 时间戳 帧计数 命令字

图 16 1553B 数据回读结果

Fig. 16 The backreading result of 1553B data

传感器组件1高速串口.dat

| Offset(h) | 1E | 1F | 20 | 21 | 22 | 23 | 24 | 25 | 26 | 3A | 3B | 3C | 3D | 3E | 3F | 40 | 41 |

|-----------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 00000000  | 55 | AA | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 65 | F7 | 00 | 00 | 57 | B5 | 50 | 50 |

| 00000048  | 55 | AA | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 65 | F9 | 00 | 00 | 57 | B5 | 9C | 9C |

| 00000090  | 55 | AA | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 65 | FB | 00 | 00 | 57 | B5 | E9 | E9 |

| 000000D8  | 55 | AA | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 65 | FD | 00 | 00 | 57 | B6 | 35 | 35 |

| 00000120  | 55 | AA | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 65 | FF | 00 | 00 | 57 | B6 | 82 | 82 |

| 00000168  | 55 | AA | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 65 | 01 | 00 | 00 | 57 | B6 | CE | CE |

| 000001B0  | 55 | AA | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 65 | 03 | 00 | 00 | 57 | B7 | 1B | 1B |

| 000001F8  | 55 | AA | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 65 | 05 | 00 | 00 | 57 | B7 | 67 | 67 |

| 00000240  | 55 | AA | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 65 | 07 | 00 | 00 | 57 | B7 | B4 | B4 |

| 00000288  | 55 | AA | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 65 | 09 | 00 | 00 | 57 | B8 | 00 | 00 |

图 17 传感器组件 1 数据回读结果

Fig. 17 Data backreading result of sensor component 1

据帧作为测试对象。本次配置对数据帧中的自定义备用字节部分内容进行修改。系统上电后, FPGA 首先将内部数据传输至回读上位机。待数据存储完成后, 通过以太网接口进行系统程序升级。系统会对升级后的内部数据回读校验, 并与初始回读数据对比分析。图 18 展示了两次回读数据的对比结果, 其中标亮部分为自定义的备用字节数据。

在线升级.dat

| Offset(h) | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 0A | 0B | 0C | 0D | 0E | 0F | 10 | 11 | 12 |

|-----------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 00000000  | 50 | FC | 81 | 00 | CF | 16 | 00 | 01 | 08 | 3F | 00 | 00 | 00 | 01 | 00 | 02 | 00 | 03 | 00 |

| 0000004A  | 50 | FC | A1 | 00 | CF | 20 | 00 | 02 | 40 | 3F | AA |

| 00000094  | 50 | FC | 81 | 00 | DB | 4B | 00 | 03 | 08 | 3F | AA |

| 000000DE  | 50 | FC | A1 | 00 | DB | 56 | 00 | 04 | 40 | 3F | AA |

| 00000128  | 50 | FC | 81 | 00 | E7 | 80 | 00 | 05 | 08 | 3F | AA |

| 00000172  | 50 | FC | A1 | 00 | E7 | 8B | 00 | 06 | 40 | 3F | AA |

| 000001BC  | 50 | FC | 81 | 00 | F3 | B5 | 00 | 07 | 08 | 3F | AA |

| 00000206  | 50 | FC | A1 | 00 | F3 | C0 | 00 | 08 | 40 | 3F | AA |

| 00000250  | 50 | FC | 81 | 00 | FF | EA | 00 | 09 | 08 | 3F | AA |

| 0000029A  | 50 | FC | A1 | 00 | FF | F5 | 00 | 0A | 40 | 3F | AA |

| 000002E4  | 50 | FC | 81 | 00 | OC | 1F | 00 | 0B | 08 | 3F | AA |

| 0000032E  | 50 | FC | A1 | 00 | OC | 2A | 00 | 0C | 40 | 3F | AA |

在线升级.dat

| Offset(h) | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 0A | 0B | 0C | 0D | 0E | 0F | 10 | 11 | 12 |

|-----------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 00000000  | 50 | FC | 81 | 00 | CF | 16 | 00 | 01 | 08 | 3F | AA |

| 0000004A  | 50 | FC | A1 | 00 | CF | 20 | 00 | 02 | 40 | 3F | AA |

| 00000094  | 50 | FC | 81 | 00 | DB | 4B | 00 | 03 | 08 | 3F | AA |

| 000000DE  | 50 | FC | A1 | 00 | DB | 56 | 00 | 04 | 40 | 3F | AA |

| 00000128  | 50 | FC | 81 | 00 | E7 | 80 | 00 | 05 | 08 | 3F | AA |

| 00000172  | 50 | FC | A1 | 00 | E7 | 8B | 00 | 06 | 40 | 3F | AA |

| 000001BC  | 50 | FC | 81 | 00 | F3 | B5 | 00 | 07 | 08 | 3F | AA |

| 00000206  | 50 | FC | A1 | 00 | F3 | C0 | 00 | 08 | 40 | 3F | AA |

| 00000250  | 50 | FC | 81 | 00 | FF | EA | 00 | 09 | 08 | 3F | AA |

| 0000029A  | 50 | FC | A1 | 00 | FF | F5 | 00 | 0A | 40 | 3F | AA |

| 000002E4  | 50 | FC | 81 | 00 | OC | 1F | 00 | 0B | 08 | 3F | AA |

| 0000032E  | 50 | FC | A1 | 00 | OC | 2A | 00 | 0C | 40 | 3F | AA |

图 18 在线升级前(上)后(下)数据回读结果

Fig. 18 The data review results before (up) and after (down) online upgrade

经对比分析回读数据与升级后数据, 确认数据帧中的自定义备用数据已成功变更, 直接验证了在线升级方式修改备用数据的有效性。

通过 Vivado 软件生成大小为 2 MB 的配置文件, 在高低温实验室中分别使用系统在线升级功能和传统 Platform Cable USB 调试器配置方法进行升级, 以软件显示配置成功作为标志。如图 19 所示, 在-40°C、30°C 和 100°C 温度环境下, USB 配置用时为 8、10、14 s; 在线升级用时分别为 2、3、5 s。系统在线升级方式比常规 USB 调试器配置方法升级速度提高接近 3 倍。实际升级过程中, 常规方法在 FPGA 板卡集成大系统时, 需对进行拆解、JTAG 接口安装、更换调试转接头和拔插 Platform Cable USB 调试器等操作, 本系统为设备维护人员提供更高效的远程在线升级环境, 显著提高了 FPGA 的升级速度。

表 3 UDT 与 UDP 传输反馈

Table 3 UDT and UDP transmission feedback

| 试验 | UDP  | UDT  | TCP  | UDT     | UDP     |

|----|------|------|------|---------|---------|

| 次数 | 耗时/s | 耗时/s | 耗时/s | 丢失/kbit | 丢失/kbit |

| 1  | 184  | 307  | 373  | 4.0     | 4 088   |

| 2  | 191  | 318  | 380  | 2.1     | 3 734   |

| 3  | 215  | 358  | 395  | 0       | 2 345   |

| 4  | 209  | 344  | 420  | 0       | 2 498   |

| 5  | 199  | 331  | 410  | 1.0     | 3 204   |

由表3可知,系统中采用UDP协议的平均传输速率达到830 Mbit/s,平均丢失数据量为3 173.5 Kbit,采用UDT协议的平均传输速率达到410 Mbit/s,采用UDT协议的平均传输速率达到494 Mbit/s,传输速率优于支持传统拥塞管理的TCP协议,丢包率接近于0,可靠性显著优于UDP协议。

## 5 结 论

本系统实现了RS422、1553B和以太网3种总线的同步监测与控制功能。通过采用简洁精确的数据融合帧结构与传输机制,不仅保障了多总线数据的精准采集,还实现了多源异构数据的高可靠传输。系统支持极端工况大温度跨度下测试,数据采集存储回读结果符合设计,升级功能运行稳定,相比传统配置方式极大提升极端测试环境下可操作性。UDT协议实现零丢包率传输,为传统UDP协议、TCP协议提供了高可靠性的备份方案。多总线多功能飞行测试系统弥补国内飞行测试系统缺少多总线硬件基础的空白,并升级国内现有测试领域部分关键技术,在硬件架构和软件功能上均实现整合创新,为航空测试领域提供了一种高效率高可靠性的测试思路。

## 参考文献

- [1] ZHOU Z, CHEN F, ZHANG P, et al. System online upgrade scheme based on FPGA reconfiguration[C]. 2021 4th International Conference on Advanced Electronic Materials、Computers and Software Engineering(AEMCSE), 2021: 1300-1304.

- [2] YAN F, LIU J, CHUN S. Study of the way to firmware program upgrade in FPGA reconfiguration of distributed geophysical instruments[J]. Sensors and Transducers, 2015, 172(6): 130-138.

- [3] 文丰, 韩冰, 袁小康. 基于千兆以太网的FPGA远距离在线更新设计[J]. 电子设计工程, 2022, 30(24): 60-63.

- [4] WEN F, HAN B, YUAN X K. Design of FPGA remote online update based on gigabit ethernet[J]. Electronic Design Engineering, 2022, 30(24): 60-63.

- [5] 谈良, 纪凌. 基于FPGA的多通道数据采集系统设计与实现[J]. 电子测量技术, 2018, 41(5): 57-63.

- [6] TAN L, JI L. Design and implementation of a multi-channel data acquisition system based on FPGA[J]. Electronic Measurement Technology, 2018, 41(5): 57-63.

- [7] HAN Z ZH, REN Y F, LI H J. Online upgrading of FPGA based on 1553B bus [J]. Electronic Design Engineering, 2022, 30(3): 1-5.

- [8] 党瑞阳, 吴柯锐, 张会新, 等. 基于FPGA的智能在线升级存储系统设计[J]. 电子测量技术, 2024, 47(18): 100-107.

- [9] DANY R Y, WU K R, ZHANG H X, et al. Design of intelligent online upgrade storage system based on FPGA [J]. Electronic Measurement Technology, 2024, 47(18): 100-107.

- [10] 石梅林, 聂建平, 赵博颖. 基于FPGA的FC-AE-1553总线桥接系统研究[J]. 电子设计工程, 2025, 33(11): 90-94.

- [11] SHI M L, NIE J P, ZHAO B Y. Research on bridging system for FC-AE-1553 based on FPGA[J]. Electronic Design Engineering, 2025, 33(11): 90-94.

- [12] 颜景, 张志浩, 彭林, 等. 基于变压器耦合的2.6 GHz功率放大器的设计[J]. 半导体技术, 2022, 47(10): 824-828.

- [13] YAN J, ZHANG ZH H, PENG L, et al. Design of a 2.6 GHz power amplifier with transformer-coupling[J]. Semiconductor Technology, 2022, 47(10): 824-828.

- [14] 文丰, 张晋铭, 张凯华, 等. 基于FPGA的RS422转以太网的设计与应用[J]. 单片机与嵌入式系统应用, 2022, 22(10): 58-61.

- [15] WEN F, ZHANG J M, ZHANG K H, et al. Design and application of RS422 to ethernet based on FPGA[J]. Integrated Circuits and Embedded Systems, 2022, 22(10): 58-61.

- [16] 闫文璇, 张会新, 孔祥博, 等. 基于千兆以太网的高速智能存储系统设计[J]. 单片机与嵌入式系统应用, 2023, 23(11): 88-91.

- [17] YAN W X, ZHANG H X, KONG X B, et al. Design of high-speed intelligent storage technology based on gigabit ethernet[J]. Integrated Circuits and Embedded Systems, 2023, 23(11): 88-91.

- [18] 朱敏, 宋善坤. 基于可见光通信的全双工以太网通信系统设计研究[J]. 科技资讯, 2024, 22(22): 47-49.

- [19] ZHU M, SONG SH K. Research on design of full-duplex ethernet communication system based on visible light communication[J]. Science & Technology Information, 2024, 22(22): 47-49.

- [20] 朱敏, 宋善坤. 基于可见光通信的全双工以太网通信系统设计研究[J]. 科技资讯, 2024, 22(22): 47-49.

- [21] 朱敏, 宋善坤. 基于可见光通信的全双工以太网通信系统设计研究[J]. 科技资讯, 2024, 22(22): 47-49.

- [22] 李霄, 徐思远, 胡瑾贤. 基于FPGA的远程快速在线升级技术研究[J]. 舰船电子对抗, 2023, 46(4): 98-102, 120.

- [23] LI X, XU S Y, HU J X. Research into a rapid remote online upgrade technology based on FPGA [J]. Shipboard Electronic Countermeasure, 2023, 46(4): 98-102, 120.

- [24] 裴升, 刘坤禹, 王鑫, 等. 基于FPGA的UDT协议设计与实现[J]. 信息技术与信息化, 2023(6): 162-165.

- [25] PEI SH, LIU K Y, WANG X, et al. Design and implementation of UDT protocol Based on FPGA[J]. Information Technology and Informationization, 2023(6): 162-165.

- [26] 赵琦. 基于UDT的无线网络链路聚合软件设计与实现[D]. 成都: 西南交通大学, 2023.

- [27] ZHAO Q. Design and implementation of wireless network link aggregation software based on UDT[D]. Chengdu: Southwest Jiaotong University, 2023.

## 作者简介

薛伟何,硕士研究生,主要研究方向为仪器科学与技术。E-mail:1270838138@qq.com

张会新(通信作者),博士,副教授,硕士生导师,主要研究方向为动态测试技术与仪器。E-mail:zhanghx@nuc.edu.cn