DOI:10.19651/j.cnki.emt.2519131

# 基于 FPGA 的高精度激光回波延时系统设计与实现

孙 尘 王凌云

(长春理工大学光电工程学院 长春 130022)

**摘要:** 针对现有激光回波模拟器难以兼顾大范围与高精度延时的问题,设计了基于 FPGA 的高精度“粗精调”全数字延时信号控制系统,以提升脉冲激光测距仪性能检测精度。该系统采用时钟计数器与混合模式时钟管理器(MMCM)动态相位调整策略,通过系统时钟为 250 MHz 的计数器实现粗调延时,利用 MMCM 相位插值技术实现 17.857 ps 步进的精细化补偿。结果表明,系统在 300~30 000 m 测距范围内仿真延时精度优于 6 ps,等效距离精度 0.01 m;实测延时精度优于 1.2 ns,等效距离精度 0.18 m,实现了大范围测距场景下的高精度延时控制,为脉冲激光测距仪的性能检测提供了可靠的延时方案。

**关键词:** 高精度延时;MMCM;相位调整;FPGA;延时系统

中图分类号: TN249; TH744.5 文献标识码: A 国家标准学科分类代码: 460.4030

## Design and implementation of a high-precision laser echo delay system based on FPGA

Sun Chen Wang Lingyun

(School of Opto-Electronic Engineering, Changchun University of Science and Technology, Changchun 130022, China)

**Abstract:** To address the challenge of achieving both wide-range coverage and high-precision delay in conventional laser echo simulators, we designed a fully digital, high-precision delay signal control system with coarse-fine tuning capability, implemented on an FPGA. The system employs a dynamic phase adjustment strategy that integrates a clock counter with a mixed-mode clock manager (MMCM). Coarse delay adjustment is performed using a 250 MHz system clock counter, while fine delay compensation is realized through MMCM-based phase interpolation with 17.857 ps resolution steps. Experimental results demonstrate that, within a simulation range of 300 m to 30 000 m, the delay accuracy is better than 6 ps, corresponding to a distance resolution of 0.01 m. In actual measurements, the delay accuracy exceeds 1.2 ns, equivalent to a distance resolution of 0.18 m. This system achieves precise delay control across a wide range, offering a robust and reliable solution for performance evaluation of pulse laser rangefinders.

**Keywords:** high-precision time delay; MMCM; phase adjustment; FPGA; delay system

## 0 引言

激光回波模拟器是评估脉冲激光测距仪性能的关键设备,其延时实现方式对测距精度具有直接影响<sup>[1]</sup>。随着激光测距仪在模拟距离范围和测量精度方面的不断提升<sup>[2-3]</sup>,研发具备大范围延时能力与高精度控制性能的激光回波模拟器已成为适应测距装备发展需求的重要方向。

当前主要的延时方法分为光纤延时法<sup>[4-6]</sup>、模拟延时法<sup>[7-8]</sup>及数字延时法<sup>[9-13]</sup>三类。为克服单一方法的局限性,部分学者采用数模混合结构设计<sup>[14-15]</sup>。上述延时技术虽已取得比较满意的延时效果,但仍存在一些不足。光纤延时法需多次更改光纤长度的局限性导致适用性受限且难以实

现远距离模拟。模拟延时法受限于模拟器件的非线性特性,进一步扩展模拟范围会导致精度劣化;数字延时法依赖延迟芯片等特定的硬件资源,近距离目标模拟时精度高但延时范围受限;数模混合结构系统设计复杂度高且受硬件结构影响,模拟远距离目标时延时精度劣化。

因此,针对现有延时技术普遍存在大范围与高精度延时难以协同实现的问题,本文设计了激光回波模拟器中基于现场可编程门阵列(field programmable gate array, FPGA)的高精度“粗精调”全数字延时信号控制系统。采用时钟计数器与混合模式时钟管理器(mixed-mode clock manager, MMCM)协同工作的延时结构,在 300~30 000 m(即 2~200 μs 延时)范围内实现了优于 1.2 ns 的高精度延

时控制,有效解决延时范围与精度难以兼顾的问题,为激光测距设备提供可靠的测试方案。

## 1 激光回波模拟器的组成及工作原理

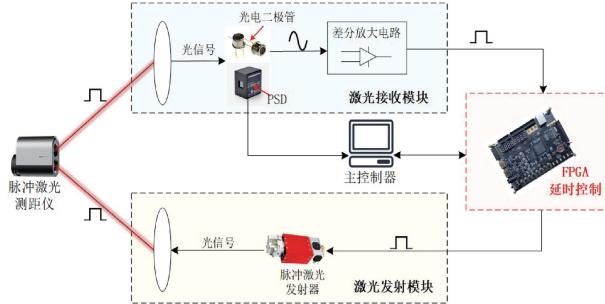

激光回波模拟器通过延时系统模拟激光往返目标的传播距离,生成对应距离的回波信号供测距仪处理<sup>[16]</sup>。该系统由激光接收模块、延时控制模块和激光发射模块组成,其结构如图 1 所示。

图 1 激光回波模拟器的系统结构图

Fig. 1 System structure diagram of the laser echo simulator

系统工作原理如下:激光接收模块通过缩束光学系统对激光测距仪发射的激光脉冲进行光束整形,由位置敏感探测器测量入射角度并将数据反馈至主控制器。同时利用高速光电二极管完成光电信号的转换,经多级差分放大电路进行信号处理后,输出触发信号至延时控制模块。主控制器根据目标距离计算延时参数并配置给 FPGA,采用全数字延时信号控制系统实现高精度延时。经时序调整后的延时信号输出至激光发射模块,驱动脉冲激光器发射激光,光束经扩束光学系统整形后生成回波模拟信号,该信号返回激光测距仪以模拟真实回波过程。系统通过协同控制回波时序,将实测数据与预设参数进行对比,从而实现高精度激光测距仪的测试功能。

系统通过 FPGA 实现延时控制,其时间分辨率决定模拟距离的精度。在激光测距模型中,设回波模拟器生成的激光回波等效往返时间为  $T$ ,则目标距离  $L$  如式(1)所示。

$$L = \frac{1}{2}CT \quad (1)$$

式中:  $C = 3 \times 10^8 \text{ m/s}$  为激光在空气中的传播速度。主控制器根据预设模拟距离  $\Delta L$ ,通过式(1)得到总延迟时间  $\Delta T$ ,并将其分解为接收模块响应时间  $\Delta T_1$ 、延时模块处理时间  $\Delta T_2$  及发射模块响应时间  $\Delta T_3$ ,满足式(2)。

$$\Delta T = \frac{2\Delta L}{C} = \Delta T_1 + \Delta T_2 + \Delta T_3 \quad (2)$$

其中,延时模块处理时间  $\Delta T_2$  为本文的核心优化参数,可进一步分解为粗调延时量  $T_{Coarse}$  与精调延时量  $T_{Fine}$ ,如式(3)所示。

$$\Delta T_2 = T_{Coarse} + T_{Fine} \quad (3)$$

本文基于 FPGA 采用时钟计数器粗调与 MMCM 精调

的协同控制结构,实现系统延时的高精度控制。

## 2 FPGA 高精度延时系统设计

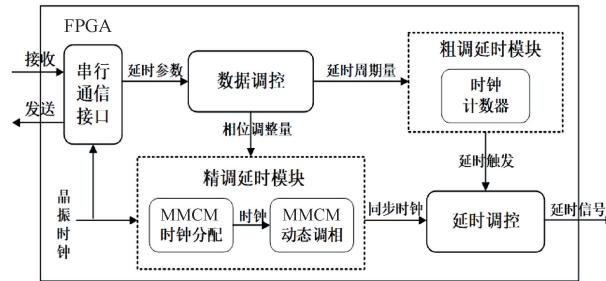

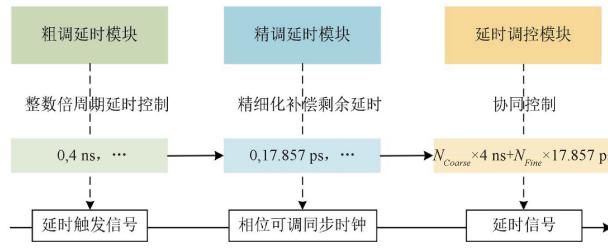

本延时系统的总体设计结构如图 2 所示,采用“粗精调”两级递进式延时调控方案。系统运行时,数据调控模块通过串行通信接口获取目标延时参数,将其分解为粗调延时模块所需的延时周期量及精调延时模块所需的相位调整量,并分别传输至对应延时控制单元。粗调延时模块基于可编程计数器实现千米量级的时钟周期累加,精调延时模块利用 MMCM 生成多相时钟,通过动态调相单元的相位插值技术完成残余延时的精细化补偿。最终在延时调控模块的协同控制下,系统输出覆盖大范围且高精度的延时信号。

图 2 FPGA 总体设计框图

Fig. 2 Overall design block diagram of the FPGA

### 2.1 粗调延时模块设计

粗调延时模块是高精度延时系统的基础功能单元,负责实现目标延时量中整数倍时钟周期部分的延时控制,其延时时间  $T_{Coarse}$  如式(4)所示。

$$T_{Coarse} = N_{Coarse} \cdot T_{CLK} \quad (4)$$

式中:  $N_{Coarse}$  为基于主控制器实时指令解析生成的延时周期量,  $T_{CLK}$  为高稳定性时钟源产生的系统时钟周期,其值为粗调延时模块的最小延时分辨率。

为实现整数倍时钟周期的高精度延时控制,本文采用基于 Artix-7 系列 FPGA 的计数器延时方案,利用芯片充足的查找表(look-up table, LUT)和触发器(flip-flop, FF)等资源实现计数器逻辑与状态存储,通过硬件逻辑对系统时钟周期进行累积计数,并由稳定的全局时钟网络驱动。相比于存储器方案<sup>[17-19]</sup>,该方案具有高延时分辨率、低时序抖动和高资源利用率的优势。通过对系统时钟周期的累积计数,实现千米量级范围内的粗调延时控制,同时为精调延时模块提供稳定的延时基准。为保障时钟信号稳定性并满足系统对时序精度的要求,本设计选用 FPGA 外部 50 MHz 晶体振荡器作为基准时钟源,利用内部 MMCM 时钟分配模块生成 250 MHz 的系统主时钟,实现 4 ns 时钟周期的高精度延时控制。

基于上述时钟系统,粗调延时模块采用同步机制接收外部触发信号及数据调控模块传输的延时周期量  $N_{Coarse}$ ,

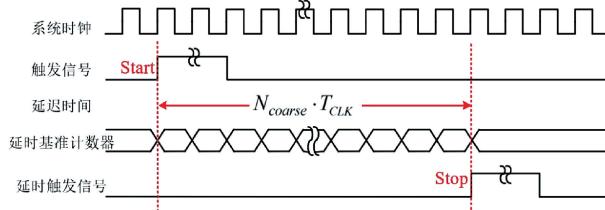

以 4 ns 的系统时钟周期  $T_{CLK}$  为计数单位,采用可编程计数器实现整数周期延时控制。当计数器的数值达到预设延时周期量时,模块输出延时触发信号,完成系统整数倍时钟周期的粗调延时。该延时触发信号同时作为精调延时模块的使能信号,触发其对不足一个时钟周期延时量的精细化补偿。粗调延时模块中触发信号响应、延时计数过程以及延时触发信号生成等关键时序节点间的关系如图 3 所示。

图 3 粗调延时模块时序特性图

Fig. 3 Timing characteristic diagram of the coarse delay module

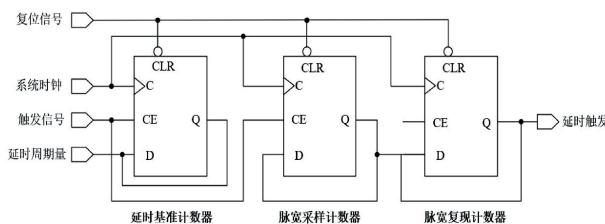

在实际高精度延时控制场景中,若采用单一计数器根据触发信号实现延时控制,可能会出现时序冲突问题。当延时周期量未到达预设值而新触发信号已到达时,会导致系统延时中断,无法实现整数倍时钟周期的延时控制。为避免上述问题,本系统所设计的粗调延时模块在 250 MHz 时钟的同步控制下通过多个计数器并行结构实现。基于图 3 所示的各信号间的时序关系,所有计数器均采用异步复位同步释放设计,通过复位信号统一初始化,并通过状态机驱动 3 个功能独立的 16 位计数器协同工作,其设计结构如图 4 所示。

图 4 计数器设计结构图

Fig. 4 Structural diagram of the counter design

延时基准计数器采用同步上升沿触发机制,通过两级同步寄存器构成的边沿检测电路实现对异步触发信号的亚稳态消除和精确边沿捕获。当检测到经过两级同步处理的触发信号边沿时,状态机立即由初始状态转换至计数状态并启动周期计数。该设计确保计数启动时刻与 250 MHz 时钟严格同步,形成精准的 4 ns 基础延时分辨率。同时支持动态重载延时周期参数,当计数值达到预设值时自动触发状态转换,其 16 位宽度的设计最大支持 65 535 个时钟周期的延时配置,理论延时范围为 0~262.14 μs,满足系统 2~200 μs 延时范围的设计要求。负责对触发信号进行脉宽采样的计数器通过同步双沿触发检测技术实现信号边沿实时监测。在检测到信号上升沿后,状态机由初始状态切

换至计数状态,并在信号高电平期间执行持续累加计数;当检测到同步下降沿时,状态机转入锁存状态,完成当前脉宽数据的锁存操作。脉宽复现计数器在完成预设的整数延时周期后,由状态机控制进入计数状态,在系统时钟上升沿触发累积计数,当动态比较器检测到实时计数值与锁存的脉宽数据相等时,状态机立即转换至终止状态,输出等脉宽的延时触发信号,从而实现一次完整的粗调延时控制流程。

整个延时过程严格遵循同步时序逻辑,各计数器在状态机的协同控制下独立工作,所有状态转换和数值比较均在时钟有效边沿完成。即使前序延时未完成时出现新的触发信号,粗调延时模块仍能维持稳定的时序关系。经综合工具分析显示,该模块实际消耗 112 个 LUT 和 108 个 FF,且未使用块存储器与数字信号处理单元,采用纯逻辑实现,避免了块存储器读写延迟引入的时序不确定性,最终实现 2~200 μs 范围内基于 4 ns 时钟周期的粗调延时控制。

## 2.2 精调延时模块设计

精调延时模块是高精度延时系统的核心功能单元,负责对粗调后不足一个时钟周期的残余延时进行精确补偿,其延时时间如式(5)所示。

$$T_{Fine} = N_{Fine} \cdot T_{Step} \quad (5)$$

式中:  $N_{Fine}$  为基于实时指令解析生成的相位调整量,  $T_{Step}$  为精调延时单元的基本延时量,即最小相位调整步长,该参数是系统延时精度的决定性因素。

为实现残余延时的高精度控制,本文采用 Xilinx Artix-7 系列 FPGA 时钟管理块(clock management tile, CMT)中的混合模式时钟管理器(MMCM)作为核心时序控制单元。相较于锁相环(phase-locked loop, PLL), MMCM 支持动态相位调整功能<sup>[20]</sup>,可实现对输出时钟相位的连续精确调整,满足高精度时序系统的低抖动需求。

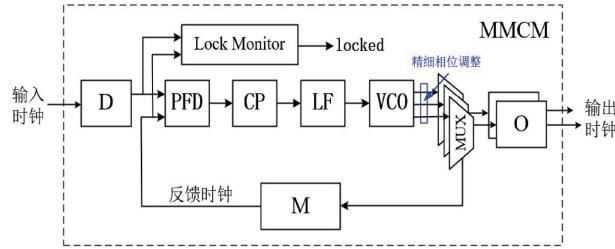

在本延时系统中,MMCM 模块负责高精度时钟生成与动态相位调整。其工作原理如图 5 所示,输入时钟经过可编程输入计数器(DIVCLK\_DIVIDE, D)分频,在相位频率检测器(phase-frequency detector, PFD)中与反馈时钟进行相位和频率比较,生成与二者差值成比例的信号;该信号经过电荷泵(charge pump, CP)和环路滤波器(loop filter, LF)转化为控制电压,驱动压控振荡器(voltage-controlled oscillator, VCO)生成输出信号。输出信号经环路反馈计数器(CLKFBOUT\_MULT\_F, M)分频后反馈至 PFD 构成闭环控制,当锁存信号 locked 有效时实现相位偏差消除,同时经过可编程输出计数器(CLKOUT\_DIVIDE, O)生成多路不同频率和相位的输出时钟。基于上述工作流程,可推导压控振荡器工作频率  $f_{VCO}$ 、输出时钟频率  $f_{COUT}$  与输入时钟频率  $f_{CIN}$  的关系,具体如式(6)和(7)所示。

$$f_{VCO} = \frac{f_{CIN}}{D} \times M \quad (6)$$

$$f_{\text{cout}} = f_{\text{vco}} \times \frac{1}{O} = \frac{f_{\text{cin}}}{D} \times \frac{M}{O} \quad (7)$$

图 5 MMCM 原理图

Fig. 5 Schematic diagram of the MMCM

基于上述 MMCM 工作原理,为满足系统各模块的时序需求,本设计采用双路时钟输出结构:一路输出时钟经全局时钟缓冲器分配至各逻辑单元,为系统提供统一的时序基准;另一路输出时钟需通过动态调相模块进行相位调整,以实现对粗调后剩余延时量的精确补偿,并为延时调控模块提供同步时钟。

为实现精确的延时补偿,系统采用 MMCM 模块的插值精细相移模式实现动态相位调整。该模式采用 VCO 多相抽头选择,实现以  $1/56f_{\text{vco}}$  为线性增量的  $360^\circ$  连续相位调整<sup>[21]</sup>。结合式(6)可推导出最小相位调整步长的表达式,如式(8)所示。

$$T_{\text{Step}} = \frac{1}{56 \times f_{\text{vco}}} = \frac{D}{56 \times f_{\text{cin}} \times M} \quad (8)$$

由式(8)可知,最小相位调整步长与压控振荡器频率成反比关系,由计数器参数 D、M 及输入时钟频率共同决定。理论分析表明,提高压控振荡器频率虽能减小最小相位调整步长以提高延时精度,但会降低系统稳定性。为兼顾延时精度与系统稳定性,在输入时钟频率为 50 MHz 的约束下,通过协同优化相关配置参数,最终确定 D=2、M=20 及 O=2,将压控振荡器频率调整为 1 000 MHz,此时系统的最小相位调整步长约为 17.857 ps。

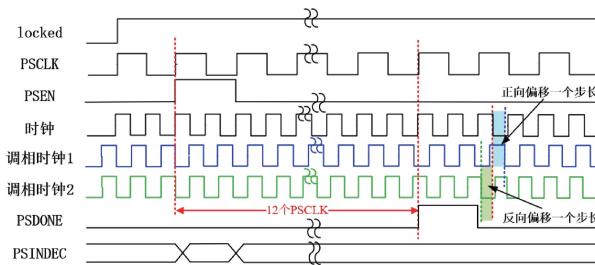

基于上述参数配置,系统采用图 6 所示的时序关系实现动态相位调整控制。当精调延时模块接收到相位调整指令且锁存信号 locked 有效时,系统将触发使能信号 PSEN 启动调相流程。PSEN 信号置位后,经 12 个 PSCLK 时钟周期(PSCLK 为动态调相模块工作时钟)偏移一个相位调整步长,PSDONE 信号置位表示当前相位调整操作完成。为优化平均相位调整次数,系统采用双向相位补偿方案。该方案以时钟周期内相位调整数的中值为阈值基准,采用 MMCM 生成初始相位差互补的两路时钟信号,根据相位调整量与阈值的比较结果控制 PSINCDEC 信号实现调相时钟正向或反向偏移。在确定最优目标移相步数后,循环执行相位调整指令,以实现对系统剩余延时量的精确补偿。

基于 17.857 ps 的最小相位调整步长,将双向相位补偿方案的最大移相步数配置为 112 步,通过双向偏移实现单个时钟周期的相位调整范围,在保证调整精度的同时优

图 6 单次动态相位调整时序图

Fig. 6 Timing diagram of single-cycle dynamic phase adjustment

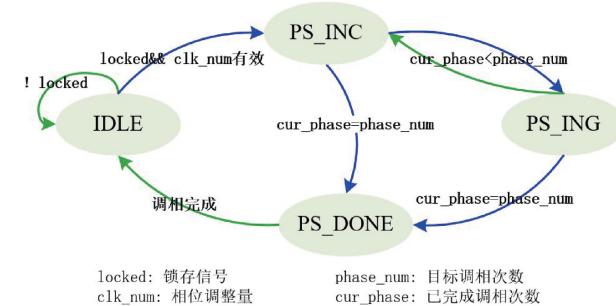

化调相次数。为实现上述动态相位调整的时序控制,本系统设计了包含 4 个状态的有限状态机。如图 7 所示,该状态机通过监测各控制信号的状态以实现动态相位调整,其具体状态及转移条件如下:

1) 空闲状态(IDLE): 系统复位后,将相移使能信号 PSEN 置为低电平,清零相位调整计数器。若锁存信号 locked 有效且相位调整参数 clk\_num 在有效范围内,系统基于设定阈值计算得出调相的相关控制参数,进入相位调整准备状态(PS\_INC);否则,继续保持 IDLE 状态,等待有效信号。

2) 相位调整准备状态(PS\_INC): 在此状态下,系统比较当前已完成调相次数 cur\_phase 与目标调相次数 phase\_num。若未达到目标调相次数,则置位 PSEN 启动相位调整操作,进入相位调整进行状态(PS\_ING);若调相已完成,则跳转至相位调整完成状态(PS\_DONE)。

3) 相位调整进行状态(PS\_ING): 监测相位调整完成信号 PSDONE。若 PSDONE 无效,保持此状态继续等待;若 PSDONE 有效,则判断剩余相位调整次数,当存在未完成任务时,返回 PS\_INC 状态继续相位调整;否则,转移至 PS\_DONE 状态。

4) 相位调整完成状态(PS\_DONE): 清零相位调整计数器并返回至 IDLE 状态,等待下一次相位调整请求,构成闭环控制流程,从而实现动态相位调整的持续运行。

图 7 状态机转移流程图

Fig. 7 State machine transition flowchart

通过上述有限状态机的闭环控制,实现 MMCM 模块的动态相位调整功能,以 17.857 ps 的步进值对粗调后不足一个时钟周期的剩余延时量进行精确补偿,从而提高系

统整体的延时控制精度。

### 2.3 延时调控模块设计

延时调控模块作为系统延时功能的终端执行单元,通过协同控制粗调与精调两级延时信号的时序关系,实现延时信号的优化输出。如图 8 所示,该模块通过以下设计实现优化控制:基于粗调延时模块产生的整数倍时钟周期延时量与精调延时模块生成的亚时钟周期补偿延时量的线性叠加,以确定延时系统的总延时量。在精调延时模块输出的同步时钟控制下,对粗调延时触发信号进行跨时钟域精准捕获,消除亚稳态风险,最终输出覆盖大范围且具备高精度的延时信号。基于该模块的协同控制结构及式(3)~(5)建立的数学模型,可推导出系统优化后的延时模块处理时间  $\Delta T_2$ ,如式(9)所示。

$$\Delta T_2 = N_{\text{Coarse}} \cdot T_{\text{CLK}} + N_{\text{Fine}} \cdot T_{\text{Step}} \quad (9)$$

图 8 两级延时模块协同工作示意图

Fig. 8 Schematic diagram of collaborative operation for two-stage delay modules

## 3 实验验证及仿真

### 3.1 仿真测试

本系统采用“粗精调”两级延时协同控制结构,实现千米量级范围内的高精度延时控制。为全面验证系统性能,基于 Modelsim 仿真平台,分别进行粗调、精调延时模块的单独测试及系统综合测试。

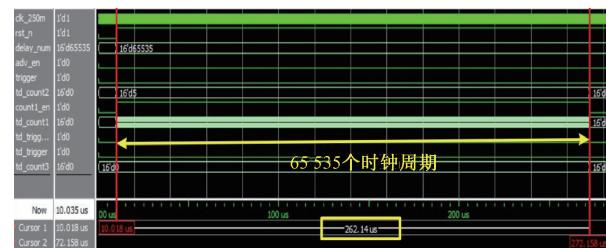

在各模块单独测试环节,首先对粗调延时模块开展仿真测试。通过设置不同的时钟周期数  $\text{delay\_num}$ (取值范围为 0~65 535),检验该模块的范围延时控制性能。如图 9 所示,在系统时钟信号  $\text{clk}_{250\text{m}}$  驱动下,触发信号  $\text{trigger}$  处于高电平有效状态时,16 位计数器对系统时钟周期进行累加计数。当计数值达到预设值 65 535 时生成  $262.14\mu\text{s}$  的粗调延时,并输出与系统时钟上升沿同步的延时触发信号  $\text{td\_trigger}$ 。仿真测试结果表明,粗调延时模块基于 4 ns 时钟周期的整数倍累积计数,可实现最大  $262.14\mu\text{s}$  的延时调节范围,完全覆盖系统要求的 2~200  $\mu\text{s}$  延时区间,等效测距范围为 300~30 000 m。

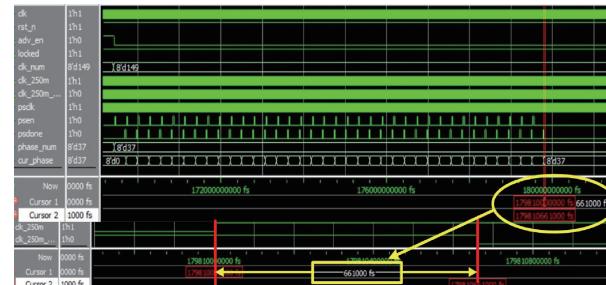

在完成粗调延时模块验证后,对精调延时模块展开仿真测试。通过设置系统相位调整参数,比较理论延时补偿值与仿真输出结果,以验证该模块在动态相位调整过程中对亚时钟周期延时精度的调控能力。如图 10 的时序仿真结果所示,当相位调整量  $\text{clk\_num}$  设定为 149 次时,系统基

图 9 粗调延时模块仿真结果

Fig. 9 Simulation results of the coarse delay module

于阈值已完成半时钟周期的相位预调整,经比较后执行 37 次优化相位调整量的连续动态调相操作。此时理论累积相位偏移量为 660.709 ps,仿真测试结果为 661.000 ps,二者相差 0.291 ps(约 0.04%)。经分析,该偏差主要源于以下因素:其一,MMCM 实际最小相位步长为离散值,且受限于相位累加器位宽,在整数运算过程中产生量化误差。其二,时序仿真工具采用固定时间步长进行信号边沿采样,若理想相位跳变时刻与离散采样点存在时间差,该偏差将在相位调整过程中产生累积效应。然而,理论计算与仿真结果的偏差量级对系统整体延时精度的影响可忽略不计。综上所述,精调延时模块在完成半时钟周期相位预调整的基础上,通过优化相位调整量可实现皮秒级相位补偿,满足亚时钟周期延时控制的精度要求。

图 10 精调延时模块仿真结果

Fig. 10 Simulation results of the fine delay module

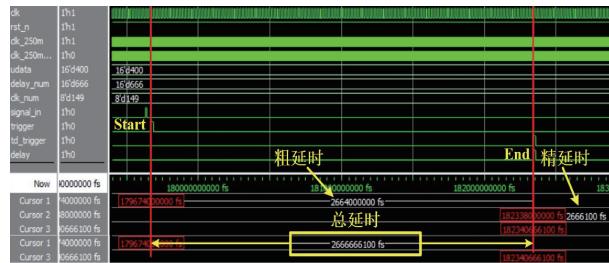

在完成各模块验证后,进行系统综合仿真测试:通过测量触发信号  $\text{trigger}$  至延时输出信号  $\text{delay}$  的时间间隔,验证系统的延时控制性能。以 400 m 模拟距离为测试条件,其仿真结果如图 11 所示。当模拟距离参数  $\text{udata}$  设定为 400 时,解析得出延时周期量  $\text{delay\_num}$  为 666,相位调整量  $\text{clk\_num}$  为 149。粗调延时模块基于 4 ns 时钟周期的整数倍特性实现 2 664.000 ns 的基础延时;精调延时模块在完成 2 ns 半时钟周期相位预调整的基础上,通过优化相位调整量实现 0.661 ns 的动态相位补偿,最终输出 2.661 ns 的精调延时。系统仿真测试的总延时为 2 666.661 000 ns,与理论值 2 666.666 667 ns 的绝对误差为 5.667 ps。该数据表明,通过粗调与精调延时模块的协同控制,系统在仿真环境下可实现皮秒级延时控制精度。

为验证系统在千米量级范围内的延时性能,在 300~

图 11 400 m 模拟距离的系统仿真结果

Fig. 11 System simulation results for 400 m simulated distance

30 000 m 测距范围内, 基于等对数间距采样原则选取 16 组距离点进行系统综合仿真验证。如表 1 所示, 测试数据覆盖近、中、远距离范围, 通过对比理论延时值与仿真延时数据, 系统评估不同距离条件下的延时控制性能。

表 1 延时系统仿真数据表

Table 1 Simulation data table of the delay system

| 模拟距离 /m | 理论延时 /ns        | 仿真延时 /ns        | 仿真误差 /ps |

|---------|-----------------|-----------------|----------|

| 300     | 2 000.000 000   | 2 000.000 000   | 0        |

| 350     | 2 333.333 333   | 2 333.339 000   | 5.667    |

| 400     | 2 666.666 667   | 2 666.661 000   | -5.667   |

| 500     | 3 333.333 333   | 3 333.339 000   | 5.667    |

| 700     | 4 666.666 667   | 4 666.661 000   | -5.667   |

| 1 000   | 6 666.666 667   | 6 666.661 000   | -5.667   |

| 1 500   | 10 000.000 000  | 10 000.000 000  | 0        |

| 2 000   | 13 333.333 333  | 13 333.339 000  | 5.667    |

| 3 000   | 20 000.000 000  | 20 000.000 000  | 0        |

| 5 000   | 33 333.333 333  | 33 333.339 000  | 5.667    |

| 7 500   | 50 000.000 000  | 50 000.000 000  | 0        |

| 10 000  | 66 666.666 667  | 66 666.661 000  | -5.667   |

| 15 000  | 100 000.000 000 | 100 000.000 000 | 0        |

| 20 000  | 133 333.333 333 | 133 333.339 000 | 5.667    |

| 25 000  | 166 666.666 667 | 166 666.661 000 | -5.667   |

| 30 000  | 200 000.000 000 | 200 000.000 000 | 0        |

表 1 中呈现 0 ps、5.667 ps 与 -5.667 ps 三组仿真误差值, 该现象源于数据调控模块的算法设计。模拟距离经线性映射转换为时间量后, 系统将其分解为粗调延时周期量与精调相位调整量。由于离散相位步进与时钟周期存在非整数倍关系, 精调延时与模拟距离的映射呈现周期性分布特征。精调延时量在模运算下呈现三模态分布对应产生三组离散的相位调整量, 最终导致仿真测试呈现上述误差数据。

仿真结果表明, 该系统在 300~30 000 m 测距范围内实现优于 6 ps 的延时精度(对应距离精度优于 0.01 m), 实现了系统的高精度延时控制。

### 3.2 实验结果与分析

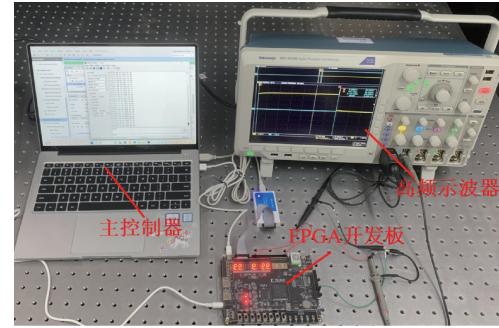

为验证所设计的全数字延时系统的性能, 基于 Xilinx Artix-7 系列 FPGA(型号 XC7A35 T)搭建激光回波实验平台, 如图 12 所示。该平台由三部分构成: 主控制器通过 UART 协议向 FPGA 发送指令; FPGA 开发板根据指令生成与目标距离对应的激光回波模拟信号; Tektronix DPO4054B 高频示波器(带宽 500 MHz 采样率 2.5 GSa/s)采集信号并分析延时精度。各部分通过数据线将主控制器、FPGA 和示波器互联, 评估不同距离下的延时控制性能。

图 12 回波模拟实验平台搭建

Fig. 12 Construction of the echo simulation experiment platform

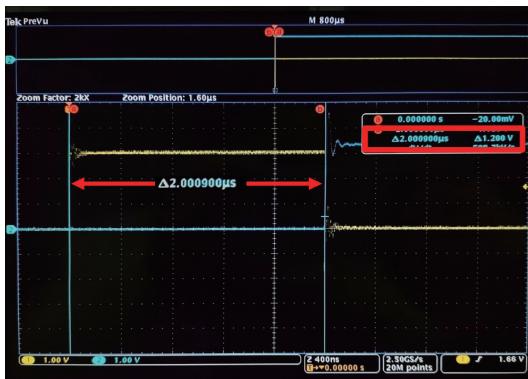

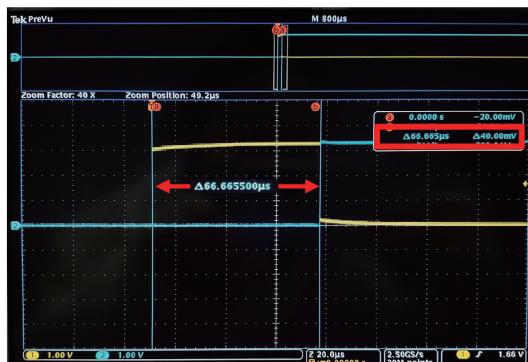

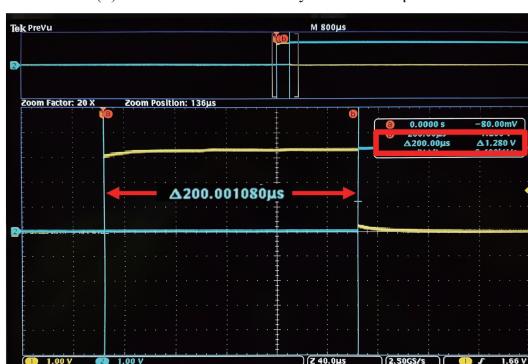

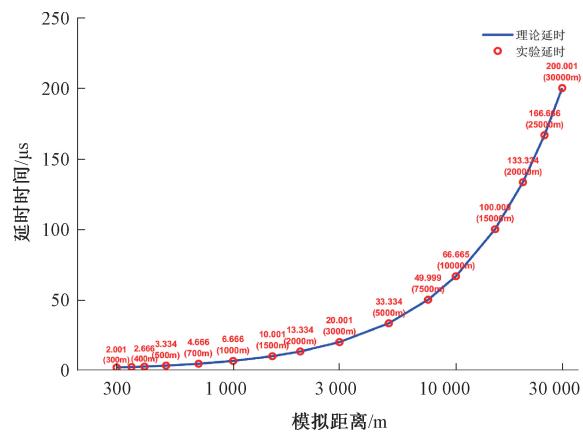

通过搭建的硬件实验平台, 对 300~30 000 m(即 2~200  $\mu$ s 延时)范围内的 16 组距离点进行延时精度测试。高频示波器 Ch1(触发信号)与 Ch2(延时信号)采用上升沿触发捕获的三组实测波形如图 13(a)~(c)所示, 分别对应 300、10 000 和 30 000 m 距离的测试结果, 验证了系统在不同距离下的延时响应能力。理论延时与实验延时在不同模拟距离下的对比情况如图 14 所示, 蓝色实线表示理论延时, 红色散点代表实验延时。在 300~30 000 m 范围内实验延时数据与理论延时曲线紧密贴合, 表明所设计的延时系统能够准确地生成与目标距离相匹配的延时信号。

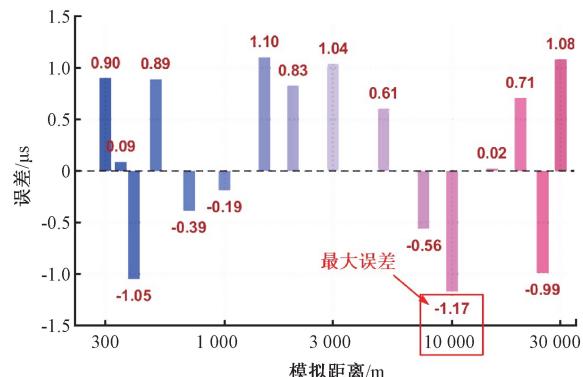

图 15 的实验误差分布结果显示, 系统误差波动控制在  $\pm 1.2$  ns 范围内, 且在 10 000 m 处出现最大绝对误差 1.167 ns。实验误差主要由多个非理想因素叠加造成:

#### 1) 时钟抖动误差

所采用的 MMCM 模块基于 VCO 的锁相环结构, 其输出时钟即使处于锁定状态, 仍不可避免地存在相位噪声与随机抖动。同时, 时钟信号存在周期性抖动, 其实际上升沿相对于理想周期发生的微小随机偏移而产生相位噪声<sup>[22]</sup>。在长距离传输中, 这种抖动在每一个周期都可能存在小偏差, 导致累积性偏移。

#### 2) 电源与温度扰动误差

外部输入晶振存在自身抖动, 在倍频工程中被放大。同时, 电源纹波、供电电压与温度变化也会干扰 VCO 导致相位不稳定。

#### 3) 结构性实现误差

FPGA 内部不同逻辑路径之间存在布线长度差异, 门

(a) 距离300 m 延时2.000 900  $\mu s$

(a) Distance:300 m delay:2.000 900  $\mu s$

(b) 距离10 000 m 延时66.665 500  $\mu s$

(b) Distance:10 000 m delay:66.665 500  $\mu s$

(c) 距离30 000 m 延时200.001 080  $\mu s$

(c) Distance:30 000 m delay:200.001 080  $\mu s$

图 13 示波器测量实验结果

Fig. 13 Experimental results measured by oscilloscope

级延迟在温度与电压的变化下产生波动, 导致时钟到达时间在逻辑单元间不一致, 影响系统的时序精度。

#### 4) 示波器测试误差

虽然示波器具备较高采样率, 但实际信号采样点位置仍存在采样抖动。此外, 周期性信号在触发边沿的不稳定性亦会导致时标偏移, 影响测量精度。

因此, 系统在实际测试中受限于多种非理想因素的共同作用, 导致实测误差相较于仿真具有数量级提升。

实验结果表明, 本文设计的延时系统在 300~30 000 m 测距范围内实现优于 1.2 ns 的延时精度, 验证了其在大测

图 14 理论与实验数据对比图

Fig. 14 Comparison diagram of theoretical and experimental data

图 15 实验误差分布图

Fig. 15 Distribution of experimental errors

量范围下仍具备高精度的延时控制能力。为进一步评估本系统的综合性能优势, 选取了文献[4-15]中的延时方法进行对比分析, 关键性能指标对比如表 2 所示。

表 2 不同延时方法性能对比

Table 2 Performance comparison of different delay methods

| 延时方法                     | 延时精度         | 测距范围          |

|--------------------------|--------------|---------------|

| 光纤延时法 <sup>[4-6]</sup>   | 0.1 ps~10 ns | 0 m~14.8 km   |

| 模拟延时法 <sup>[7-8]</sup>   | 30 ps~6.7 ns | 0 m~3 km      |

| 数字延时法 <sup>[9-13]</sup>  | 1 ps~0.65 ns | 0 ~18 m       |

| 数模混合法 <sup>[14-15]</sup> | 2 ~3 ns      | 0 m~7 km      |

| 本系统                      | $\pm 1.2$ ns | 300 m~30000 m |

分析结果表明, 现有延时方法在大范围应用场景中存在精度下降问题, 且在实现高精度时其延时范围受限, 难以实现大范围与高精度的协同优化。与之相比, 本系统在 300~30 000 m 范围内实现优于 1.2 ns 延时精度, 为激光测距等应用提供更优的解决方法。

#### 3.3 系统占用资源分析

本文采用 Vivado 2018.3 对 XC7A35 T 平台进行综合

布线，并扩展分析其在不同规格 FPGA 器件上的资源使用情况。表 3 对比了不同 FPGA 型号的资源利用率。

**表 3 不同规模 FPGA 的资源利用率**

**Table 3 Resource utilization of FPGAs of different sizes**

| 资源名称 | %           |             |              |           |          |

|------|-------------|-------------|--------------|-----------|----------|

|      | XC7A<br>35T | XC7A<br>75T | XC7A<br>100T | Spartan-7 | Kintex-7 |

| LUT  | 7.36        | 3.24        | 2.41         | 3.19      | 3.73     |

| FF   | 0.85        | 0.38        | 0.28         | 0.37      | 0.43     |

| DSP  | 2.22        | 1.11        | 0.83         | 1.43      | 0.83     |

| IO   | 2.80        | 2.46        | 2.46         | 2.07      | 2.46     |

| BUFG | 12.50       | 12.50       | 12.50        | 12.50     | 12.50    |

| MMCM | 20.00       | 16.67       | 16.67        | 12.50     | 16.67    |

从表 3 数据可知，本系统在 Artix-7 至 Kintex-7 系列等不同规模 FPGA 器件上均展现出良好的资源适配性。随着 FPGA 器件规模的扩大，资源利用率降低 ( $LUT < 4\%$ ,  $FF < 0.5\%$ ,  $DSP < 1.5\%$ )，且全局缓冲资源的占用率保持稳定。相比于其他规模器件，所选 XC7A35 T 平台在满足当前需求的前提下，实现了资源利用率与成本效益的较优平衡。

## 4 结 论

本文设计了一种基于 FPGA 的高精度“粗精调”全数字延时信号控制系统，采用时钟计数器粗调与 MMCM 动态相位精调的延时架构，解决了现有激光回波模拟器在延时控制方面难以兼顾大范围与高精度的问题。在 300~30 000 m 测距范围内，仿真验证其延时精度优于 6 ps，等效距离为 0.01 m。实验测试中受限于多种非理想因素的共同作用，实际延时精度优于 1.2 ns，等效距离为 0.18 m。未来随着 FPGA 时钟架构与动态相位调节技术的协同优化，将进一步提升激光测距等领域的延时控制精度。

## 参考文献

- [1] XU R, SHI R, YE J S, et al. Research on key technologies of LADAR echo signal simulator [C]. Beijing Institute of Technology (China), 2015.

- [2] 王宇琦, 母一宁, 温冠宇, 等. 用于通信成像一体化的变基准三角法测距模型 [J]. 电子测量与仪器学报, 2024, 38(1): 145-153.

- WANG Y Q, MU Y N, WEN G Y, et al. Ranging model of variable reference triangle method for integrated communication and imaging [J]. Journal of Electronic Measurement and Instrumentation, 2024, 38(1): 145-153.

- [3] 胡新源, 杨凌辉, 宋有建, 等. 基于时域可区分特征的双飞秒激光多目标绝对距离测量 [J]. 仪器仪表学报, 2023, 44(8): 74-81.

- HU X Y, YANG L H, SONG Y J, et al. Absolute distance measurement of multiple targets using dual femtosecond lasers with time-domain distinguishable characteristics [J]. Chinese Journal of Scientific Instrument, 2023, 44(8): 74-81.

- [4] NI Z H, LU L J, LIU Y B, et al. Silicon-integrated 8-channel 6-bit tunable optical true-time delay lines with high switching speed and low loss [C]. 2023 International Topical Meeting on Microwave Photonics, 2023: 1-5.

- [5] 李欢, 余红英. 基于 FPGA 的高性能激光雷达测距系统设计 [J]. 电子测量技术, 2021, 44(20): 6-10.

- LI H, YU H Y. Design of high-performance lidar ranging system based on FPGA [J]. Electronic Measurement Technology, 2021, 44(20): 6-10.

- [6] 欧阳竑, 王侠, 韦幕野, 等. 光纤延时测量技术研究 [J]. 光电技术应用, 2020, 35(4): 41-44.

- OUYANG H, WANG X, WEI M Y, et al. Research on optical fiber delay measurement technology [J]. Electro-Optic Technology Application, 2020, 35(4): 41-44.

- [7] 徐翔宇, 王劲松. 基于高精度延时芯片的激光回波模拟电路设计 [J]. 科技资讯, 2015, 13(3): 6-8.

- XU X Y, WANG J S. Design of laser echo simulation circuit based on high-precision delay chip [J]. Science & Technology Information, 2015, 13(3): 6-8.

- [8] 王梦宇, 张延超, 李美伦, 等. 用于激光雷达的高精度脉冲延时及脉宽控制研究 [J]. 机械与电子, 2016, 34(8): 3-6.

- WANG M Y, ZHANG Y CH, LI M L, et al. Research on high-precision pulse delay and width control for lidar [J]. Machinery & Electronics, 2016, 34(8): 3-6.

- [9] MA J H, ZHANG L G, HUI Y Z, et al. Design and implementation of dynamic phase adjustment technology based on delayed phase-locked loop [C]. 14th International Conference on Measuring Technology and Mechatronics Automation, 2022: 52-56.

- [10] 刘士兴, 李江晖, 夏进, 等. 应用于 ATE 的时间测量单元设计 [J]. 电子测量与仪器学报, 2023, 37(6): 86-92.

- LIU SH X, LI J H, XIA J, et al. Design of time measurement unit applied to ATE [J]. Journal of Electronic Measurement and Instrumentation, 2023, 37(6): 86-92.

- [11] ZHU M, CUI T, QI X H, et al. A picosecond delay generator optimized by layout and routing based on

- FPGA[J]. Sensors (Basel, Switzerland), 2023, 23(13), DOI:10.3390/S23136144.

- [12] 余甜,王志斌,景宁.皮秒分辨率数字可编程精密延迟触发技术[J].电子测量技术,2023,46(3):75-79.

YU T, WANG ZH B, JING N. Picosecond resolution digitally programmable precision delay trigger technology[J]. Electronic Measurement Technology, 2023, 46(3): 75-79.

- [13] SOBOTKA J, ADLER V, NOVAK J. Sub-clock Digital Delay for Radar Target Simulation[C]. IEEE International Workshop on Metrology for Automotive, 2023:170-174.

- [14] 张晖,刘静军.激光回波模拟系统[J].光电技术应用,2016,31(1):1-3,28.

ZHANG H, LIU J J. Laser echo simulation system[J]. Electro-Optic Technology Application, 2016, 31(1): 1-3,28.

- [15] LIU M, ZHANG G Y, AN ZH Y, et al. Detection method for ranging performance of IR laser rangefinder based on aerosol echo simulation[J]. Optik-International Journal for Light and Electron Optics, 2016, 127 (1): 25-29.

- [16] ZHANG P, WANG P, WU H J, et al. FPGA based echo delay control method for pulse radar testing[C]. 13th IEEE International Conference on Electronic Measurement & Instruments, 2017: 34-38.

- [17] 任亚欣,王瑞斌,侯涛.雷达回波模拟器的设计与实现[J].火控雷达技术,2021,50(1):98-101,107.

REN Y X, WANG R B, HOU T. Design and implementation of radar echo simulator [J]. Fire Control Radar Technology, 2021, 50(1): 98-101,107.

- [18] 苏淑婧,余毅.一种高精度脉冲延时电路设计[J].舰船电子工程,2023,43(10):226-230.

- SU SH J, YU Y. Design of a high-precision pulse delay circuit[J]. Ship Electronic Engineering, 2023, 43(10): 226-230.

- [19] 徐洋洋.基于 FPGA 的多通道大容量 FIFO 设计[J].电子测量技术,2017,40(8):193-197.

XU Y Y. Design of multi-channel large-capacity FIFO based on FPGA [J]. Electronic Measurement Technology, 2017, 40(8): 193-197.

- [20] 王媖姿,闫冰,李志天,等.基于载波双向频率传递的时钟同步系统[J].微电子学与计算机,2022,39 (8): 97-106.

WANG Y Z, YAN B, LI ZH T, et al. Clock synchronization system based on two-way carrier frequency transfer[J]. Microelectronics & Computer, 2022, 39(8): 97-106.

- [21] 王伟,张瑞峰.基于 FPGA 的高分辨率数字时间转换器[J].强激光与粒子束,2023,35(3):159-167.

WANG W, ZHANG R F. High-resolution digital time converter based on FPGA[J]. High Power Laser and Particle Beams, 2023, 35(3): 159-167.

- [22] 刘涛,赵金迪,苏洋,等.基于 ATE 的 SIP 时钟抖动测试分析及优化[J].电子制作,2025,33(9):96-98.

LIU T, ZHAO J D, SU Y, et al. SIP clock jitter test analysis and optimization based on ATE[J]. Electronic Production, 2025, 33(9): 96-98.

## 作者简介

孙尘,硕士研究生,主要研究方向为智能测试技术与系统、航天器地面标定技术。

E-mail:19396269059@163.com

王凌云(通信作者),教授,博士生导师,主要研究方向为智能测试技术与系统、航天器地面标定技术、光电检测技术等。

E-mail:15004318783@126.com