DOI:10.19651/j.cnki.emt.2518037

# 基于 FPGA 的 SATA 图像采集系统的设计与实现<sup>\*</sup>

王振 黄春平 陈威威

(重庆邮电大学光电工程学院 重庆 400065)

**摘要:** 本文设计并实现了一个基于 FPGA 的高速图像采集与存储系统, 旨在解决高速图像数据采集和存储过程中的性能瓶颈。系统通过 Camera Link 接口接收高速图像数据, 并利用 FPGA 实现 SATA 协议控制器以高效稳定地存储至 SATA 硬盘。图像采集模块采用 Xilinx FPGA 内置的 LVDS 收发器及特定原语(如 IDELAYE3 和 ISERDESE3)直接处理 Camera Link 协议, 取代传统专用芯片。在 MicroBlaze 中设计了一个轻量级文件系统, 以实现 SATA 控制器的配置和数据流的控制。通过集成以太网模块, 系统能够实时导出数据至上位机。开发了 C# 上位机软件, 提供可视化的文件系统界面, 用于管理和监控磁盘及文件操作。实验验证表明, SATA 控制器实现了高达 504.8 MB/s 的写入速率和 542.0 MB/s 的读取速率。在 400 MB/s 的数据采集速率下, 系统表现出了优异的性能和可靠性, 适用于高性能图像采集与存储应用。

**关键词:** FPGA; 图像采集; SATA; 高速存储; 文件系统

中图分类号: TN911.7 文献标识码: A 国家标准学科分类代码: 510.99

## Design and implementation of a SATA image storage system based on FPGA

Wang Zhen Huang Chunping Chen Weiwei

(School of Communication and Information Engineering, Chongqing University of Posts and Telecommunications, Chongqing 400065, China)

**Abstract:** This paper designs and implements a high-speed image acquisition and storage system based on FPGA, aiming to address the performance bottlenecks in high-speed image data acquisition and storage. The system receives high-speed image data through the Camera Link interface and utilizes an FPGA-implemented SATA protocol controller to efficiently and stably store the data on SATA hard drives. The image acquisition module employs Xilinx FPGA's built-in LVDS transceivers and specific primitives(such as IDELAYE3 and ISERDESE3) to directly process the Camera Link protocol, replacing traditional dedicated chips. A lightweight file system is designed within the MicroBlaze for configuring the SATA controller and controlling data flow. By integrating an ethernet module, the system can export data to a host computer in real-time. A C# host software was developed, providing a visualized file system interface for managing and monitoring disk and file operations. Experimental results show that the SATA controller achieves write speeds of up to 504.8 MB/s and read speeds of up to 542.0 MB/s. At a 400 MB/s data acquisition rate, the system demonstrates excellent performance and reliability, making it suitable for high-performance image acquisition and storage applications.

**Keywords:** FPGA; image acquisition; SATA; high-speed storage; file system

## 0 引言

随着高速成像技术<sup>[1]</sup>的迅猛进步, 图像传感器在分辨率和帧率等关键性能指标上的显著提升, 极大地扩展了其在航空、航天及武器测试等领域的应用范围。尤其是在处理高速图像时, 实现大容量、快速的数据存储解决方案显得

尤为重要且具有挑战性。

在 CameraLink 接口实现方面<sup>[2-3]</sup>, 现有研究主要是使用专用芯片方案, 如甄国涌等<sup>[4]</sup>采用 DS90CR286 芯片实现 Base 模式图像采集, 虽能实现稳定传输, 但需额外配置解串芯片。这样不仅传输速率会受到芯片限制, 还会占用大量硬件空间和主控芯片的 I/O 口资源, 不利于产品小型化

和低成本的需求。在高速图像采集的存储方面,有些并未采用外部存储介质,而是直接利用双倍数据速率(double data rate, DDR)存储器作为数据缓存来临时存放图像数据<sup>[5-6]</sup>,如刘宇宇等<sup>[7]</sup>提出的基于现场可编程门阵列(field programmable gate array, FPGA)和通用串行总线(universal serial bus, USB)3.0的高速CameraLink图像采集系统。尽管这种方法能够在一定程度上提高数据采集效率,但在缺乏外部高速存储介质的情况下,面对大规模数据存储需求时仍面临瓶颈。为了克服上述限制,一些研究开始探索使用NAND Flash芯片作为存储介质的可能性<sup>[8-9]</sup>。例如,段梦月等<sup>[10]</sup>在其图像采集存储系统中采用了TF卡作为采集图像的存储单元。然而,NAND Flash的写入速度通常不足以应对高速图像数据的存储需求。另一方面,也有方案选择使用固态硬盘(solid-state drive, SSD)作为存储介质<sup>[11-14]</sup>,如李晋涛等<sup>[15]</sup>提出的基于串行高级技术附件(serial advanced technology attachment, SATA)3.0的大容量图像数据的实时存储方案。国际上,Niwase等<sup>[16]</sup>提出的基于LiteX框架的FPGA直连SATA磁盘方案,实现了写操作速率为569.1 MB/s,读操作速率为523.8 MB/s,展示了高效的大容量数据存储能力。尽管这些方案能够有效解决高速大容量数据存储的问题,但在人机交互和系统灵活性方面仍有待改进。例如,缺乏一个可视化的上位机操作界面,限制了系统的易用性和用户友好性。

针对上述问题,本文提出一种基于FPGA的全集成高速图像采集与存储系统。通过Xilinx UltraScale FPGA原生低压差分信号(low-voltage differential signaling, LVDS)接口解析Camera Link协议,摒弃专用串并转换芯片,实现Full模式的解析。同时,研发了一个SATA 3.0控制器,用FPGA逻辑实现了SATA各个协议层,并添加了先进可扩展接口(advanced extensible interface, AXI)以增强系统的统一性和灵活性。控制器结合AXI中心直接内存访问(center direct memory access, CDMA)与双端口块RAM(block RAM, BRAM)构建DDR4-SSD乒乓缓冲链路。为提高人机交互和系统灵活性作了一下工作:在MicroBlaze软核中开发嵌入式的简要文件系统,支持文件级操作(创建/删除/读写);通过软核构建任务调度器,利用简化千兆媒体独立接口(reduced gigabit media independent interface, RGMII)接口与轻量级IP协议栈(lightweight IP, LWIP)实现以太网实时数据导出;开发C#上位机软件可视化的文件系统界面,并支持一键式采集控制。

实验结果显示,所设计的控制器连续写入速率达到504.8 MB/s,读取速率达到542.0 MB/s。在400 MB/s的相机数据采集场景下,系统能够稳定地进行图像数据采集。这些结果证明,该系统不仅能够在高速图像采集过程中保持高效稳定的性能,还在高速图像采集与存储领域展现了广阔的应用前景。

## 1 系统概述

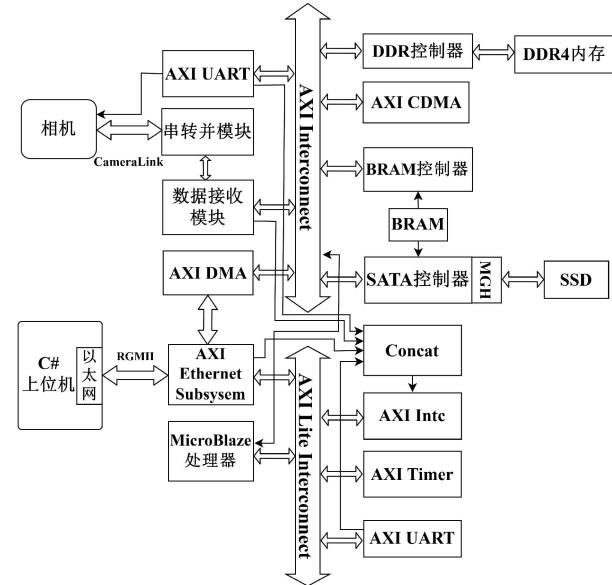

本文设计了一种基于FPGA的高速图像采集与存储系统,其系统架构如图1所示。该系统主要由图像采集模块、数据存储模块、以太网通信模块以及控制管理模块组成,通过AXI互联总线实现模块间的高效协作。

图1 系统架构框图

Fig. 1 System architecture block diagram

图像采集模块采用Camera Link接口接收来自相机的高速图像数据。接收到的数据首先通过串并转换模块完成格式转换,并使用先进先出队列(first in first out, FIFO)进行临时存储。随后,数据通过AXI Full总线传输至DDR4内存中作为临时缓存。在数据存储模块中,DDR4中的数据通过AXI CDMA传输到双端口BRAM。为了实现高效、稳定的数据写入,系统设计了一个基于FPGA的SATA控制器。该存储链路充分利用了SATA 3.0接口的高带宽优势,实现了接近SSD的最大性能表现。MicroBlaze处理器<sup>[17]</sup>作为系统的核心控制单元,负责管理数据流及控制指令的执行。它通过通用异步收发传输器(universal asynchronous receiver-transmitter, UART)接口与外部设备进行通信,并协调DDR、SATA控制器及以太网模块的高效运行。以太网通信模块支持通过RGMII接口将采集到的图像数据实时传输至上位机。结合基于C#开发的上位机软件,可以实现图像的接收与显示功能。

## 2 FPGA逻辑设计

### 2.1 Camera Link串转并模块设计

针对Camera Link格式的数据输入接口,传统方法通常采用专用串并转换芯片来实现。这类方案尽管功能稳定,但需要占用大量FPGA IO资源,并依赖高引脚数FPGA夹层卡接口,这在某些应用场景中存在局限性。例

如,在 Full 模式下,使用传统的串并转换芯片需要多达 76 个 IO 口,这极大地限制了系统的灵活性和扩展能力。为了解决这些问题,本文基于 FPGA 逻辑设计,利用 LVDS 接口直接实现了 Camera Link 格式的数据接收和串转并处理,显著减少了对外部器件的依赖,提高了系统的灵活性和可扩展性。

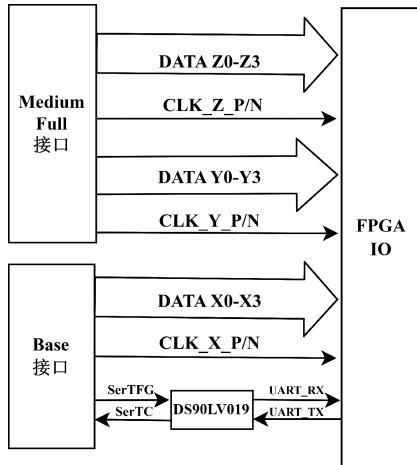

图 2 展示了 Camera Link 接口的框图。系统通过 Base 和 Full 接口接收 Camera Link 格式的数据流,其中时钟差分信号(CLK\_X\_P/N,CLK\_Y\_P/N,CLK\_Z\_P/N)用于同步数据传输,数据差分信号(DATA\_X0-X3,DATA\_Y0-Y3,DATA\_Z0-Z3)负责高速数据传输。

图 2 Camera Link 接口框图

Fig. 2 Camera Link interface block diagram

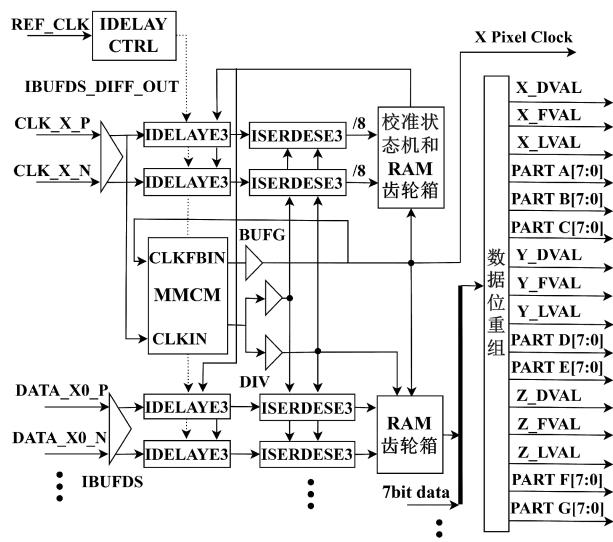

图 3 呈现了 Camera Link 串行到并行转换模块的框图。为确保数据接收的准确性,系统采用 IDELAYE3 原语对数据线进行精确延迟调整,并结合主从延迟校准机制优化采样点位置,从而保证在高速传输环境下的数据完整性。

图 3 串转并模块框图

Fig. 3 Serial-to-parallel conversion module block diagram

解串过程由 ISERDESE3 原语完成。ISERDESE3 以 1:8 DDR 模式将高速串行数据转化为并行数据流,并结合 8:7 比例的分布式 RAM 齿轮箱模块实现数据流的对齐与格式转换。系统使用到 3 个时钟域:1/2 速率的采样时钟、1/8 速率的解串时钟以及 1/7 速率的像素时钟。这些时钟信号由接收时钟经过 MMCM 生成,确保了采样时钟满足 VCO 频率范围,同时减少了解串模块时钟输入间的偏移,提升了系统的时钟稳定性。

在完成解串和初步对齐后,齿轮箱利用像素时钟对数据进行进一步对齐和统一广播,每条差分数据通道输出 7 位相机数据。随后,数据重组模块将齿轮箱输出的数据按照 Camera Link 协议要求进行重新排列,生成完整的像素数据及有效信号,包括 X\_DVAL、X\_FVAL、X\_LVAL、PART\_A[7:0] 等。本文通过这种设计仅需 30 个 IO 口即可实现 Full 模式的 Camera Link 数据接收,相较于传统方案节省了超过 60% 的 IO 资源。该模块的设计不仅满足了 Camera Link 协议的严格要求,还通过优化资源使用和数据路径设计,实现了高帧率、高分辨率的图像采集能力,为高速图像采集系统提供了一种高效且可靠的解决方案。

## 2.2 数据读取模块设计

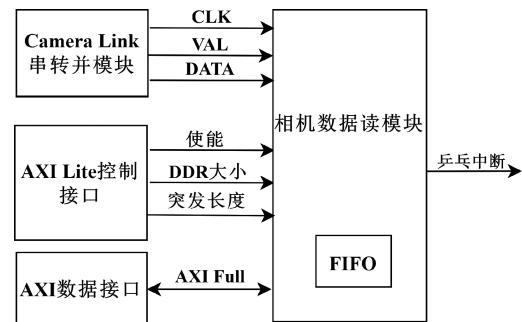

如图 4 所示,本文设计了相机数据读取模块,旨在高效接收来自相机的高速图像数据流,并将其可靠地传输至 DDR 存储器中。模块整体架构包括数据读取模块、FIFO 缓冲区、AXI Lite 控制接口和 AXI Full 数据接口。

图 4 相机数据读取模块框图

Fig. 4 Camera data reading module block diagram

在数据接收时,串转并模块将相机发送的高速串行数据转换为并行格式后输入至 FIFO 缓冲区。为了确保 FIFO 写入的数据始终以完整帧为单位,模块引入帧同步信号与写入使能信号的联合控制逻辑。当 MicroBlaze 发送的使能信号有效且帧同步信号处于帧间隙状态时,写入控制信号被置为高电平,允许数据写入;而一旦使能信号失效,写入操作立即停止,从而有效避免因上一帧未结束而导致的数据不完整问题。

与此同时, MicroBlaze 通过 AXI Lite 控制接口完成对模块的配置,包括设定 DDR 存储器的访问地址、突发传输长度等,并通过中断机制实时监控数据传输状态。数据读取按照预设的突发传输规则,由 AXI 数据接口从 FIFO 缓

冲区中高效提取数据并写入DDR存储器。在此过程中,系统采用乒乓操作机制,使得数据传输与存储能够并行进行,进一步提升了系统吞吐能力。每当一批数据成功存储至DDR后,系统触发中断信号通知MicroBlaze,后者据此更新计数器并准备下一轮的数据读取和传输。

### 2.3 SATA控制器

SATA控制器的设计旨在提供一个易于使用的接口,直接连接高带宽、非易失性存储系统。

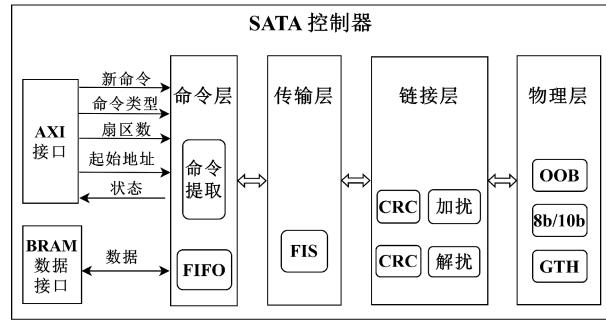

#### 1) SATA控制器接口和模块

本文在设计中实现了SATA通信协议的链接层、传输层和命令层。SATA协议的物理层通过Xilinx GTH高速收发器(UltraScale)的封装实现。SATA控制器通过AXI Lite接口接收来自MicroBlaze的控制指令,并通过外部双端口BRAM进行数据交换。图5展示了SATA控制器的功能框图。

图5 SATA控制器框图

Fig. 5 SATA controller block diagram

文献[14]提出的方案虽然实现了SATA 3.0存储系统,但在灵活性和可扩展性上存在不足。为了提高系统的灵活性和整体性能,本文定义了AXI接口和配置寄存器,用于接收来自MicroBlaze的配置信息。这使得MicroBlaze能够通过读写寄存器以及接受中断的方式,灵活地对SATA控制器进行配置和状态监控。

命令层使用有限状态机(finite state machine,FSM)实现了ATA命令集的一个子集,包括Read DMA Ext、Write DMA Ext、FPDMA Read、FPDMA Write、Set Features和Identify Device等命令。命令层解析读/写请求并向传输层发出相应的扇区操作指令。每个命令执行涉及一系列帧信息结构(frame information structure,FIS)的交换。传输层构建和分解由命令层请求的FIS,传递命令、数据、状态和控制信息。用户参数(如命令类型、扇区地址和扇区数量)根据ATA格式封装。传输层FSM解码FIS并检查ATA状态和错误字段中的错误。

链接层主要负责根据帧传输协议对每个FIS进行构架和交付。它使用特殊的控制字(称为原语)管理帧流和构造。传输层FSM创建命令FIS并将其存储在FIS传输缓冲区中,然后请求链接层FSM处理。链接层RX和TX

FSM负责帧的构造和去构架过程。TX FSM读取FIS缓冲区,计算32位CRC,并将其附加到帧负载末尾。接着添加SOF(帧开始)和EOF(帧结束)原始符号以标记帧边界。为了防止电磁干扰,帧需要通过扰频电路。扰频是通过将要传输的数据与线性反馈移位寄存器的输出进行异或运算来实现的。

GTH高速收发器负责数据的串行化/解串行化以及8b/10b编码/解码。在建立数据通信链路之前,SATA协议要求通过OOB信号重置、同步和初始化链路。OOB功能通过FPGA逻辑实现。

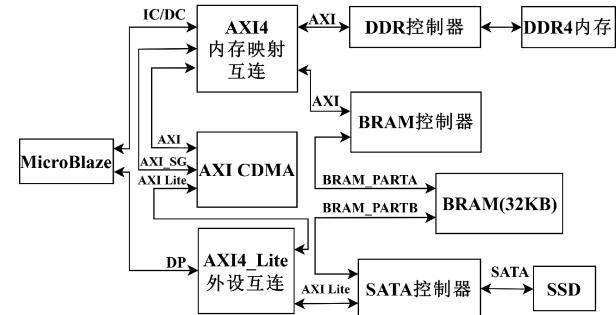

#### 2) SATA数据流传输控制

在设计SATA存储系统的FPGA实现中,数据传输流程是一个关键组成部分,它确保了从DDR内存到SATA硬盘的数据高效且可靠的移动。该部分通过整合多种硬件模块和接口,包括AXI CDMA控制器、双端口BRAM以及SATA控制器,实现了优化的数据流管理。DDR至SATA的数据路径框如图6所示。

图6 DDR至SATA的数据路径框图

Fig. 6 Data path from DDR to SATA block diagram

当需要将数据从DDR内存转移到SATA硬盘时, MicroBlaze处理器会发起一个读取请求至AXI CDMA控制器。AXI CDMA控制器负责处理与DDR4内存之间的高速数据传输,并将所获取的数据暂存于内部的BRAM之中。此BRAM被配置为乒乓缓冲结构(PART A和PART B),以支持连续的数据流而不会造成瓶颈。在一个BRAM部分(PARTA)接收来自DDR4内存的新数据的同时,另一个部分(PARTB)可以并发地向SATA控制器的应用层FIFO发送之前接收到的数据。这种乒乓机制极大地提高了数据吞吐量,减少了等待时间。

一旦数据到达应用层FIFO,它们就会按照SATA协议规范经过一系列处理步骤,这些步骤涵盖了从物理层到链路层再到传输层等不同层面的操作,确保数据格式正确无误并准备好进行传输。随后,处理完毕的数据通过SATA接口最终写入到连接的SATA硬盘上。

对于相反方向的数据读取过程,其基本原理相同,只是数据流动的方向是从SATA硬盘开始,依次经过SATA控制器的不同层级处理后进入BRAM,再经由AXI CDMA控制器返回到DDR内存,最后由MicroBlaze处理器进行

处理或进一步操作。

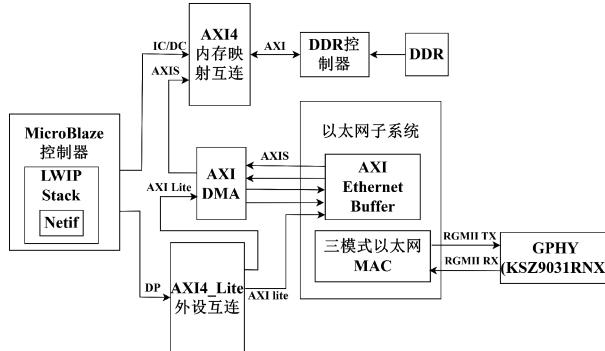

## 2.4 以太网数据导出模块

以太网<sup>[18]</sup>数据导出模块是用于将从硬盘导出的数据高效地传输到外部网络的关键组件。图 7 展示了一个以太网数据导出模块的框图,描述了通过 Xilinx 提供的 AXI 1 G Ethernet Subsystem IP 从 DDR 中导出数据的过程。MicroBlaze 处理器利用 LWIP 协议栈实现用户数据报协议 (user datagram protocol, UDP) 协议,用于实时数据导出。

图 7 以太网数据导出模块框图

Fig. 7 Ethernet data export module block diagram

MicroBlaze 控制器负责整体控制和协调各个模块的工作,包括配置和状态监控。AXI DMA 实现数据在 DDR4 存储器和 AXI Ethernet Subsystem 之间的高效传输。AXI Ethernet Subsystem 包含 AXI Ethernet Buffer,用于缓冲待发送的数据,并与 MAC 层进行交互。Tri-Mode Ethernet MAC 支持多种物理层接口(如 RGMII),负责数据帧的封装和解封装。物理层接口通过 RGMII 接口与外部的 KSZ9031RNX 以太网物理层芯片通信,实现高速串行数据传输,连接到外部网络设备。

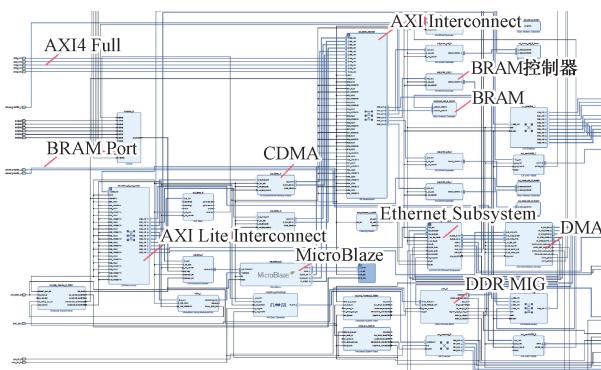

## 2.5 Block Design 设计

图 8 展示了在 Vivado 中设计的完整 Block Design,该设计集成了多个 Xilinx 提供的 IP 核,如 MicroBlaze、DDR4 MIG、AXI Ethernet Subsystem、AXI DMA 等,并实现了与 SATA 控制器和数据读取模块通信的接口。

图 8 Block Design 设计图

Fig. 8 Block Design diagram

## 3 软件设计与实现

本章节将详细介绍整个系统的软件设计,包括 MicroBlaze 嵌入式系统的开发以及上位机软件的开发。具体涵盖了简单文件系统、数据流控制、读写控制和文件管理、以及图像数据回放等方面。

### 3.1 MicroBlaze 软件开发

为了克服现有方案在灵活性和可扩展性方面的不足,本文创新性地采用了 MicroBlaze 软核来灵活配置和管理 SATA 控制器。

#### 1) 简单文件系统

为了支持高效的数据存储和管理,本文在 MicroBlaze 上实现了一个轻量级的文件系统。该文件系统旨在提供基本的文件操作功能,如创建、删除、读取和写入文件,同时保持较低的资源占用率,以适应嵌入式环境的需求。

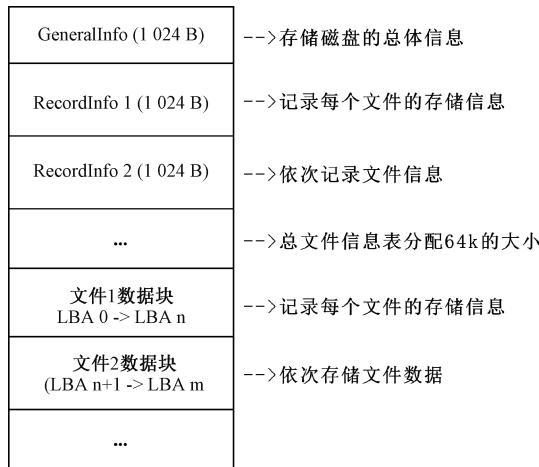

文件系统的设计围绕两个核心部分展开:文件表区域和数据区域。文件表区域用于描述磁盘的整体状态和每个文件的具体信息;数据区域则用于实际存储文件内容。具体来说,文件表区域包括磁盘信息(表 1)和文件记录信息(表 2),而数据区域则从逻辑块地址 0 (logical block addressing, LBA) 开始,依次存储各个文件的数据。

表 1 磁盘信息

Table 1 Disk information

| 包含字段                | 内容          |

|---------------------|-------------|

| DiskTotalSectors    | 磁盘总扇区数      |

| DiskRemainSectors   | 剩余扇区数       |

| DiskNextStartLba    | 下一个文件起始 LBA |

| DiskInitializedFlag | 文件系统是否初始化标志 |

| Checksum            | 校验和         |

| Reserved            | 保留字段        |

表 2 文件记录信息

Table 2 File record information

| 包含字段              | 内容         |

|-------------------|------------|

| Id                | 文件记录的唯一标识符 |

| Index             | 文件在表中的索引号  |

| DiskStartLba      | 文件起始扇区地址   |

| DiskSectorCount   | 文件所占用的扇区数  |

| record_start_time | 文件记录的开始时间  |

| record_stop_time  | 文件记录的结束时间  |

| ExistFlag         | 文件存在标志     |

| StopFlag          | 文件结束标志     |

| Reserved          | 保留字段       |

磁盘信息结构涵盖了磁盘总扇区数、剩余可用扇区数、下一个文件起始 LBA、文件系统初始化标志、校验和以及

保留字段。这些信息确保了文件系统的初始化状态被正确记录,并且能够通过校验和验证数据完整性。

文件记录信息详细描述了每个文件的唯一标识符、索引号、起始LBA、占用的扇区数、记录的开始和结束时间、存在标志、结束标志及保留字段。这些信息使得文件可以被精确地定位、管理和访问。

图9展示了整个磁盘的布局,包括1 024字节的GeneralInfo用于存储磁盘总体信息,多个1 024字节的RecordInfo用于记录文件信息,总共分配了64 KB的空间来存储文件信息表。文件数据从LBA 0开始依次存储,每个文件根据其起始LBA和占用的扇区数进行定位和访问。

图9 SATA 盘内容组成

Fig. 9 Composition of SATA disk content

文件系统操作流程简化为几个关键步骤:文件创建时分配新的记录并更新下一个文件起始LBA;文件删除时标记记录为无效并释放空间;文件读取和写入操作基于记录中的起始LBA和占用的扇区数进行;错误处理机制利用校验和字段验证数据完整性,同时保留字段为未来扩展预留空间。

通过这种设计,MicroBlaze平台上的简单文件系统不仅提供了必要的文件操作功能,还保证了数据的可靠性和系统的稳定性,适用于需要高性能和低资源占用的应用场景。此文件系统在满足嵌入式系统特定需求的同时,也确保了高效的磁盘空间管理和数据传输性能。

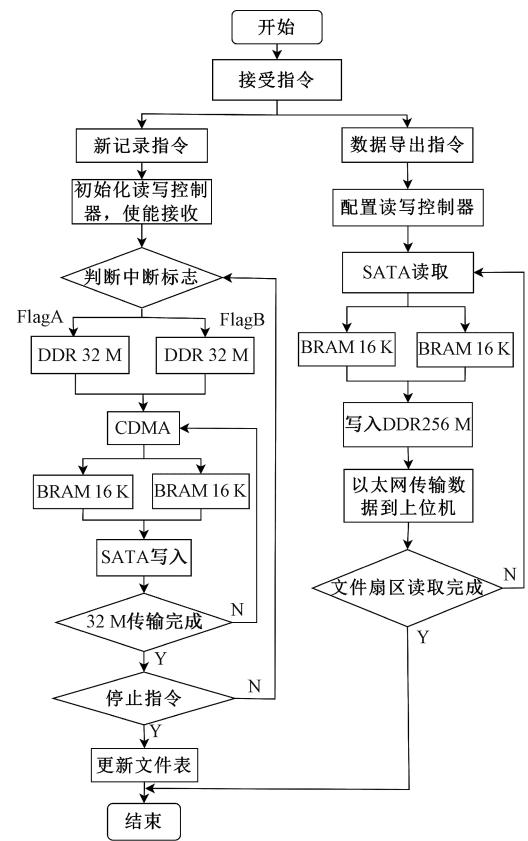

## 2)数据流控制

为了确保数据在MicroBlaze系统中的高效传输和处理,设计了一套集成乒乓传输技术的数据流控制系统。该系统的指令读取和数据流控制流程如图10所示。

在接收新记录指令时,数据首先被写入DDR 32 M或DDR 64 M缓冲区;当这些缓冲区达到半满或全满状态时,触发中断信号(如FlagA或FlagB),通知MicroBlaze处理器有新数据待处理。MicroBlaze接收到中断后,使用CDMA技术将数据快速传输到双端口32 K BRAM缓冲区,每次操作16 K的数据量。BRAM的乒乓机制确保一

图10 指令读取和数据流控制

Fig. 10 Command reading and data flow control

边接收新数据,另一边同时传输已有数据给SATA控制器模块,最终写入SATA盘中进行长期存储。这一过程是循环进行的,确保了即使在大量数据涌人的情况下,也能维持高效的数据流控制和处理能力。

对于数据导出指令,系统配置读写控制器准备数据导出操作。它执行SATA读取操作,将数据从SATA存储读取到其中一个16 K BRAM缓冲区,再通过CDMA机制快速传输到DDR 256 M。随后,数据通过以太网接口传输到上位机。

## 3.2 上位机软件开发

为了进一步增强系统的易用性和人机交互体验,本文专门设计了上位机软件。该软件不仅支持磁盘和文件管理操作,还提供了一系列调试工具,便于系统的维护和优化。

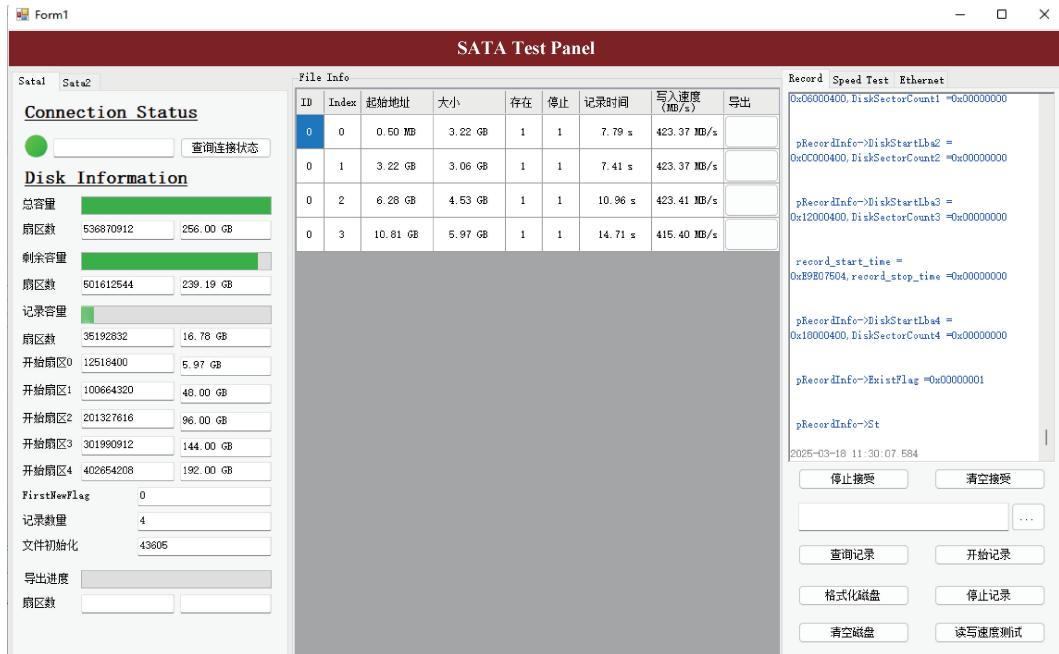

### 1)读写控制和文件管理

上位机的SATA测试面板提供了一个直观且功能丰富的界面,用于管理和监控磁盘及文件操作。该界面集成了磁盘信息显示、文件列表管理、读写控制指令以及UART调试窗口,可以方便地执行各种操作并进行系统调试。上位机控制界面如图11所示。

该界面主要分为几个关键区域:

(1)磁盘信息:显示磁盘的总容量、已用空间和剩余空间等基本信息,帮助用户了解当前存储状况。

图 11 上位机控制界面

Fig. 11 Host computer control interface

(2)文件列表:列出所有文件的详细信息,包括文件ID、名称、大小、状态(如是否可读、是否可写)以及记录时间等,方便用户查看和管理文件。

(3)读写控制指令:通过一组按钮,用户可以轻松启动或停止数据记录、读取和写出操作,还可以格式化磁盘或清除缓存,确保磁盘处于最佳工作状态。

(4)UART 调试窗口:显示调试信息和命令响应,帮助技术人员实时监控系统状态并进行必要的调试,确保系统的稳定运行。

此外,界面还包括连接状态指示,确保数据传输的稳定性;以及以太网接口状态显示,支持远程管理和监控功能。整个界面设计旨在为用户提供一个高效、直观的操作平台,适用于需要高带宽和实时性要求高的应用场景。

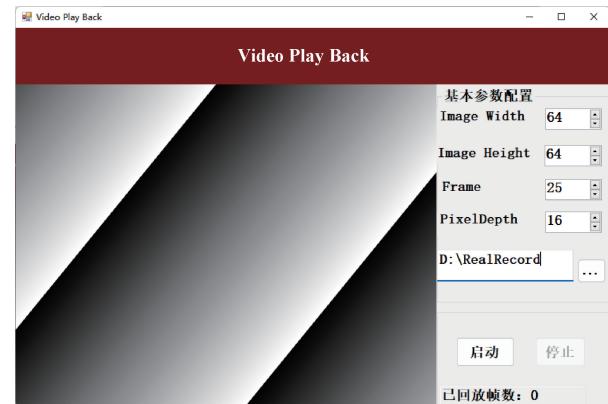

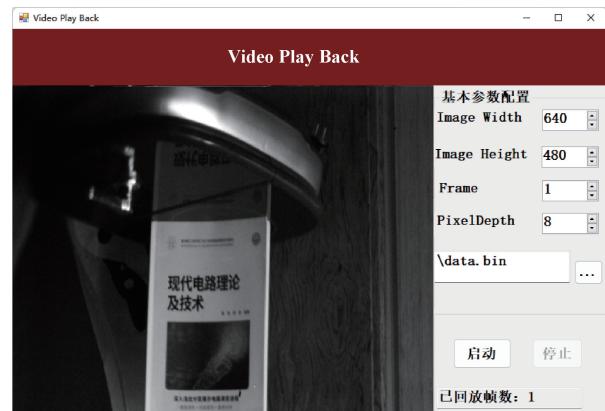

## 2)图像数据回放

图 12 展示的是一个图像回放界面,用于播放和管理录制的图像数据。该界面简洁直观,提供了关键功能以设置图像参数、控制回放操作以及配置文件路径。

图 12 左侧显示当前回放的图像,右侧包含多个设置选项:可以设置图像宽度和高度、帧率以及像素深度,这些参数分别影响图像的尺寸、播放速度和质量;文件路径输入框允许用户指定要回放的图像文件位置;启动和停止按钮用于控制回放操作;状态信息栏显示已回放的帧数,了解回放进度。

## 4 系统验证和分析

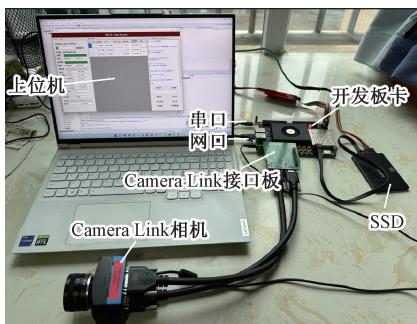

系统测试环境如图 13 所示。测试平台采用黑金的

图 12 图像回放界面

Fig. 12 Image playback interface

AXKU040 板卡,搭载 Xilinx Ultrascale FPGA(型号为 XCKU040),并使用 Xilinx Vivado Design Suite 2 020.2 作为开发环境。图像采集使用 EoSens 3.0 CL 相机,存储介质选用三星 870 EVO SSD 固态硬盘。该 SSD 通过 SATA 3.0 接口连接,其写入最大速率为 530 MB/s,读取最大速率为 560 MB/s,完全满足设计需求。

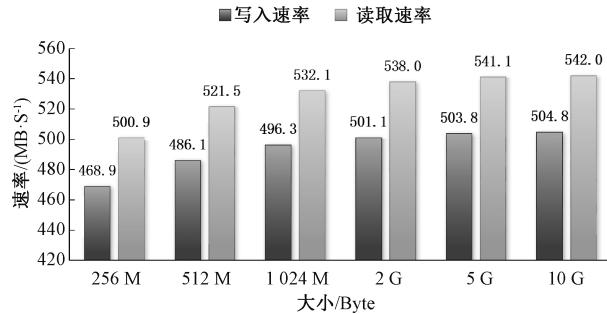

### 4.1 SATA 控制器速率测试

SATA 控制器性能测试通过嵌入在 MicroBlaze 处理器中的软件代码实现。测试过程中,本文记录了从开始向 SATA 硬盘写入数据到完成写入的时间戳,并以此计算实际的写入速率。同样地,对于读取操作,记录了从发出读取指令到接收到全部数据的时间。为了验证性能的稳定

图 13 系统测试环境

Fig. 13 System testing environment

性,在多个存储大小下分别做了十次的写入和读取的操作。实验结果如图 14 所示,在最佳条件下,硬盘的最大连续写入平均速率为 504.8 MB/s,读取速率为 542.0 MB/s。这些测量值反映了 SATA 协议控制器的有效实现以及与硬盘的良好稳定性。

图 14 SATA 控制器速率测试

Fig. 14 SATA controller rate test

#### 4.2 存储性能对比

为了全面评估本系统 SATA 控制器的性能,将其与现有的几种典型方案进行了对比测试。表 3 展示了不同方案在写速率和读速率上的性能差异。

表 3 存储系统性能对比

Table 3 Storage system performance comparison

| 方案     | 写速率/<br>(MB·s <sup>-1</sup> ) | 读速率/<br>(MB·s <sup>-1</sup> ) | 存储介质       |

|--------|-------------------------------|-------------------------------|------------|

| 文献[11] | 44.8                          | —                             | Nand Flash |

| 文献[14] | 473.0                         | 435.0                         | SATA SSD   |

| 文献[16] | 569.1                         | 523.8                         | SATA SSD   |

| 本文系统   | 504.8                         | 542.0                         | SATA SSD   |

从表 3 中可以看出,文献[11]采用了 Nand Flash 作为存储介质,在写入速度上明显低于基于 SATA SSD 的其他方案。文献[14]和文献[16]均使用了 SATA SSD 作为存储介质,显示出了较高的传输速率。特别是文献[16],在写速率和读速率方面都表现出色,分别达到了 569.1 MB/s 和 523.8 MB/s。相比之下,本系统实现了高达 504.8 MB/s

的写速率和 542.0 MB/s 的读速率,接近 SATA 3.0 接口的理论极限。尽管本系统的写速率略低于 Niwase 方案,但在读速率上却表现更优。此外,本系统的设计注重了灵活性和适应性,通过集成 MicroBlaze 处理器和轻量级文件系统,提供了更友好的用户界面和更强的功能扩展能力。

#### 4.3 相机数据采集及验证

相机数据采集功能的验证是通过上位机软件回放经由以太网导出的数据来完成的。在测试中,首先配置相机以 Full Camera Link 模式运行,实现了高达 400 MB/s 的数据采集速率。接着,通过以太网模块将采集到的图像数据实时传输至上位机,并利用上位机上的专用播放软件对图像序列进行回放。回放图像如图 15 所示,图像未发现任何差异或失真现象,证明了系统的高效性和可靠性。

图 15 图像采集回放

Fig. 15 Image acquisition and playback

## 5 结 论

本文设计并实现了一种基于 FPGA 的高速图像采集与存储系统,通过 FPGA 原生 LVDS 接口解析 Camera Link 协议,结合自主设计的 SATA 3.0 控制器与 AXI CDMA 乒乓缓冲机制,实现了高效的数据传输链路。系统支持 400 MB/s 的图像采集速率,实测 SATA 硬盘连续写入速率达 504.8 MB/s,读取速率达 542.0 MB/s,接近 SATA 3.0 理论极限。集成轻量级文件系统与以太网模块,支持文件级操作与实时数据导出。实验结果表明,系统在高速、大容量场景下具有优异的稳定性与可靠性。

#### 参考文献

- [1] 刘静军,贺小军,王鹏,等.星载多模式和多通道图像采集与处理[J].电子测量技术,2023,46(20):30-35.

LIU J J, HE X J, WANG P, et al. Spaceborne multi-mode and multi-channel image acquisition and processing[J]. Electronic Measurement Technology, 2023, 46(20):30-35.

- [2] 任丽畔,汪晨.基于FPGA的Camera Link接口设计[J].长春大学学报,2022,32(4):11-15.

- REN L Y, WANG CH. Design of camera link interface based on FPGA[J]. Journal of Changchun University, 2022, 32(4):11-15.

- [3] QIN J, WANG K, LI X, et al. A software defined high-speed cameraLink image data transmission system based on pixel clock recovery[J]. Automatic Control and Computer Sciences, 2022, 56 (5): 403-410.

- [4] 甄国涌, 丁润琦, 张凯华. 基于 Camera Link 的高可靠性图像数据传输设计[J]. 仪表技术与传感器, 2021(1): 43-47.

- ZHEN G Y, DING R Q, ZHANG K H. Design of high reliability image data transmission based on camera link[J]. Instrument Technique and Sensor, 2021(1):43-47.

- [5] 王晨, 马游春, 郭鑫. 基于 DDR3 的大容量数据缓存与传输系统设计[J]. 仪表技术与传感器, 2024,(12): 71-74,79.

- WANG CH, MA Y CH, GUO X. Design of large capacity data cache and transmission system based on DDR3 [J]. Instrument Technique and Sensor, 2024,(12):71-74,79.

- [6] 赵冬青, 孟宇航. 基于 FPGA 的高速图像采集传输系统[J]. 计算机与数字工程, 2023, 51 (8): 1861-1863,1923.

- ZHAO D Q, MENG Y H. High speed image acquisition and transmission system based on FPGA[J]. Computer and Digital Engineering, 2023, 51 (8): 1861-1863,1923.

- [7] 刘宇宇, 范永杰. 基于 FPGA 和 USB3.0 的高速 CameraLink 图像采集[J]. 软件, 2022, 43 (9): 176-179.

- LIU Y Y, FAN Y J. High speed CameraLink image acquisition based on FPGA and USB3.0 [J]. Software, 2022, 43(9):176-179.

- [8] 邢震震, 苏淑婧, 梁文科, 等. 基于 FPGA 高精度  $\Delta$ - $\Sigma$ ADC 温度采集存储系统设计[J]. 电子测量技术, 2022, 45(8):21-26.

- XING ZH ZH, SU SH J, LIANG W K, et al. Design of high precision  $\Delta$ - $\Sigma$ ADC temperature acquisition and storage system based on FPGA [J]. Electronic Measurement Technology, 2022, 45(8):21-26.

- [9] 杨成禹, 庄晓奇. 基于 ARM 的图像采集与传输系统设计[J]. 电子测量技术, 2015, 38(12):59-62.

- YANG CH Y, ZHUANG X Q. Design of image acquisition and transmission system based on ARM[J]. Electronic Measurement Technology, 2015, 38(12): 59-62.

- [10] 段梦月, 赵宏亮. 微型 CMOS 图像采集存储系统设计[J]. 仪表技术与传感器, 2021(9):78-81,86.

- DUAN M Y, ZHAO H L. Design of miniature CMOS image acquisition and storage system[J]. Instrument Technique and Sensor, 2021(9):78-81,86.

- [11] 王子懿, 沈三民, 杨峰, 等. 基于 FPGA 的高速大容量存储与传输系统[J]. 电子测量技术, 2021, 44(13):150-155.

- WANG Z Y, SHEN S M, YANG F, et al. High speed and large capacity storage and transmission system based on FPGA[J]. Electronic Measurement Technology, 2021, 44(13):150-155.

- [12] 台运娇, 江先阳. SATA3.0 物理层设计与实现[J]. 信息技术, 2019(10):121-125,130.

- TAI Y J, JIANG X Y. Physical layer design and implementation of SATA3.0 [ J ]. Information Technology, 2019(10):121-125,130.

- [13] 林建华, 吴绪玲. 基于 FPGA 存储阵列的优化设计与实现[J]. 电子技术应用, 2023, 49(4):111-116.

- LIN J H, WU X L. Optimized design and realization of storage array based on FPGA[J]. Application of Electronic Technique, 2023, 49(4):111-116.

- [14] 朱彦铭, 刘文重, 吕雨桦, 等. 卫星高性能存储数传一体化系统关键技术及应用[J]. 电子测量技术, 2024, 47(24):93-102.

- ZHU Y M, LIU W ZH, LYU Y H, et al. Key technologies and applications of integrated high-performance storage and data transmission system for satellites [J]. Electronic Measurement Technology, 2024, 47(24):93-102.

- [15] 李晋涛, 任勇峰, 杨志文, 等. 基于 SATA3.0 的存储系统优化设计[J]. 电子技术应用, 2021, 47 (1): 86-90.

- LI J T, REN Y F, YANG ZH W, et al. An optimized design of a storage system based on SATA3.0 [J]. Application of Electronic Technique, 2021, 47 (1): 86-90.

- [16] NIWASE R, HARASAWA H, YAMGUCHI Y, et al. A cost/power efficient storage system with directly connected FPGA and SATA disks[C]. 2023 IEEE 16th International Symposium on Embedded Multicore/ Many-core Systems-on-Chip ( MCSoC ). IEEE, 2023, 51-58.

- [17] 王忆夏, 焦凯强. 基于 MicroBlaze 的激光告警最小处理系统设计[J]. 激光与红外, 2024, 54(6):915-919.

- WANG Y X, JIAO K Q. Minimal processing system design of laser alarm based on MicroBlaze [ J ]. Laser & Infrared, 2024, 54(6):915-919.

- [18] 刘文元, 刘伟. 基于 MicroBlaze 的以太网卡芯片功能测试方法[J]. 中国集成电路, 2023, 32(12):91-95.

- LIU W Y, LIU W. Function test method for the ethernet card IC based on MicroBlaze [ J ]. China Integrated Circuit, 2023, 32(12):91-95.

## 作者简介

王振, 硕士研究生导师, 主要研究方向为新型半导体材料与器件物理研发、电路与系统。

E-mail: wangzhen@cqupt.edu.cn

黄春平(通信作者), 硕士研究生, 主要研究方向为嵌入式技术、电路与系统。

E-mail: 244806128@qq.com

陈威威, 博士, 硕士生导师, 主要研究方向为电路与系统。

E-mail: chenww@cqupt.edu.cn