# QFN 封装器件应用电路谐振分析与解决方法研究

田 腾 王志奎 刘亚旭 崔 彭 王培阳

(南京电子设备研究所 南京 210000)

**摘要:** 本文基于某款 QFN 封装器件在 Ku 频段应用时出现谐振现象, 导致电路出现 3 dB 以上的电路插损, 造成电路平坦度严重恶化, 根据该现象开展电路谐振分析并探究解决方案。本文对 3 种类型缺陷地结构共面波导的射频特性和等效电路进行理论分析, 并基于共面波导理论, 使用 CST 仿真软件对提出的第三类缺陷地结构的结构参数及传输线两端接地面空腔对传输线特性影响进行仿真分析。研究表明, QFN 封装器件的射频输出引脚易和周围引脚及周围接地面形成含有缝隙的缺陷结构共面波导, 使电路等效引入了一个 LC 并联谐振电路。并且缺陷地结构共面波导的空腔长度  $l$ , 空腔宽度  $w$ , 缝隙宽度  $g$ , 缝隙离空腔的边壁距离  $d$  及传输线两端接地面空腔同时出现对传输线特性均会造成影响, 使电路易在低频段出现谐振点。本文对电路进行优化设计, 通过去除电路中等效的缺陷地共面波导结构中的缝隙  $g$ , 有效消除谐振现象。本文通过理论和仿真分析采取的去除谐振现象的手段和电路设计方法, 有效提高微波带内的平坦度, 该方法在现代高密度集成的第四代微波电路设计中有广泛的借鉴作用。

**关键词:** 共面波导; 谐振; QFN 封装; 等效电路

中图分类号: TN702 文献标识码: A 国家标准学科分类代码: 510.1025

## Investigation on resonance analysis and solution of QFN-packaged device applications

Tian Teng Wang Zhikui Liu Yaxu Cui Peng Wang Peiyang

(Nanjing Electronic Equipment Research Institute, Nanjing 210000, China)

**Abstract:** This paper is based on the resonance phenomenon of a square flat no leads package device when it is applied in Ku band, which leads to circuit insertion loss of more than 3dB and serious deterioration of circuit flatness. Based on this phenomenon, circuit resonance analysis is carried out and solutions are explored. In this paper, the RF characteristics and equivalent circuit of coplanar waveguide with three types of defected ground structures are theoretically analyzed. Based on the coplanar waveguide theory, the structural parameters of the third type of defected ground structure and the characteristics of the transmission line with ground cavities at both ends of the transmission line are simulated and analyzed by CST simulation software. The research shows that the RF output pin of QFN package device is easy to form a defective coplanar waveguide with gaps with the surrounding pins and the surrounding ground, which makes the circuit equivalent to an LC parallel resonant circuit. In addition, the length of cavity  $l$ , the width of cavity  $w$ , the width of gap  $g$ , the distance from the gap to the side wall of the cavity  $d$  and the simultaneous presence of cavities at both ends of the transmission line will affect the characteristics of the transmission line, making the circuit prone to resonant points in the low frequency band. In this paper, the circuit is optimized and the resonance phenomenon is effectively eliminated by removing the gap  $g$  in the equivalent defect ground coplanar waveguide structure in the circuit. Then the method of eliminating resonance phenomenon and circuit design method adopted through theoretical and simulation analysis can effectively improve the flatness in the microwave band. This method can be widely used for reference in the design of modern high-density integrated fourth generation microwave circuits.

**Keywords:** coplanar waveguide; resonance; QFN-packaged; equivalent circuits

## 0 引言

现代微波通信、雷达、制导、电子测量仪器等各种电子

设备正快速发展, 其对微波电路的高密度集成、轻量化提出了更高的要求。随着异质半导体外延技术、硅通孔 (through Si vias, TSV) 为代表的垂直互联技术、以及介质

基板材料加工工艺的提升,以片上系统(system on chip, SOC)、封装级系统(system on package, SOP)和系统级封装(system in package, SIP)为代表的第四代微波集成电路<sup>[1-5]</sup>得到迅猛发展。在第四代微波集成电路中,SOC、SOP 和 SIP 的集成应用,能够显著提高电路系统的高密度集成及小型化发展。但是系统集成实现小型化的同时,微波电路面临着阻抗失配、信号串扰、电路谐振等复杂的电磁情况。

针对第四代微波电路的问题挑战,微波电路的设计对精确仿真提出更高的要求,需要设计工程师识别电路设计中的潜在风险。方形扁平无引脚封装(quad flat no-leads package, QFN)是一种常见的封装形式<sup>[6]</sup>,因其具有尺寸小、散热性能好、结构稳定等特点,在低频和数字电路中被广泛应用。而将 QFN 封装应用于微波频段时,若电路设计不当,未充分考虑射频输出端的阻抗匹配时,QFN 封装的射频信号输出引脚与非射频引脚之间将产生交叉影响,造成阻抗失配,使电路传输特性如平坦度、插损等,在一定的频段内引起显著的改变。QFN 引脚之间的阻抗失配对电路的影响往往作用在很窄的频段范围,当微波电路的工作频段不在受影响的范围内时,这种现象在微波集成电路的研究和应用中往往被忽视<sup>[7-9]</sup>。

本文对某款由 QFN 器件组成的第四代微波电路的实例电路进行仿真分析。该电路中出现的谐振现象引起超过 3 dB 的电路插损,造成电路平坦度严重恶化。电路出现阻抗失配、电路谐振等现象时,通常在信号输出通道中引入匹配单元、调节传输线阻抗等措施来完成电路匹配,此类方法需要对电路的输出匹配重新设计,电路设计周期变长,而本文基于共面波导理论对电路谐振产生的根源进行了详细研究,并提出消除电路中等效 LC 并联谐振的改进方法,该方法可以有效抑制电路谐振的产生,并在 QFN 器件在微波频段应用中有广泛的借鉴作用。

## 1 现象描述与分析

### 1.1 谐振现象

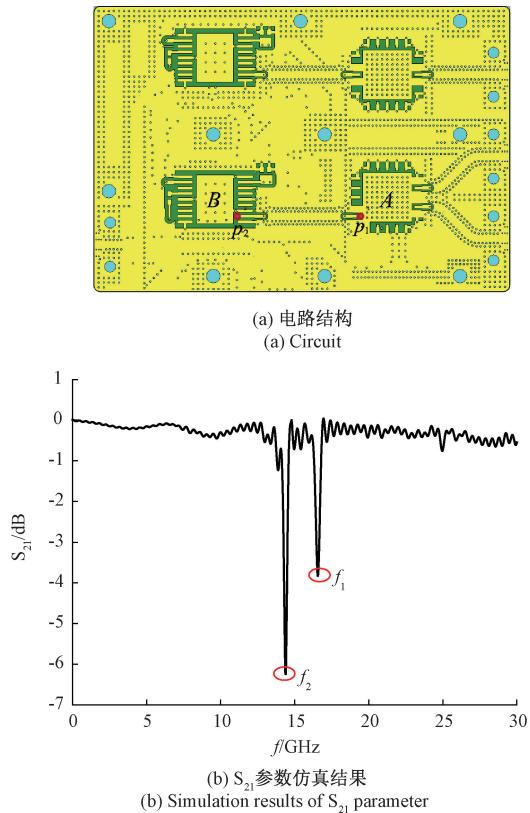

该款基于 QFN 封装的两种(A 和 B)SIP 在印制板 PCB 上的电路图如图 1(a)所示。为有效屏蔽信号串扰,电路板装配在铝制金属腔内,并且 PCB 上 A 型和 B 型 SIP 器件四周接地区域均与金属盒体紧密贴合,且仅在 SIP 器件上方留有高度 3 mm 的空气腔,用于放置器件,其电路工作在 10~20 GHz 范围内的 Ku 波段。A 型和 B 型 SIP 采用微带线转带状线的结构进行射频信号传递。

本文采用专业的电磁场仿真软件 CST 对该实例 PCB 电路板(如图 1(a)所示)进行半实物仿真分析,探究 A 型和 B 型 SIP 的 QFN 引脚端口  $p_1$  和  $p_2$  之间的  $S_{21}$  参数,仿真结果如图 1(b)所示,  $S_{21}$  参数曲线在 0~12.5 GHz 范围内趋于平缓;在 20~30 GHz 范围内有  $\pm 0.3$  dB 的波动,在 25 GHz 附近存在低插损谐振点;而在工作频段 12.5~

20 GHz 内,频率  $f_1$  和  $f_2$  附近出现强烈谐振,造成超过 3 dB 以上的插损恶化。频率  $f_1$  和  $f_2$  附近的高插损谐振将严重影响电路平坦度,因此本文将对该频段的谐振现象进行详细分析。

图 1 实例 PCB 电路

Fig. 1 Example of PCB circuit

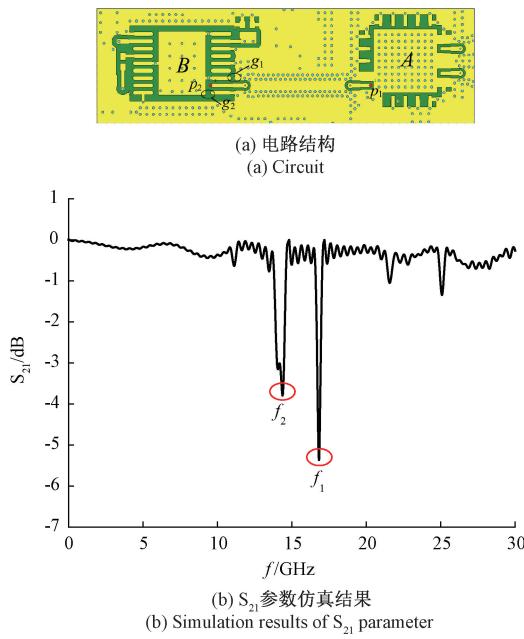

图 1(a)实例电路由电路器件和结构一致的上下两部分组成,选择下版部分区域电路作为典型区域(如图 2(a)所示)进行建模分析,电路上方设置高度为 3 mm 的空气腔,其中  $g_1$  和  $g_2$  表示器件 B 的引脚端口  $p_2$  的输出两端接地引脚与周围大面积参考地之间的缝隙。将该局部电路进行仿真,  $S_{21}$  参数仿真结果如图 2(b)所示,结果同图 1(b)趋势一致,电路在相同频率  $f_1$  和  $f_2$  附近依然存在严重谐振现象,同时在 11 GHz、21.5 GHz、25 GHz 附近存在低插损谐振点。

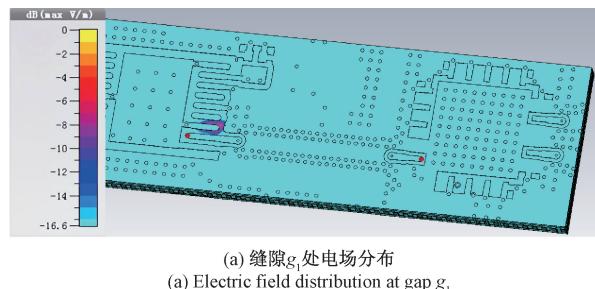

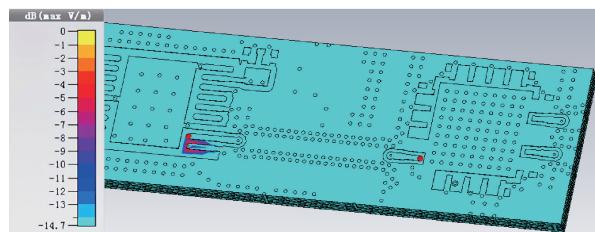

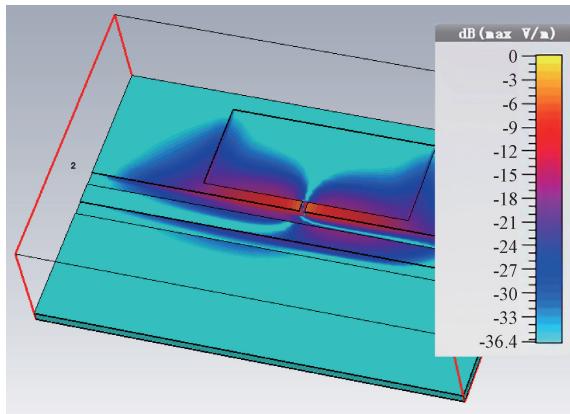

在三维电场仿真时,在谐振点  $f_1$  和  $f_2$  添加电场监控,关注电路间电场分布情况,以判断谐振发生区域。图 3(a)和图 3(b)分别为缝隙  $g_1$  和缝隙  $g_2$  处电场分布。由图 3(a)、(b)可知,缝隙  $g_1$  和缝隙  $g_2$  处电场强度高于其他区域,并且电场在缝隙  $g_1$  和缝隙  $g_2$  处形成驻留效应,导致信号在  $p_1$  和  $p_2$  之间无法有效传递,出现阻抗失配,从而引起电路的高插损谐振现象。利用同样的方法可知,11 GHz、21.5 GHz、25 GHz 的低插损谐振点,是由于重新建立模型时空气腔激起的高次模引起,本文研究忽略高次

图 2 重点关注区域电路

Fig. 2 Circuit in key focus areas

模的影响。由上述仿真分析可知, 电路中存在的高插损谐振是由电路结构引起, 因此, 本文就该问题对谐振产生原因开展研究分析。

(a) 缝隙 $g_1$ 处电场分布

(a) Electric field distribution at gap  $g_1$ (b) 缝隙 $g_2$ 处电场分布

(b) Electric field distribution at gap  $g_2$ 图 3 缝隙  $g_1$ 、 $g_2$  处的电场分布Fig. 3 Electric field distribution at gap  $g_1$  and  $g_2$

## 1.2 缺陷地共面波导结构射频特性与等效电路

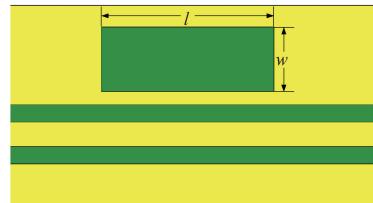

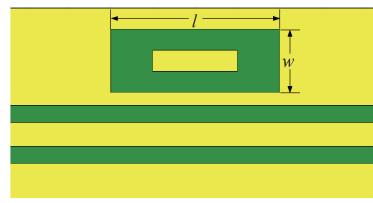

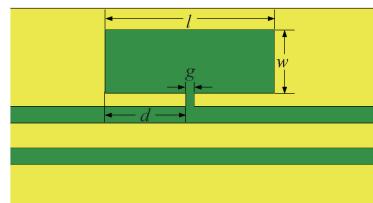

由于接地面上不同的缺陷结构将带来不同的传输特性差异, 因此本文将分析 3 种类型的缺陷地共面波导结构的射频特性, 如图 4(a)、(b)、(c) 所示。图 4(a) 中类型一为在共面波导接地面上一侧刻蚀出长度为  $l$ , 宽度为  $w$  的矩形空

腔, 图 4(b) 中类型二为在类型一的基础上, 在矩形空腔区域内添加非接地金属内导体, 图 4(c) 中类型三为在类型一的基础上, 矩形空腔区域在传输线的一侧切出宽度为  $g$  的缝隙。

(a) 类型一缺陷地共面波导

(a) Type 1 coplanar waveguide with defected ground(b) 类型二缺陷地共面波导

(b) Type 2 coplanar waveguide with defected ground(c) 类型三缺陷地共面波导

(c) Type 3 coplanar waveguide with defected ground

图 4 3 种类型缺陷地共面波导

Fig. 4 Three types of coplanar waveguides with defected ground

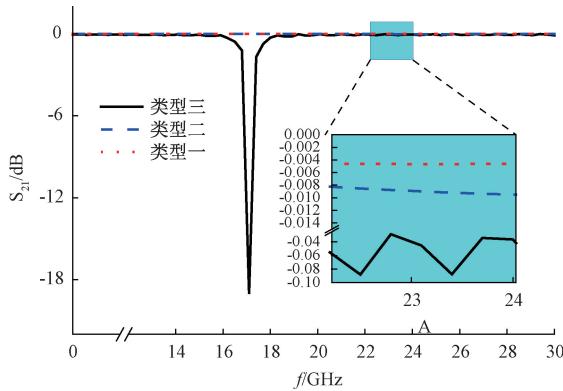

在 CST 软件中分别建立 3 种类型结构, 介质基板材料为睿龙科技 RA300B, 介电常数为 2.89, 厚度为 0.238 mm, 中间 50 欧姆传输线宽度 0.58 mm。当矩形空腔区域中  $l=5.8$  mm,  $w=2.5$  mm,  $g=0.16$  mm,  $d=2.82$  mm 时, 图 4 中 3 种不同缺陷地结构的  $S_{21}$  参数仿真结果如图 5 所示。由图 5 仿真结果可知, 在 0~30 GHz 的仿真频率范围内, 类型一和类型二缺陷地结构在相同频点的  $S_{21}$  参数曲线的差值在 0.004 dB 左右, 且波动可忽略, 均有良好的传输特性。类型三缺陷地结构在 17 GHz 附近出现插损大于 10 dB 的谐振点。

因此, 在图 4(c) 类型三的仿真模型中添加谐振频点的电场监控, 仿真结果如图 6 所示, 缝隙  $g$  处电场强度高于其他区域, 并且电场在缝隙处形成驻留效应, 因此缝隙  $g$  是造成电路谐振的主要原因。

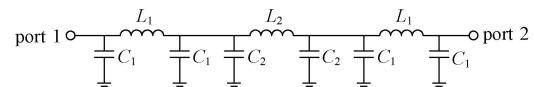

根据传输线及各类单元结构上的电流、电场、磁场分布随时间、频率、位置的变化, 无源传输线的电路特性可以用 RCL 电路进行等效表示<sup>[10]</sup>。完整非缺陷的共面波导传输线的中心导带和与传输线两端接地面之间等效为串联电感

图 5 三种类型  $S_{21}$  参数仿真结果Fig. 5 Simulation results of  $S_{21}$  parameters about three types图 6 类型三缝隙  $g$  处电场分布Fig. 6 Type 3 electric field distribution at gap  $g$

$L_1$  和并联电容  $C_1$ 。图 4(a)类型一的缺陷结构中,由于空腔区域的存在,造成电场的不连续,缺陷区域中心导带和接地面之间等效为串联电感  $L_2$  和并联电感  $C_2$ 。图 4(b)类型二的缺陷结构中,由图 5 中的  $S_{21}$  仿真结果已知空腔区域的非接地内导体对电场的影响很小,且类型一和类型二的仿真曲线几乎重合,因此中心导带和接地面之间的等效电路和类型一近似相等,依然等效为串联电感  $L_2$  和并联电感  $C_2$ 。而在图 4(c)类型三的缺陷地结构中,因为缝隙  $g$  的存在,不仅存在类型一和类型二中的串联电感  $L_2$  和并联电感  $C_2$ ,缝隙  $g$  和矩形空腔区域还等效为一个  $LC$  并联谐振电路,包含电容  $C_s$  和电感  $L_s$ 。因此类型一和类型二的等效电路<sup>[11-12]</sup>可以表示为图 7(a)所示,类型三的等效电路<sup>[13]</sup>为图 7(b)所示。根据图 7(b)的等效电路,由于缝隙  $g$  的引入,电路在缝隙处引入了额外的电容  $C_s$  和电感  $L_s$ 。

其中,图 4(c)中类型三缝隙  $g$  处并联谐振电路的阻抗可以表示为<sup>[14-15]</sup>:

$$X_{LC} = \frac{1}{j} \left[ \frac{1}{j\omega C_s} + \frac{1}{j\omega L_s} \right] = \frac{1}{\omega_0^2 C_s - \omega C_s} \quad (1)$$

(a) 类型一与类型二等效电路

(a) Equivalent circuit of type 1 and type 2(b) 类型三等效电路

(b) Equivalent circuit of type 3

图 7 三种类型的等效电路

Fig. 7 Equivalent circuits of three types

LC 谐振电路的谐振频率为:

$$\omega_0 = \frac{1}{\sqrt{L_s C_s}} \quad (2)$$

由式(1)、(2)可知,随着缝隙  $g$  处引入的电容  $C_s$  和电感  $L_s$  数值的增加,引起的电路谐振的谐振频率越低。

## 2 数值仿真与讨论

### 2.1 仿真分析

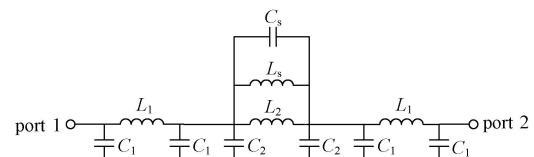

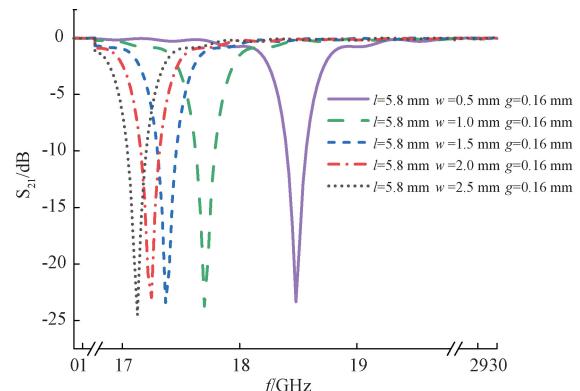

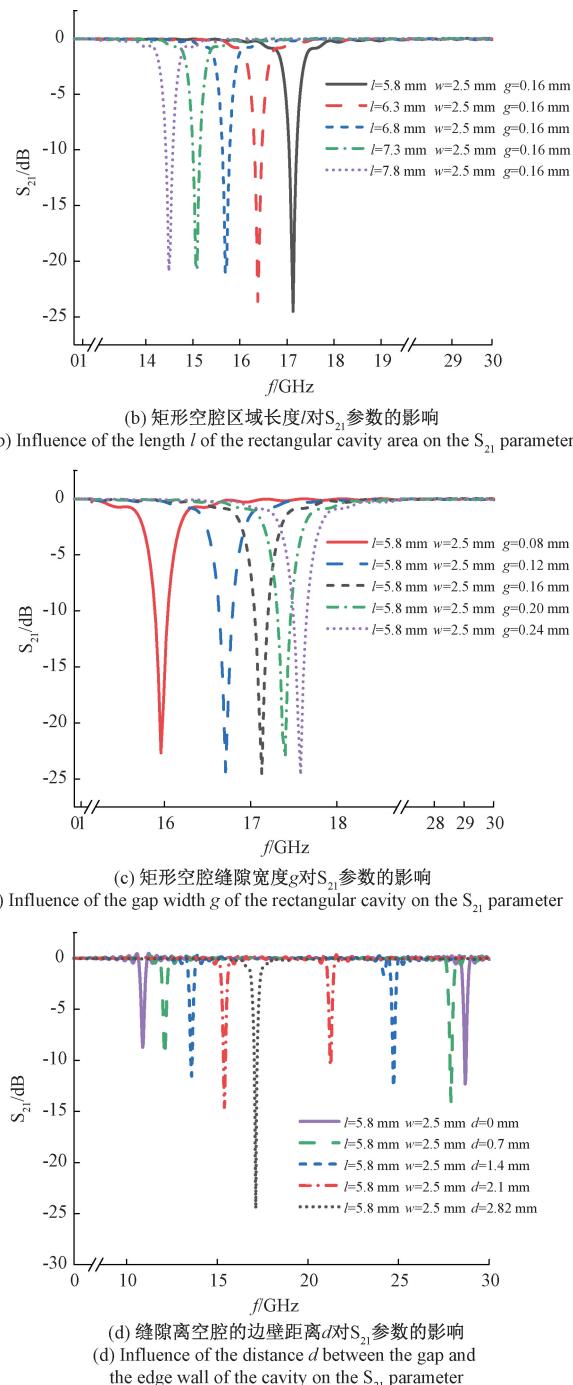

在其他参数不变的情况下,使用 CST 仿真软件分析图 4(c)中类型三的矩形空腔宽度  $w$  ( $0.5 \sim 2.5$  mm)、空腔长度  $l$  ( $5.8 \sim 7.8$  mm)、缝隙宽度  $g$  ( $0.08 \sim 0.24$  mm) 以及缝隙离空腔的边壁距离  $d$  ( $0 \sim 2.82$  mm) 对电路谐振频率的影响,仿真结果如图 8(a)、(b)、(c)、(d) 所示。

在图 8(a)中,当缝隙宽度  $g = 0.16$  mm 和长度  $l = 5.8$  mm 时,随着宽度从  $w = 0.5$  mm 逐渐增大(步长为 0.5 mm),谐振频率逐渐降低;在图 8(b)中,当宽度  $w = 2.5$  mm,缝隙宽度  $g = 0.16$  mm 时,随着长度从  $l = 5.8$  mm 逐渐增大(步长为 0.5 mm),谐振频率继续降低。因此,随着空腔区域长度  $l$  及宽度  $w$  的增大,电路的谐振频率逐渐降低,即空腔区域的面积越大,谐振频率越低。

在图 8(c)中,当宽度  $w = 2.5$  mm 和长度  $l = 5.8$  mm

(a) 矩形空腔区域宽度  $w$  对  $S_{21}$  参数的影响

(a) Influence of the width  $w$  of the rectangular cavity area on the  $S_{21}$  parameter

图 8 类型三缺陷地结构参数影响仿真结果

Fig. 8 Simulation results of influence of structural parameters in type 3 defected ground structure

时,随着缝隙宽度从  $g = 0.08 \text{ mm}$  逐渐增大(步长为  $0.04 \text{ mm}$ ),谐振频率逐渐增大。在图 8(d)中,当宽度  $w = 2.5 \text{ mm}$ 、长度  $l = 5.8 \text{ mm}$  和缝隙宽度  $g = 0.16 \text{ mm}$  时,由缝隙离空腔的边壁距离  $d$  的影响可知,随着缝隙离空腔的边壁距离  $d$  越来越小,电路中的谐振频率也将降低,当  $d = 0$  时,电路中的谐振频率最低,当  $d = 2.82 \text{ mm}$ ,即缝隙位于

空腔中间位置时,谐振频率最高。在图中的仿真频率范围内,每一个边壁距离值  $d$  出现了两个谐振点,而  $20 \text{ GHz}$  以上的谐振点,是对应尺寸下激起的高次模。

结合等效电路计算及仿真分析可知,随着矩形空腔区域面积的增大、缝隙离空腔的边壁距离  $d$  的减小,电路中的等效电感  $L_s$  将增大,电路的谐振频率也将降低;而随着矩形空腔缝隙宽度  $g$  的尺寸降低,电路中的等效电容  $C_s$  将增大,电路的谐振频率也将降低。

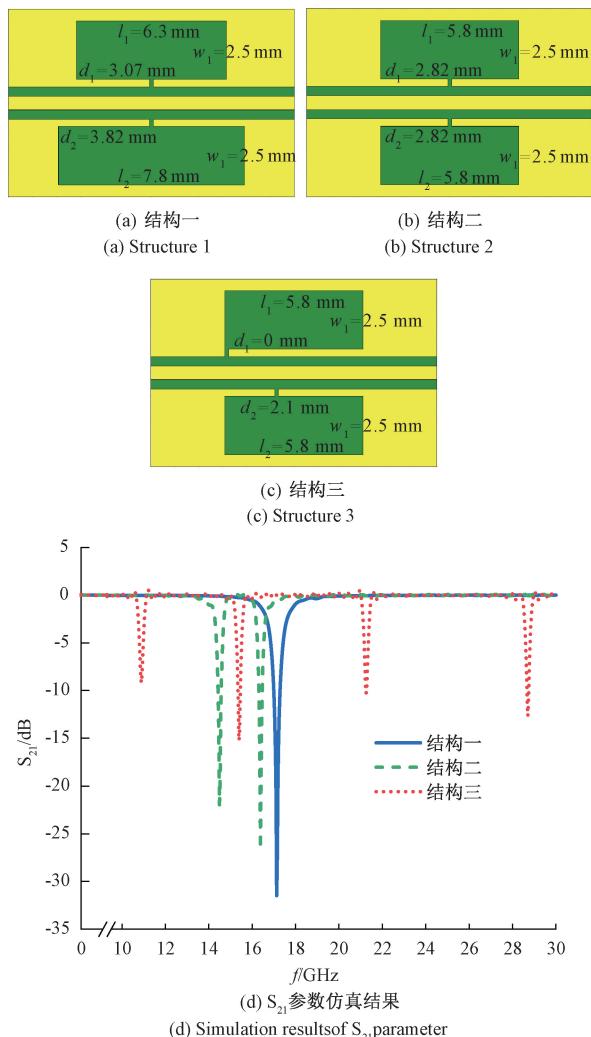

通过对类型三缺陷地结构的分析,传输线一端的接地面上出现缝隙和空腔时,会引起电路在缝隙处产生谐振现象,空腔的面积、缝隙的大小、缝隙距离空腔边缘的距离都会引起谐振频率的改变。进一步研究发现,在传输线另一端的接地面上出现缝隙和空腔时,同样会引起额外的谐振现象。图 9(a)、(b)、(c)为 3 种不同双腔结构电路。对 3 种不同双腔结构电路的传输特性进行分析,其仿真结果如图 9(d)所示。

在图 9(d)中,根据结构一  $S_{21}$  仿真结果可知,空腔尺寸相同、缝隙位置相同时,电路只会产生同一处谐振点。当  $w_1 = w_2 = 2.5 \text{ mm}$ 、 $l_1 = l_2 = 5.8 \text{ mm}$ 、 $g_1 = g_2 = 0.16 \text{ mm}$ 、 $d_1 = d_2 = 2.82 \text{ mm}$  时,对比图 8(d)中显示的单个空腔时的  $S_{21}$  参数仿真结果,17 GHz 附近的谐振点,单个空腔时插损小于  $25 \text{ dB}$ ,双空腔时,此时谐振点的插损  $>30 \text{ dB}$ 。根据结构二  $S_{21}$  仿真结果可知,空腔尺寸不同、缝隙位置相同时,电路会产生两处谐振点。并且当  $w_1 = w_2 = 2.5 \text{ mm}$ 、 $g_1 = g_2 = 0.16 \text{ mm}$  时,两处的谐振频点和图 8(b)中尺寸  $l_1 = 5.8 \text{ mm}$ 、 $l_2 = 7.8 \text{ mm}$  处相同。根据结构三  $S_{21}$  仿真结果可知,当空腔尺寸相同、缝隙位置不同时,电路会产生两处谐振点。并且当  $w_1 = w_2 = 2.5 \text{ mm}$ 、 $g_1 = g_2 = 0.16 \text{ mm}$ 、 $l_1 = l_2 = 5.8 \text{ mm}$  时,两处的谐振点频点和图 8(d)中的尺寸  $d_1 = 0 \text{ mm}$ 、 $d_2 = 2.1 \text{ mm}$  处相同。因此,传输线的两端的接地面上出现缝隙和空腔时,可以各自独立引起电路的谐振现象,对电路的传输特性造成影响。

## 2.2 电路改进

含有缺陷结构的共面波导,缺陷区域在朝着传输线一侧出现缝隙时,会使电路在工作频段内有产生谐振的潜在风险,因此,聚焦 QFN 器件 B 以及周围引脚。由图 2(a)中的器件 B 的局部电路可知,端口  $p_2$  输出位置  $g_1$  与 B 器件周围引脚的避铜空腔区域形成第 1 个图 4(c)类型三缺陷结构共面波导;端口  $p_2$  输出位置  $g_2$  与 B 器件周围引脚的避铜空腔区域形成第 2 个图 4(c)类型三的缺陷结构共面波导。正是这两个类型三的缺陷结构共面波导,导致电路产生了如图 1(b)、图 2(b)中的两个谐振点  $f_1$  和  $f_2$ 。

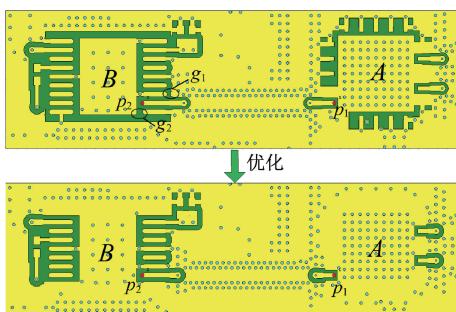

基于 1.2 节中的理论分析,若要去除低频谐振现象,需将类型三缺陷地共面波导中的缝隙  $g$  去除,使类型三缺陷地共面波导变成类型一或者类型二缺陷地共面波导。根据 2.1 节的仿真分析,若要提高谐振出现的频率,需要减小缺陷地的空腔面积。故对图 2(a)电路进行修改优化,分别去

图 9 三种不同双腔结构及  $S_{21}$  参数仿真结果

Fig. 9 Three different dual cavity structures and  $S_{21}$  parameter simulation results

除器件 B 引脚处缝隙  $g_1$  和  $g_2$ , 记录仿真结果; 缝隙  $g_1$ 、 $g_2$  同时去除, 并将器件 A 和 B 周围引脚的避铜空腔区域面积减小优化, 记录仿真结果。图 10(a)中电路最后优化结果如图 10 所示。

图 10 重点关注区域电路优化改进对比图

Fig. 10 Comparison chart of optimization and improvement of key focus area circuit

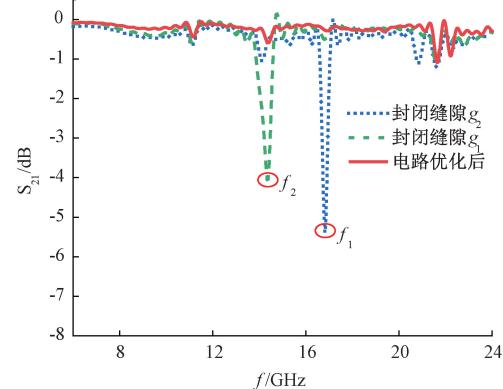

3 种情况  $S_{21}$  参数仿真对比结果如图 11 所示, 去除缝隙  $g_1$  时, 电路中只存在谐振点  $f_2$ , 谐振点  $f_1$  被消除; 去除缝隙  $g_2$  时, 电路中只存在谐振点  $f_1$ , 谐振点  $f_2$  被消除; 将传输线两端缝隙  $g_1$  与  $g_2$  全部去除, 并将器件 A、B 引脚四周空腔面积降低到最小, 最终的修改电路的主要谐振点  $f_1$  和  $f_2$  全部消失, 有效提高了电路的传输特性。

图 11 分别封闭缝隙  $g_1$ 、 $g_2$  以及电路优化后  $S_{21}$  参数结果

Fig. 11  $S_{21}$  parameter simulation results of closed gaps  $g_1$  and  $g_2$ , as well as after circuit optimization

### 3 结 论

本文对某款 QFN 封装的 SIP 器件在微波频段应用时发生谐振进行了分析研究。研究表明, QFN 封装器件的射频输出引脚易和周围引脚及周围接地地面形成含有缝隙的缺陷结构共面波导, 使电路等效引入了一个 LC 并联谐振电路, 造成电路易在低频段出现谐振点。本文探究了不同缺陷地结构的结构参数(空腔长度  $l$ 、空腔宽度  $w$ 、缝隙宽度  $g$ 、缝隙离空腔的边壁距离  $d$ )及传输线两端接地地面空腔同时出现对传输线特性的影响, 研究表明, 第 3 类缺陷地结构中空腔面积越大, 缝隙宽度越窄、缝隙离空腔的边壁距离越近, 造成电路谐振的频率越低; 并且传输线的两端接地面同时出现缝隙和空腔时, 可以各自独立引起电路的谐振。本文基于理论研究和仿真结果, 对出现谐振现象的电路进行优化设计, 通过去除电路中等效缺陷地共面波导结构中的缝隙, 有效消除了谐振现象。由本文可知, SIP 器件在微波频段应用时, 应有效避免在 QFN 封装射频输出引脚的上下接地引脚与避铜的空腔出现缝隙, 防止电路出现谐振的潜在风险。本文通过理论和仿真分析采取的去除谐振现象的手段和电路设计方法, 有效提高微波带内的平坦度, 该方法在现代高密度集成的第 4 代微波电路设计中有广泛的借鉴作用。本文展示的消除电路谐振点的方法是针对于 QFN 射频器件的射频信号引脚两端均为接地引脚的情况, 而对于射频信号引脚两端不全是接地引脚的 QFN 器件, 无法完全使用该方法, 可以通过排布接地孔、控制射频引脚两端接地面空腔面积等手段抑制谐振点, 这需要后续更加

详细的研究。

## 参考文献

- [1] 向伟玮. 微系统与 SiP、SoP 集成技术[J]. 电子工艺技术, 2021, 42(4): 187-191.

- XIANG W W. Microsystem with SiP and SoP integration technology [J]. Electronics Process Technology, 2021, 42(4): 187-191.

- [2] 徐锐敏, 王欢鹏, 徐跃杭. 射频微系统关键技术进展及展望[J]. 微波学报, 2023(5): 70-78.

- XU R M, WANG H P, XU Y H. Progress and prospects of key technologies in RF microsystems[J]. Journal of Microwaves, 2023(5): 70-78.

- [3] 龚静, 郭茜, 焦鹏辉, 等. 微系统发展现状及其在无人装备领域应用和展望[J]. 微电子学与计算机, 2024, 41(1): 1-10.

- GONG J, GUO Q, FAN P H, et al. The development status of microsystem and its application and prospect in the field of unmanned equipment[J]. Microelectronics & Computer, 2024, 41(1): 1-10.

- [4] 刘卫强, 万涛, 吕苗, 等. 基于硅基堆叠 SIP 技术的超宽带 T/R 组件[J]. 微波学报, 2024, 40(2): 74-78.

- LIU W Q, WAN T, LYU M, et al. Ultra-wideband T/R module based on silicon stack SIP technology[J]. Journal of Microwaves, 2024, 40(2): 74-78.

- [5] 翟志明, 邢小明, 夏侯海. 基于厚薄膜混合基板的超宽带垂直互联设计[J]. 电子测量技术, 2019, 42(4): 37-41.

- ZHAI ZH M, XING X M, XIA H H. Ultra-wideband vertical interconnect design based on thick film hybrid substrate [J]. Electronic Measurement Technology, 2019, 42(4): 37-41.

- [6] 王栋, 郑琦, 汤荣耀, 等. 基于 LTCC 基板 QFN 封装高速链路仿真及性能测试[J]. 电子与封装, 2020, 20(11): 14-18.

- WANG D, ZHENG Q, TANG R Y, et al. High speed link simulation and performance test of QFN package based on LTCC substrate [J]. Electronics and Packaging, 2020, 20(11): 14-18.

- [7] 皋利利, 周波华, 李超, 等. QFN 器件封装技术及焊点可靠性研究进展[J]. 电子工艺技术, 2022(4): 196-199, 203.

- GAO L L, ZHOU B H, LI CH, et al. Review of packaging technology and solder joint reliability about QFN devices [J]. Electronics Process Technology, 2022(4): 196-199, 203.

- [8] 冯泉水. 对 QFN 封装芯片散热 PAD 的测试研究[J]. 电子测试, 2020, (14): 19-20, 24.

- FENG Q SH. Research on heat dissipation PAD of QFN packaged chips in test [J]. Electronic Test, 2020, (14): 19-20, 24.

- [9] 冯立, 张庆军, 李银. QFN 封装埋嵌铜块印制板散热研究[J]. 印制电路信息, 2022, 30(7): 11-14.

- FENG L, ZHANG Q J, LI Y. Study of embedded copper coin printed circuit board of QFN package using thermal analysis [J]. Printed Circuit Information, 2022, 30(7): 11-14.

- [10] 谭戴导. 毫米波接地共面波导建模方法研究[D]. 西安: 西安电子科技大学, 2022.

- TAN D D. Study on modeling method of millimeter wave grounded coplanar waveguide[D]. Xi'an: Xidian University, 2022.

- [11] 张乃柏. 基于共面波导缺陷结构的 RF MEMS 滤波器理论研究与优化设计[D]. 北京: 北京邮电大学, 2012.

- ZHANG N B. Theoretical study and optimal design on RF MEMS filter based on CPW defect structures[D]. Beijing: Beijing University of Posts and Telecommunications, 2012.

- [12] 王楚玺. 基于缺陷地共面波导的无损葡萄糖传感器研究[D]. 南京: 东南大学, 2023.

- WANG CH X. Research of non-invasive glucose sensors using defective-ground-structure coplanar waveguide[D]. Nanjing: Southeast University, 2023.

- [13] 李露. 基于缺陷地结构的共面波导带通滤波器设计[D]. 重庆: 重庆邮电大学, 2021.

- LI L. Design of coplanar waveguide bandpass filters based on defected ground structure[D]. Chongqing: Chongqing University of Posts and Telecommunications, 2021.

- [14] 凌锐, 于映. 基于中心对称结构的带宽可重构滤波器设计[J]. 电子测量技术, 2023, 46(1): 142-147.

- LING R, YU Y. Design of bandwidth reconfigurable filter based on centrosymmetric structure [J]. Electronic Measurement Technology, 2023, 46(1): 142-147.

- [15] 刘义彬. 基于 RF MEMS 开关与加载缺陷地结构的可调滤波器研究[D]. 北京: 北京邮电大学, 2021.

- LIU Y B. Research on tunable filter based on RF MEMS switch and loaded by defective ground structure[D]. Beijing: Beijing University of Posts and Telecommunications, 2021.

## 作者简介

- 田腾(通信作者), 工程师, 主要研究方向为射频电路及射频直采技术。

E-mail: tian\_teng\_tt@163.com

- 王志奎, 高级工程师, 主要研究方向为微波与通信技术。

E-mail: wangzhikui-wzk@163.com

- 刘亚旭, 高级工程师, 主要研究方向为射频电路、数模混合电路及架构技术。

E-mail: liuyaxu168@163.com

- 崔彭, 工程师, 主要研究方向为射频电路及宽带毫米波天线。

E-mail: pz\_cui@163.com

- 王培阳, 工程师, 主要研究方向为射频电路及微波通信技术。

E-mail: 512784757@qq.com