DOI:10.19651/j.cnki.emt.2315004

# 轻量化音频信号处理算法与FPGA实现<sup>\*</sup>

龙彪 杨军 陈惠萍 陈光润 赵培阳

(广西师范大学电子与信息工程学院 桂林 541004)

**摘要:**为了解决语音通信系统中音频信号处理的数据量大,杂散信号多,以及调频接收机在接收到的音频信号忽大忽小的问题,提出了一种轻量化音频信号处理算法,并基于此算法在现场可编程门阵列(FPGA)平台上实现了音频信号的接收与自动增益控制。该算法结合数字下变频技术、多级抽取滤波技术及自动增益控制技术(AGC),应用于音频信号处理系统中,将从上级天线接收的射频模拟信号通过模数转换以及数字下变频转换为基带音频信号,经四级抽取滤波将基带信号中的杂散信号滤除,降低了系统的复杂性和功耗,同时AGC对基带音频信号进行控制调整,输出较为稳定的音频信号。经过实验证明:该算法能够有效地将信息速率从102.4 MHz降至32 kHz、减少计算负担、提高信号质量、降低了FPGA的资源利用率;并且实现音频信号的自动增益控制调整,其调整时间仅为12.8 μs,满足接收机的功率稳定时间。

**关键词:**音频信号;数字下变频;多级抽取滤波;自动增益控制

中图分类号:TN912.3 文献标识码:A 国家标准学科分类代码:510.4040

## Lightweight audio signal processing algorithm and FPGA implementation

Long Biao Yang Jun Chen Huiping Chen Guangrun Zhao Peiyang

(College of Integrated Circuits, Guangxi Normal University, Guilin 541004, China)

**Abstract:** In order to solve the problem that the audio signal processing in the voice communication system has a large amount of data, a lot of stray signals, and the received audio signals of the frequency modulation receiver are large and small, a lightweight audio signal processing algorithm is proposed, and based on this algorithm, the audio signal receiving and automatic gain control are realized on the field programmable gate array(FPGA) platform. The algorithm combines digital down-conversion technology, multistage extraction filtering technology and automatic gain control technology (AGC) technology, and is applied to the audio signal processing system. The RF analog signal received from the upper antenna is converted into baseband audio signal through analog-to-digital conversion and digital down-conversion, and the stray signal in the baseband signal is filtered through four-stage extraction filtering, reducing the complexity and power consumption of the system. At the same time, the digital AGC controls and adjusts the baseband audio signal to output a more stable audio signal. The experimental results show that the algorithm can effectively reduce the information rate from 102.4 MHz to 32 kHz, reduce the computation burden, improve the signal quality, and reduce the resource utilization of FPGA. And the automatic gain control adjustment of audio signal is realized, and the adjustment time is only 12.8 μs, which meets the power stability time of the receiver.

**Keywords:** sound signal; digital downconversion; multistage extraction filtering; automatic gain control

## 0 引言

在传统的语音通信系统中,存在着因采样频率过高等因素导致数据冗余量过大,以及因传播距离的远近、音频信号源不稳定等外界因素导致音频信号的强度发生变化等一系列问题<sup>[1-6]</sup>。针对这一系列问题,这就需要降低音频信号

处理系统的数据量或者提高硬件设备的处理能力,以及对不同幅度的音频信号进行自动增益控制(automatic gain control, AGC)调整。在基于现场可编程门阵列(field-programmable gate array, FPGA)平台的音频信号处理系统中为了提升数据处理能力,传统方法是采用性能更好的FPGA芯片<sup>[7-14]</sup>。而针对接收的音频信号忽大忽小的问

收稿日期:2023-11-16

\*基金项目:中央引导地方科技发展资金项目(桂科ZY23055007)、广西师范大学重大科技成果转化培育项目(2020PY002)资助

题，传统接收机的音频处理系统是采用模拟自动增益控制电路来实现射频信道单元增益的放大或者衰减，这种方式存在模拟 AGC 收敛速度慢和收敛过程容易受环境影响的问题，从而引起接收信道增益误调整<sup>[15-19]</sup>。

本文提出了一种轻量化音频信号处理算法,该算法将接收到的射频信号通过数字下变频转换为基带音频信号,然后对基带音频信号进行四级抽取滤波,再将滤波后的音频信号通过数字 AGC 模块实现信号幅度的放大和衰减,从而实现音频信号的稳定接收。四级抽取滤波模块,降低了基带信号的信息速率,滤除了杂散信号,减少了计算负担,提高了 FPGA 的资源利用率。数字 AGC 模块对输入的音频信号进行实时性跟踪,监测音频信号的幅值变化并反馈到数字信号处理单元,与标准阈值范围对比,确定增益倍数。

N，再对数字信号左移或者右移，实现对音频信号的增益控制。

该算法基于 MATLAB 进行预仿真，在 FPGA 平台上搭建音频信号处理系统，实现轻量化音频信号处理算法，可以大大降低计算负担、提高信号质量、降低 FPGA 的资源利用率，同时实现音频信号的自动增益控制。

## 1 音频信号处理系统整体框架

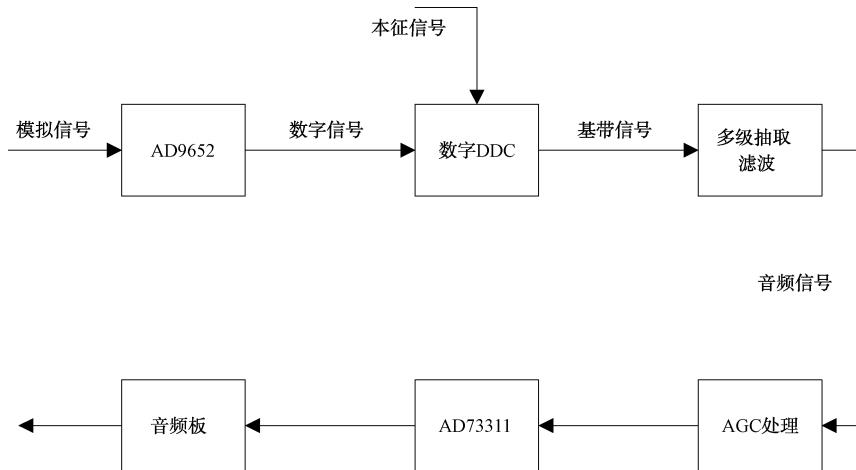

本系统在 FPGA 中实现, FPGA 采用 Xilinx 公司的 ZYNQ 7000 系列的 xc7z045ffg900-2, 系统主要分为 4 个部分, 分别是基于 AD9652 芯片的模数转换模块、数字下变频 (digital down converter, DDC) 模块、多级抽取滤波模块、AGC 处理模块, 整体设计示意图如图 1 所示。

图 1 音频信号处理系统整体结构

其中基于 AD9652 芯片的模数转换模块实现射频模拟信号到数字信号的转换。DDC 模块将数字中频信号搬移到零频附近,即数字基带信号;多级抽取滤波模块对数字基带信号进行抽取和滤波,降低信息速率,计算负担,提高信号质量。AGC 处理模块实现对音频信号的自动增益调整。

AD9652 是一款双通道、16 位、采样速率最高达 310 MSPS 的模数转换器(ADC)。它用于支持高要求、高速度信号处

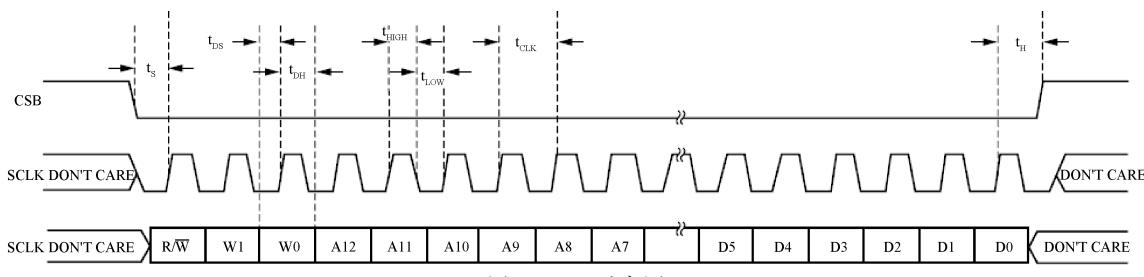

理应用,该应用需要在宽输入频率范围(465 MHz)具有优秀的动态范围。来自每个 ADC 的 16 位输出数据与双数据速率(DDR)时钟在单独的 LVDS 输出端口交错。FPGA 通过 SPI 通信接口,完成对 AD 芯片寄存器的配置,其时序图如图 2 所示,片选信号(CSB)拉低时开始进行 SPI 操作,三线制 SPI 的读写共用一根线,其读写状态由读写指令位(R/W)所确定。

图 2 SPI 时序图

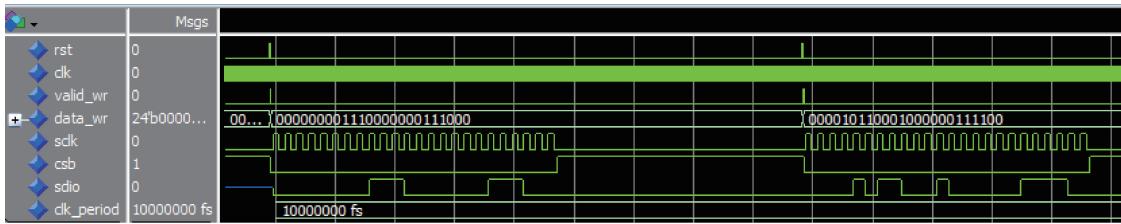

SPI 时序仿真结果如图 3 所示, 系统时钟频率为 100 MHz, 输入串行时钟(SCLK)频率为 10 MHz, 闲置状态下片选信号(CSB)处于高电平, 当 CSB 处于低电平时开始进行数据传输, 串行数据会在时钟上升沿和时钟下降沿进行读写。

操作。

2 数字下变频模块

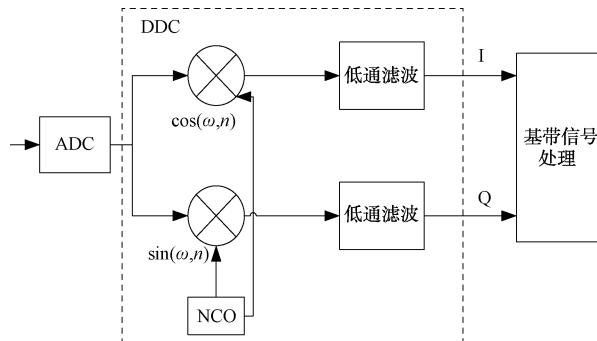

根据系统设计框图可知, DDC 模块将从 AD9652 芯片

图3 SPI时序仿真

输出的数字中频信号搬到零频附近。DDC 结构图如图 4 所示。

图4 数字下变频结构图

从图 4 中可知,从 ADC 芯片输出的采样信号与 DDC 中的数控振荡器(NCO)产生的本地数字中频载波信号进行混频,将中频信号下变频到基带。

其中  $s_t$  是中频输入信号,  $x_{lo}$  是本振信号:

$$s_t = \cos\{2\pi(f_0 + f_c)t + \varphi_1\} \quad (1)$$

$$x_{lo} = \cos(2\pi f_c t + \varphi_2) \quad (2)$$

将中频信号与本振信号进行混频后可得:

$$\begin{aligned} f_{mix} &= s_t \cdot x_{lo} = \cos\{2\pi(f_0 + f_c)t + \varphi_1\}\cos(2\pi f_c t + \varphi_2) = \frac{1}{2}\{\cos(2\pi(f_0 + 2f_c)t + \varphi_1 + \varphi_2) + \cos(2\pi f_0 t + \varphi_1 - \varphi_2)\} \end{aligned} \quad (3)$$

式中:  $f_0$  为基带信号频率, Hz;  $f_c$  为本振信号频率, Hz;  $\varphi_1$  为中频输入信号初相位,  $\varphi_2$  为本振信号初相位。

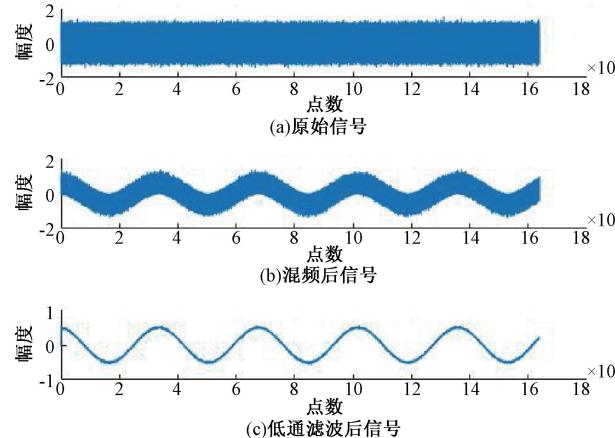

可见,当对中频信号和本振信号进行混频后,会产生一个射频信号与基带信号。为进一步对混频后的信号进行低通滤波后便得到所需要的基带信号。本系统的本征信号频率 10 MHz, 音频信号频率为 3 kHz, 信噪比为 15 dB。图 5 给出了原始信号、混频后的信号、低通滤波后的信号时域波形对比图。

### 3 多级抽取滤波器模块

多级抽取滤波器模块旨在对数字下变频后的基带信号进行抽取滤波处理,降低信号的信息速率,滤除不相关的杂散信号,同时解决了一级滤波器工程实现难的问题。目标音频信号带宽为 3 kHz, 末级信号采样率设计为 32 kHz。数字下变频后的基带信号信息速率为 102.4 MHz,

图5 变频前后的信号对比

经过本模块处理后的信息速率降低为 32 kHz, 抽取倍数为 3 200 倍。若直接采用一级抽取滤波的话,在工程上很难实现,本文设计了不同抽取级别的滤波器,并应用于FPGA 中进行测试,所采用的 xc7z045ffg900-2 FPGA 芯片 DSP 为 900, BRAM 为 545。测试结果如表 1 所示,由于总的抽取倍数为 3 200 倍,直接分两级或三级抽取滤波会消耗较多的 FPGA 资源,这将导致时序违例较严重的情况出现,使得 FPGA 上板运行出现异常。若抽取的级数过多,不仅会增加额外的工作量,而且难以进一步降低资源利用率。

表1 抽取滤波模块的FPGA资源消耗情况

| 抽取级数 | 抽取形式       | DSP 个数 | BRAM 个数 | DSP 资源占用率/% | BRAM 资源占用率/% |

|------|------------|--------|---------|-------------|--------------|

| 二级   | 25×128     | 100    | 15      | 11.11       | 2.75         |

| 三级   | 5×20×32    | 34     | 3       | 3.78        | 0.55         |

| 四级   | 2×4×16×25  | 22     | 2       | 2.44        | 0.37         |

| 五级   | 2×4×5×8×10 | 24     | 2       | 2.67        | 0.37         |

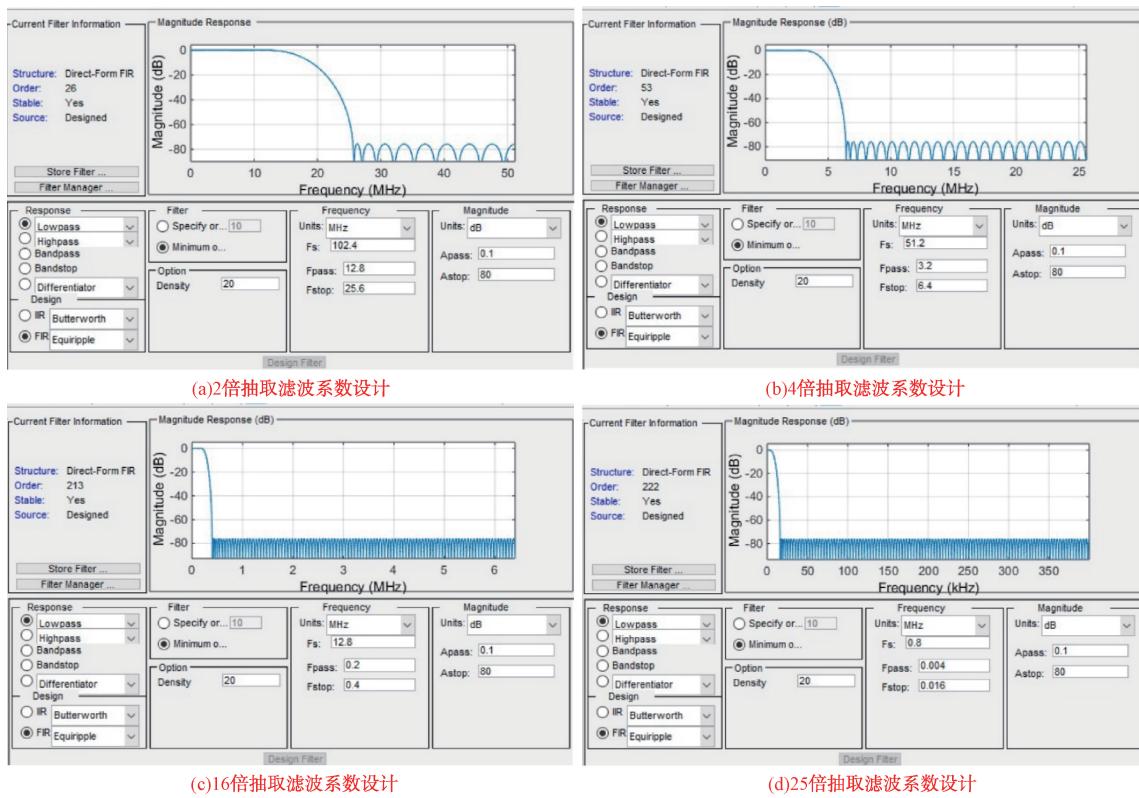

综合工程实践难易程度,以及FPGA的资源利用率,本模块采取四级抽取滤波,每一级抽取倍数分别为 2 倍、4 倍、16 倍和 25 倍。在 MATLAB 中通过 fdatoool 工具,设计每一级滤波器的系数。图 6 为每一级滤波器系数设计截图。由图 6(a)可知,初始采样速率  $F_s = 102.4$  MHz, 经过 2 倍抽取后采样速率降为 51.2 MHz, 由采样定理可知,信号频率不得高于采样频率的 0.5 倍,即滤波器的截止频率  $F_{stop} = 25.6$  MHz。图 6(b)、(c) 和 (d) 为继续进行 4 倍、

图 6 滤波器系数设计

16 倍和 25 倍抽取滤波设计。

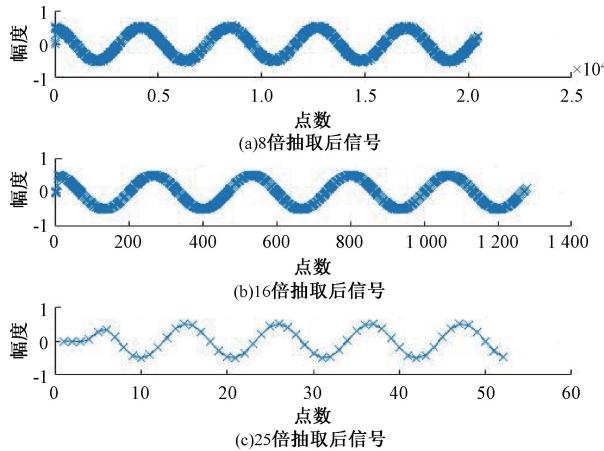

根据设计的每一级滤波器系数,在 MATLAB 中对四级抽取滤波后采样的音频信号进行仿真,结果如图 7 所示。

图 7 抽取滤波后采样的音频信号

目标音频信号带宽为 3 kHz, 其横坐标为音频信号进行采样的采样点数, 纵坐标为音频信号的幅度。抽取倍数与信号样点速率的对应关系如表 2 所示, 信息速率经过第一级的 2 倍及第二级的 4 倍抽取滤波后, 一个音频信号周期范围内有 4 266 个信号样点; 再对信息速率进行 16 倍抽取滤波, 一个音频信号周期范围内有近 266 个信号样点;

经过末级 25 倍抽取滤波后采样频率为 32 kHz 时, 频率为 3 kHz 的目标音频信号的一个周期范围内的信号样点仅为 10 个。这大大降低了信息速率, 避免了过采样的情况出现, 降低了系统的复杂性和功耗, 滤除了部分高频噪声和干扰。

表 2 抽取滤波后的样点速率

| 抽取级数 | 抽取倍数 | 样点速率/<br>MHz | 一个周期内<br>样点个数 |

|------|------|--------------|---------------|

| 第一级  | 2    | 51.2         | 17 066        |

| 第二级  | 4    | 12.8         | 4 266         |

| 第三级  | 16   | 0.8          | 266           |

| 第四级  | 25   | 0.032        | 10            |

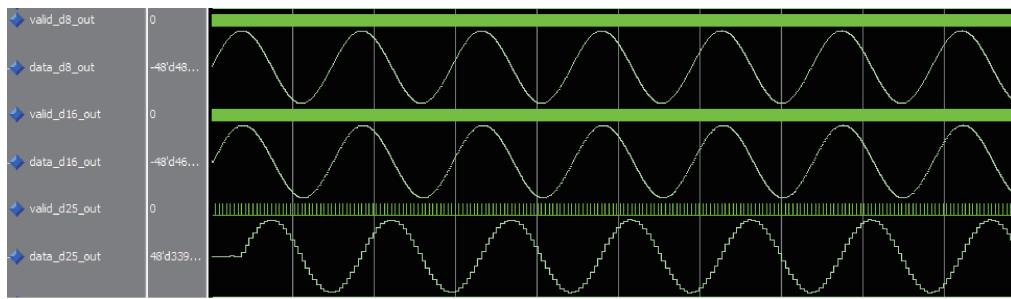

FPGA 对抽取滤波器模块的控制采用 VHDL 硬件描述语言编程设计, 在 Vivado 2018.3 环境下进行编译、仿真和调试。实现的结果如图 8 所示, 可见在 FPGA 中仿真实现的结果与 matlab 中仿真的结果一致, 经过抽取滤波后大大降低了信息速率。

## 4 自动增益控制模块

### 4.1 输出动态范围的确定

综合接收机工作的实际情况考虑, 若自动增益控制的阈值取为定值, 那么经过增益调整后的输出信号的幅度可

图8 抽取滤波模块联合仿真图

能无限接近这一期望值,将导致信号持续性地进行增益调整,使得输出信号不稳定。因此,综合接收机功率稳定要求以及工程实现难度考虑,本系统的增益调整电平区间为 $-110\sim-10$  dBm,最佳电平区间为 $-30\sim-20$  dBm,其他区间以5 dBm为一个电压增量值。当音频信号幅值所对应的电平区间为 $-30\sim-20$  dBm时,认为信号已处于稳定状态,不再对其进行增益调整,若不在该动态范围内,则以5 dBm为一个电压增量值对音频信号进行增益调整,这样可以使输出信号的幅度得到稳定。

#### 4.2 增益调整速度的确定

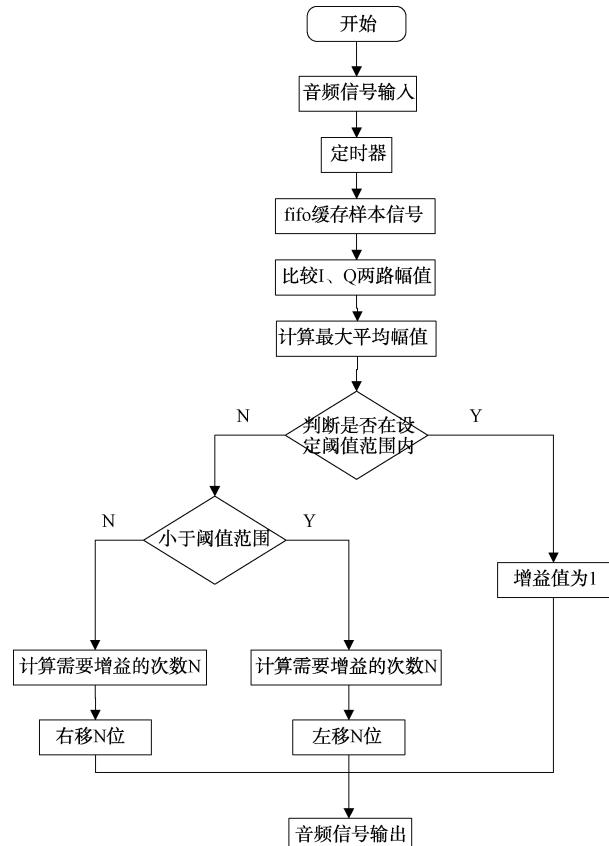

在语音通信系统中,信号的幅度大小是在不断变化的,如果频繁的对音频信号进行增益调整,不仅会增加FPGA资源占用率还可能导致音频信号“失真”。故本系统设定增益调整时间间隔为1 s,即每隔1 s对信号强度进行一次检测,若不在最佳电平区间则对信号进行增益调整,其调整时间仅为 $12.8\mu s$ 。本文所设计的数字AGC算法流程如图9所示。

音频信号的信号幅度为:

$$A = \sqrt{I^2 + Q^2} \quad (4)$$

式中: $A$ 为音频信号幅度, $I$ 为I路信号幅度, $Q$ 为Q路信号幅度。

由于在FPGA中进行开平方操作会消耗太多的资源,因此需要对信号进行一步处理,进行泰勒展开后:

$$\begin{aligned} \sqrt{I^2 + Q^2} &= I \sqrt{1 + \left(\frac{Q}{I}\right)^2} = \\ I \left(1 + \frac{1}{2} \left(\frac{Q}{I}\right) - \frac{1}{8} \left(\frac{Q}{I}\right)^2 + \dots\right) &\approx I \left(1 + \frac{1}{2} \left(\frac{Q}{I}\right)\right) = \\ I + \frac{1}{2} Q \end{aligned} \quad (5)$$

$$\begin{aligned} \sqrt{I^2 + Q^2} &= Q \sqrt{1 + \left(\frac{I}{Q}\right)^2} = \\ Q \left(1 + \frac{1}{2} \left(\frac{I}{Q}\right) - \frac{1}{8} \left(\frac{I}{Q}\right)^2 + \dots\right) &\approx Q \left(1 + \frac{1}{2} \left(\frac{I}{Q}\right)\right) = \\ Q + \frac{1}{2} I \end{aligned} \quad (6)$$

将信号幅度A进一步处理可得:

$$A = \max(I, Q) + \frac{1}{2} \min(I, Q) \quad (7)$$

图9 数字AGC算法流程图

由此可见接收到的信号的强度与I/Q两路信号的大小有关。

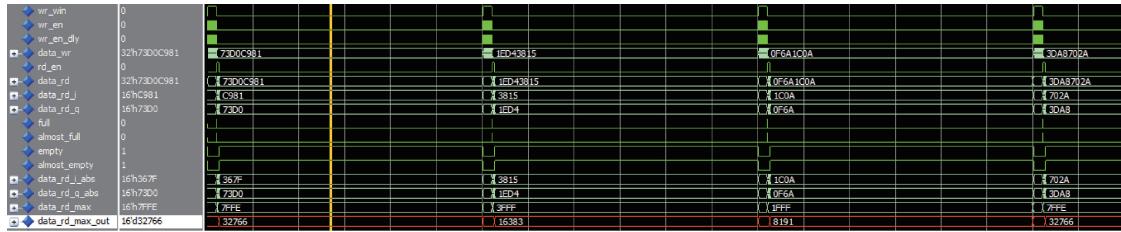

本实验平台基于Xilinx公司ZYNQ-7000系列xc7z045ffg900-2芯片,音频采样A/D采用A/D9652芯片进行模数转换,将采样频率为102.4 MHz的采样信号对原始音频信号进行采样,设计一个时间间隔为1 s的定时器模块,每隔1 s,将采集输入信号的256个样点缓存进fifo。设计仿真结果如图10所示,将I/Q两路信号幅度取绝对值再分别求出平均幅度,并进行比较判断,得出两路信号幅度的最大平均值 $A_m$ ,如图10中的信号“data\_rd\_max\_out”,再根据 $A_m$ 来对增益进行调整。如果采集到的样点信号的 $A_m$ 处于设定好的阈值范围内,则增益的倍数为1。如果采集到的样点信号的 $A_m$ 大于设定好的阈值范围,则

对数字信号进行右移相应位数  $N$ , 即将超过阈值范围内的音频信号调小。如果采集到的样点信号的  $A_m$  小于设定好

图 10 fifo 样本信号缓存模块

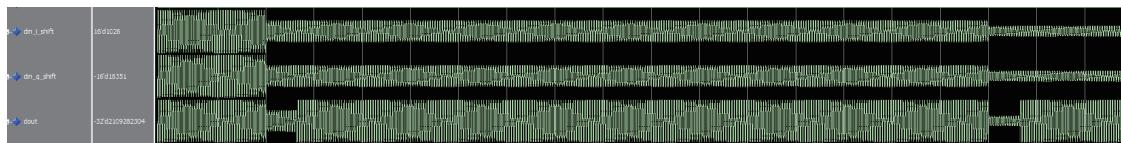

调节输入音频信号的幅度, 仿真后显示的输出信号的变化如图 11 所示。当输入信号幅度不断发生变化时, 经过采集信号样点并得出该段信号的平均幅度  $A_m$  后, 若其所对应的电平值不在最佳电平区间  $-30 \sim -20$  dBm 内, 则根据增益调整基准, 以每 5 dBm 为一个电压增量值对原始音频信号进行调整, 使得信号的幅度趋于一个较为稳定的区间, 符合设计需求。

图 11 在 Modelsim 环境下对 AGC 方案进行布局布线后的仿真结果

## 5 结 论

本文针对语音通信系统中音频信号处理数据量大、占用硬件资源较多以及受外界干扰波动较大的情况, 提出了一种轻量化音频信号处理算法, 并基于该算法在 FPGA 硬件平台上设计并实现了一种新型的语音处理系统。该算法应用于音频处理系统中, 大大降低了系统的复杂性和功耗, 滤除了部分高频噪声和干扰, 多级抽取滤波模块 DSP 与 BRAM 占用率分别为 2.44%、0.37%, 在降低 FPGA 资源占用率方面具有明显优势, 并且 AGC 处理除了使得输出的音频幅度相对平稳外, 还具有一定的噪音抑制能力, 其增益调整时间仅为 12.8  $\mu$ s, 符合接收机功率稳定时间要求, 与传统的音频处理系统相比具有较大优势。本语音处理算法已成功运用于某语音通信的接收机中。然而本系统缺点也较为明显, 由于受信号毛刺的影响, 会使得求信号平均功率时产生误判, 导致计算增益倍数时发生错误。在今后的研究工作中, 还需要对计算平均功率的灵敏度进行提高。

## 参考文献

- [1] 田高峰, 邓计才, 张延彬, 等. 基于 FPGA 的可变带宽基带信号回放系统设计 [J]. 电子测量技术, 2023, 46(5): 17-22.

- [2] 汪震, 杨嘉睿, 娄岱松, 等. 基于 FPGA 的超声导波宽带激励源设计 [J]. 电子测量技术, 2023, 46(11): 30-36.

- [3] 李晨雨. 微波快速 AGC 技术的研究 [D]. 成都: 电子科技大学, 2014: 35-65.

- [4] 李志骞, 李大鹏, 单福悦. 基于数字 AGC 的控制算法 [J]. 无线电工程, 2012, 42(6): 58-61.

- [5] ZHOU Y, CHIA M Y W. A low-power ultra-wideband CMOS true RMS power detector [J]. IEEE Transactions on Microwave Theory and Techniques, 2021, 56(5): 1052-1058.

- [6] 付扬. 基于 FPGA 的信号源设计 [J]. 工矿自动化, 2016, 42(7): 59-62.

- [7] 林俊武, 饶连周, 林东东. 基于 AGC 的等精度数字频率计设计 [J]. 延边大学学报(自然科学版), 2016, 42(2): 161-164.

- [8] 龚泯宇, 郭世旭, 田皓文. 基于 FPGA 的多波束声纳发射机与接收机模块化设计 [J]. 电子测量技术, 2022, 1(36): 141-148.

- [9] 郭栋梁, 张晓荣, 李晓飞. 基于 FPGA 的音频数模混合 AGC 采集系统 [J]. 山西电子技术, 2023, 4: 26-29.

- [10] 徐灵基, 杨益新. 海洋环境噪声接收机的设计与实现 [J]. 电子测量技术, 2016, 39(4): 31-35.

- [11] 宋锡文, 董业鹏, 杨世飞. 基于 FPGA 的振动信号处理参数寻优试验研究 [J]. 电子测量与仪表学报, 2021, 35(2): 101-108.

- [12] AMER A E, ABDALLA M A Y, ESHRAH I A. 20~44 GHz mismatch tolerant programmable dynamic

- range with inherent CMRR square law detector for AGC applications[C]. 2019 49th European Microwave Conference, 2019.

- [13] ZHOU Z, WEI Y. The influence of automatic gain control on narrowband frequency domain GPS anti-jamming receiver[C]. 2021 IEEE 21st International Conference on Communication Technology, 2021.

- [14] 林师远,李文惠,孙双花,等.基于 FPGA 的高速动态测量数据采集系统[J].电子测量技术,2023,46(15):32-37.

- [15] 薛擎.智能音箱芯片中数字音频均衡器设计[D].西安:西安电子科技大学,2020.

- [16] 谈良,纪凌.基于 FPGA 的多通道数据采集系统设计与实现[J].电子测量技术,2018,41(5):57-63.

- [17] 王栋.一种大动态范围数字 AGC 快速控制算法[J].通信技术,2023,56(9):1099-1106.

- [18] 柯乐乐,方圆,王毅,等.基于 FPGA 短波发射机音频 AGC 算法的设计与实现[J].通信技术,2023,56(5):661-665.

- [19] 陈云刚,郑澍鹏.宽频段大动态快速响应 AGC 设计[J].移动通信, 2023,47(4): 98-102.

### 作者简介

龙彪,硕士研究生,主要研究方向为通信工程(含宽带网络、移动通信等)。

E-mail:486917564@qq.com

杨军(通信作者),高级工程师,硕士生导师,主要研究方向为通信工程。

E-mail:yjgioc@163.com