# 基于 FPGA 的雷达实时测速系统硬件设计

陈 珞 白雪杨

(中国电子科技集团公司第二十八研究所 南京 210096)

摘 要:伴随着社会科技与经济的高速发展,对测量速度的需求越来越多。雷达测速数据实时处理系统作为测速系统中的核心设备之一更是决定着速度测量的实时性和精度,研制高精度的实时数据处理系统对于国家安全和发展有着非常重要的战略意义。针对目前测速设备中实时信号处理系统实时性能差的问题,提出了一种利用嵌入式技术与数字信号处理技术相结合的硬件设计方案。这种方案以 FPGA 为核心,完成信号处理和对外设的控制。实验数据表明,系统对低频信号和高频信号都能够得到较好的采集性能,能够满足应用需求。

关键词: FPGA; 实时测速; 嵌入式

中图分类号: TN953<sup>+</sup>.1 文献标识码: A 国家标准学科分类代码: 510.1050

# Design of an FPGA based radar system for real-time speed measurement

Chen Luo Bai Xueyang

(No. 28 Research Institute, China Electronics Technology Group Corporation, Nanjing 210096, China)

Abstract: The demand for accurate speed measurement increases with the rapid development of electronic science and technology in recent years. As the key component of speed measurement radar, the hardware circuits in real-time speed measurement radars have essential impact on the accuracy and real-time performance of the measurement results. Thus it is important to design high performance hardware circuits for speed measurement radars. This paper presents a hardware design for the speed measurement radars to improve the accuracy and real-time performance of radar systems. The hardware platform is based on field-programmable gate array (FPGA) thus the digital signal processing technique can be exploited to process the radar signals and control the radar system. The experimental results show that the proposed radar system maintains high performance for both low and high frequency signals. Thus the proposed system is applicable in real applications.

Keywords: FPGA; real-time speed measurement; embedded

# 1 引 言

随着信息技术的迅猛发展,基于红外线测速、激光测速和雷达测速等方法的测速设备因其高精度、高可靠性和运算速度快等特点而得到了大量应用[1-4]。目前主流的测速雷达采用的仍是以 DSP,ARM 为运算核心的硬件架构<sup>[5]</sup>,虽然节约了开发的时间成本,但顺序执行的运算方式,限制了进一步对算法实现的优化与改进。本课题使用常用的多普勒雷达测量运动目标的速度,算法相对成熟,同时可以精确的测量移动目标的速度,当与现代计算机技术相结合采用 FPGA 做运算核心时,可以对算法进行并行计算的改进,提高执行效率和速度,同时系统可以做到实时处理显示、数据无损存储、设备一体化和实时处理与事后处理结合。本文提出的雷达系统设计方案结合了微弱信号调理技

术、高速大容量缓存技术和宽带数据传输技术,使系统能够检测到微弱的雷达回波信号,同时能够将处理结果实时传输到上位机上进行显示。

#### 2 系统总体设计

雷达测速模块硬件主要完成对脉冲信号的高速采样、记录与实时处理<sup>[6]</sup>。设备采用高速 ADC 对外部输入脉冲信号进行转换,转换后的数字信号在高性能 FPGA 内通过实时高速信号处理算法进行快速计算,最终的计算结果通过大容量记录系统进行实时记录。系统整体由 4 大部分构成:

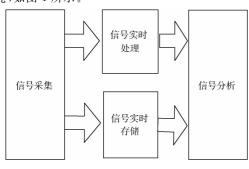

信号采集部分主要用于对脉冲信号的高速数字化过程,采集后的数据将分为两路,一路进入实时处理模块进行信号的实时处理,另一路进入实时存储模块进行是实时记

录,实时记录后的数据在上位机信号分析模块中使用 MATLAB进行处理,最终两路处理结果进入信号分析模 块进行分析和比对,从而指导用户进行脉冲信号处理算法 的研究,如图 1 所示。

图 1 系统整体框图

本系统不仅能够用于算法验证和评估,也可以用于对原始信号进行无损的实时记录。系统具有性能出色、扩展性好、适用范围广、工作稳定的优点。

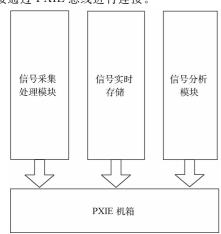

## 3 系统设计方案

系统硬件包括 4 大部分:脉冲信号采集处理模块、实时存储模块、信号分析模块和 PXIE 便携式机箱,其中脉冲信号采集处理模块是系统的核心部分,实时存储模块、信号分析模块分别采用 PXIE 控制器和存储器实现。系统各个单元的连接通过 PXIE 总线进行连接。

图 2 系统各单元连接示意图

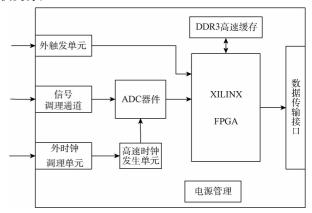

### 3.1 信号采集处理模块总体设计

信号采集处理模块主要包含外触发单元、信号调理通道、外时钟调理单元、高速时钟发生单元、ADC器件、FPGA模块、DDR2高速缓存、电源管理、数据传输接口等。ADC模块主要完成对输入脉冲信号的采样,然后将源同步的数据输入FPGA进行处理,采样速率为100Msps,量化位宽14bit。系统在FPGA中依据外部触发信号,对ADC器件的采集信号进行截取。然后在FPGA内部完成IQ解调、

相关运算、多项式拟合、FFT变换、FIR滤波等实时信号处理算法。最后将计算得到的结果及原始采样数据通过PCIE高速数据传输接口传输到上位机,为用户后续分析提供支持。

图 3 信号采集处理模块示意框图

#### 3.1.1 ADC 模块

系统中的 ADC 采用 14 位,105 Msps 采样速率的模数转换器芯片 ADS6444。该芯片集成了输入缓冲用于隔离内部采样保持器和外部电路之间的串扰,该缓冲器同时提高了 ADC 的输入阻抗。ADS6444 芯片采用串行模式的LVDS 电平数字量输出,芯片具有很高的 SNR 性能和SFDR 性能,十分适合高精度的数据采集应用。

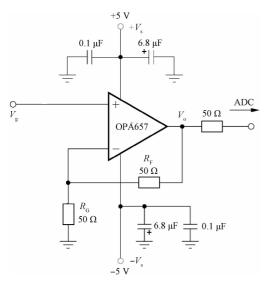

为了检测高速率脉冲信号,同时避免电流流人检测电路影响测量精度,前置放大器选用高输入阻抗的 JFET 输入级的运算放大器 OPA657。OPA657是一款高带宽,低失调,低噪声的电压反馈型运算放大器。放大器具有极高阻抗的 JFET 输入结构,其差分输入阻抗高达 1 012  $\Omega$ 。运放增益带宽积达到 1. 6 GHz,输入电压噪声为 4. 8  $nV/\sqrt{Hz}$ ,非常适合宽带小信号的检测。输入小信号检测电路图如图 4 所示。

在 OPA657 的后级差分运算放大器将单端信号转换为差分信号,主要作用是为了使前端输出阻抗与 ADC 的输入阻抗相匹配。系统中选用 TI 公司的高速全差分运算放大器 THS4513。THS4513 采用全差动架构,其输入噪声低至  $2.2~\mathrm{nV}/\sqrt{\mathrm{Hz}}$ ,谐波失真极低(输入信号为 70 MHz 的情况下,其二次谐波失真为  $-75~\mathrm{dBc}$ ,三次谐波失真为  $-86~\mathrm{dBc}$ ),1.6 GHz 的高带宽和高达  $5~\mathrm{100~V}/\mu\mathrm{s}$  的压摆率是该芯片的主要优势。为了与 ADC 输入电路直流耦合,THS4513 拥有独特的输出共模电压控制电路,可以设置其输出信号的共模电压。

#### 3.1.2 时钟电路设计

ADC 时钟的常见设计简单分为以下几种:

1) 单片机/FPGA/DSP 等可编程逻辑器件直接产生<sup>[7]</sup>。可编程器件的外接晶振通过器件内部的倍频电路或

图 4 前端小信号检测电路

者锁相环电路产生可靠时钟。因为数字电路对时钟抖动并不敏感,所以依靠晶振及其内部电路产生的时钟精度并不高。时钟抖动会大大制约系统信噪比的提高。

2)锁相环系统产生。锁相环系统是锁定相位的环路,是一个自反馈控制系统。所以在产生稳定的高频信号方面具有频率飘移小,频谱纯度高的优势<sup>[8]</sup>。锁相环的时钟精度是由一系列器件:PLL、VCO'环路滤波器等共同决定的,只有整体设计全部达到要求,锁相环才能实现高精度的时钟输出,这就对电路设计提出了很高要求,也会增加调试和维护的难度<sup>[9-10]</sup>。

3)专用时钟芯片产生。专用时钟芯片通常是把锁相环、VCO、环路滤波等电路集中在一个芯片内,通过简单的数字控制信号就可以产生各种不同频率的时钟信号[10]。该器件兼顾了数字电路和锁相环的优点,提供了控制简单、调试方便的高精度、低抖动时钟。

比较上述3种方案,本系统采用方案3)。系统时钟采用 IDT 公司的 ICS8430-61,这是一款集成高频时钟发生器,其外围电路简单,在单芯片中集成整个锁相环系统加时钟扇出系统,外围器件只要一个晶振,两路 LVPECL 时钟扇出,输出频率范围 20~500 MHz 可调,时钟抖动小,最大值只有6 ps。

#### 3.1.3 FPGA 电路

本系统中采用 Xilinx 公司的 FPGA( XC5VSX35)进行外设控制及速度解算算法的实现。 XC5VSX35 采用了最高支持 500 MHz 的 Xesium 系统时钟技术,具有丰富、灵活的高性能的时钟资源。在内部资源上,其具备 192 个 XtremeDSP (18x18) 数字信号处理单元,34 560 个逻辑单元和 3 456 个 Block RAM。其内置的 Block RAM 包括内置的误差校验和修正(ECC) 功能,不用消耗逻辑单元就可以转换为 FIFO[11]。创新的 ChipSync 技术为简化的源同

步接口提供了专用高精度电路。芯片集成了个多种硬 IP,可以实现多种系统功能,与在逻辑单元中实现同等功能相比,功耗降低多达 80%,速度最高超出 60%。芯片采用三栅极氧化层技术,将功耗较前一代产品降低了 50%。芯片的高性能和丰富的信号处理资源使其非常适合本系统中的高速数字信号处理过程实现。

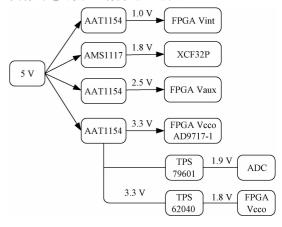

## 3.1.4 电源模块硬件电路设计

因本系统功能复杂,故所涉及的有源器件较多导致涉及到的电源电平种类也比较复杂。所以,在进行系统电源设计之前,首先根据系统所用到的电源种类、电压及功耗进行划分。电源种类和分类需求如表1所示。

表 1 系统电源需求表

| 系统器件           | 电压/V        | 功耗                        |

|----------------|-------------|---------------------------|

| ADS6444        | 3.3         | 1.8 W * 1                 |

| ICS8442        | 3.3         | $600 \text{ mW} \times 1$ |

| XCF32P-VO48    | 1.8         | 240 mW $\times$ 1         |

| VIRTEX-5 LX50T | 1.0,2.5,3.3 | 5 <b>W</b>                |

开关电源芯片 AAT1154 提供 FPGA 和 PROM 的 3.3 V,2.5 V,1.8 V 和 1.2 V 等电压。因为系统中的 AD9517-4 与 ADC 有较大的功耗,并且均为模数混合器件,电源噪声对其影响较大,所以系统中用线性电源为其供电。 ADC 的供电点采用 TPS79601 芯片实现。AD9517-4 则采用 NS 公司的 LM1084 供电。 ADC 前端电路中所需用的 +5 V,+3.3 V则由板卡输入 5 V和开关电源的 3.3 V进行严格的滤波后提供。 -5 V 电平则由 TI 公司的负电源模块 PTN04050 供给。

具体的电源类型划分如图 5 所示:

图 5 电源系统框图

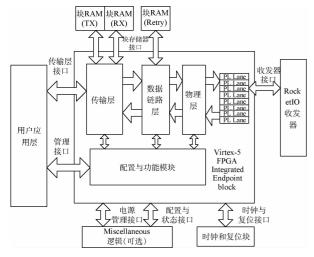

#### 3.1.5 PXIE 传输接口设计

为了简化系统设计,本系统采用内部集成 PCI-E 端点模块知识产权(IP)核的 FPGA Virtex-5 LX50T 作为处理核心。利用 FPGA 内部的 PCI-E IP 核,系统可以快速实现

基于 PCI-E 总线的板卡及模块,从而搭建基于 PCI-E 总线的系统。PCI-E 端点模块的 IP 核框图如图 6 所示。

图 6 Virtex-5 FPGA 集成端点模块图表

PCI-E协议主要包括物理层(physical layer)、数据链路 层(data link layer)及事务层(transaction layer)。物理层是 协议底层模块,主要实现对 PCI-E 链路的检测、训练及维 护,其中最主要的组成部分包括链路训练状态机 (LTSSM)、数据编码解码单元、串并转换单元及差分数据 收发器。数据链路层主要用于保证数据传输的正确性,即 错误检测和校正。数据链路层通过采用纠错编码技术保证 一个数据包内的数据传输正确性,而对于无法纠正的错误 及丢包错误,则采用重发机制来保证数据传输正确性。事 务层主要实现对 PCI-E 事务的处理,即对不同的 PCI-E 事 务采用不同的数据处理方法。PCI-E 协议定义了多种事 务,包括配置读写事务、IO 读写事务和存储器读写事务等, FPGA中的 PCI-E IP 核对不同事务传输过来的数据进行 分类处理[11]。发送数据首先通过事务层组帧,形成带数据 或不带数据的事务帧,然后经过数据链路层,对数据进行纠 错编码,然后再进入物理层进行扰码和 8B/10B 编码,最后 通过高速差分驱动器发送出去。接收端从链路上接收到数 据后,进行与发送端相反的操作,最终得到发送端发送过来 的数据,完成一次传输操作。

## 4 测试结果及分析

为了说明系统的性能,下面对部分系统测试结果进行分析。

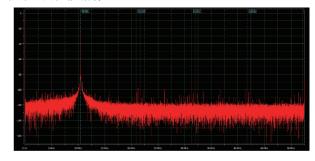

图 7 所示是输入为 10.426 MHz 单音输入信号的采集结果频谱图。从图中可以看出,谐波和杂散抑制比较好。表 2 列出了单频输入时采集结构的性能参数。

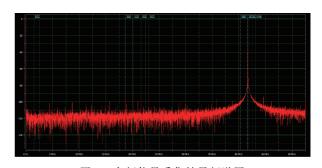

图 8 所示是输入信号为高频单音时的采集结果频谱图。从图中可以看出,输入信号频率升高时采集性能并未发生明显恶化。表 3 所示是输入信号为高频单音时采集结

果的主要性能指标。

图 7 低频信号采集结果频谱图

表 2 低频信号采集性能

| 性能参数 | 指标/dB      |

|------|------------|

| SNR  | 73         |

| SFDR | <b>-89</b> |

| 二阶谐波 | -95        |

| 三阶谐波 | -92        |

图 8 高频信号采集结果频谱图

表 3 高频信号采集性能

| 性能参数 | 指标/dB      |

|------|------------|

| SNR  | 71         |

| SFDR | <b>-90</b> |

| 二阶谐波 | -92        |

| 三阶谐波 | <b>-90</b> |

# 5 结 论

本文详细介绍了基于 FPGA 的多普勒测速雷达信号 采集处理部分的硬件设计,包括脉冲信号采集处理模块,实 时存储模块,信号分析模块和 PXIE 便携式机箱。其中脉 冲信号采集处理模块是系统核心,采用 FPGA 作为处理核 心,有利于测速算法的并行改进,提高测速的实时性,性能 较以往的系统有较大提升空间。

# 参考文献

[1] 郑巧,嵌入式系统的应用与开发分析[J]. 制造业自动

- 化,2011(5):171-173.

- [2] 刘丽华,多普勒雷达测速系统研究[D]. 武汉:华中科技大学,2007.

- [3] 马岭,蔡征宇,程风雷,等.毫米波测速雷达的测速原理[J].弹道学报,2003(4):88-91.

- [4] 李颖宏,马龙,一种新型双激光测速系统的设计与应用[J]. 电子测量与仪器学报,2016,30(2): 256-264.

- [5] 何荣森,何希顺,张跃.从 ARM 体系看嵌入式处理器的发展[J]. 微电子学与计算机,2002(5):42-45.

- [6] 卢铮,李超,方广有. 调频连续波太赫兹雷达方案研究及系统验证[J]. 电子测量技术,2015,38(8):58-63.

- [7] 季青涛,殷兴辉. 基于 MSP430 的锁相环控制系统设计[J]. 国外电子测量技术,2016,35(8):99-102.

- [8] 杨磊,马伟. 锁相环频率源的杂散干扰分析与仿

- 真[J]. 电子测量技术,2010,33(12):16-19.

- [9] 肖江涛,韩前进,王健,等. HMC983/984 的宽带射频源的设计[J]. 电子测量技术,2016,39(4):18-22.

- [10] 许志鹏,余剑. 锁相环中鉴相器的设计与仿真[J]. 电子测量技术,2011,34(11):32-35.

- [11] 余能顺. 基于 PXI Express 总线的高速数字信号中和 器设计与实现[D]. 长沙:国防科学技术大学,2009.

# 作者简介

陈珞,工学硕士,工程师,主要研究方向为系统集成、通信与信息系统技术等。

**白雪杨**,工学硕士,高级工程师,主要研究方向为系统 集成,通信与信息系统技术等。

E-mail: 45774944@qq. com

## (上接第 155 页)

- [5] AL SHEIKH A, BRUN O, HLADIK P E. Partition scheduling on an IMA platform with strict periodicity and communication delays[C]. 18th International Conference on Real-Time and Network Systems, 2010: 179-188.

- [6] SIVANTHI T, KILLAT U. A satisficing momip framework for reliable real-time application scheduling [C]. 2006 2nd IEEE International Symposium on Dependable, Autonomic and Secure Computing, IEEE, 2006: 187-194.

- [7] 金继伟,马菲菲,张健. SMT 求解技术简述[J]. 计 算机科学与探索,2015(7):769-780.

- [8] 张杰. 机载高速数据总线技术的应用研究[J]. 电子测量技术,2016,39(6):163-166.

- [9] 王丽爱,周旭东,陈崚.最大团问题研究进展及算 法测试标准[J]. 计算机应用研究,2007(7): 69-70,107.

- [10] BARRETT C, MOURA L, STUMP A. Design and results of the first satisfiability modulo theories competition (SMTCOMP 2005)[J].

Journal of Automated Reasoning, 2005, 35(4): 373-390.

#### 作者简介

**杨骏峰**,1991年出生,硕士研究生在读,主要研究方向 机载通信网络、实时系统等。

E-mail: yjf\_job@foxmail. com