# 新型时钟管理电路模型分析与参数设计

#### 程甘霖 王蕴龙

(北京空间机电研究所 北京 100094)

摘 要:现今,电子产品的功能越来越复杂,随之而来在电路板设计中会选用多种类型芯片,比如微处理器、ADC、存储器、接口芯片等。这种情况下就需要时钟管理电路实现对多路时钟在频率、相位、占空比、抖动指标上的管理,为每种芯片提供不同属性的工作时钟。本文提出一种基于时钟芯片的新型时钟管理电路,进行总体方案设计,重点对电路中的锁相环的重要环节模型及电路整体模型进行分析,归纳了电路参数选择方法及其与系统指标之间关系,为最终电路详细设计和程序配置的提供参考依据。

关键词:时钟管理电路;锁相环;压控晶振;环路带宽

中图分类号: TM135 文献标识码: A 国家标准学科分类代码: 510,1010

# Model analysis and parameter design for new-type clock management circuit

Cheng Ganlin Wang Yunlong

(Beijing Institute of Space Mechanics & Electricity, Beijing 100094, China)

Abstract: Nowadays, the functions of electronic products are more and more complex, and then different kinds of chips, such as MCU, ADC, memories, interface chips and so on, will be selected in the PCB design. In this case, the clock management circuit is needed to provide different working clocks for each chip. It manages several clock signals in part of frequency and phase, etc, and improves signals in part of cycle duty, jitter, etc. The new-type clock management circuit based on the clock chip is designed in this paper, which consist of the clock management circuit unit and the clock management IP core in the control unit. The important components and the whole circuit are selected to build math models and be analyzed. The method for selecting circuit parameters and the relationship between circuit parameters and system parameters are concluded, which are the references for the detailed circuit design and software configuration.

Keywords: clock management circuit; PLL; VCXO; loop width

#### 1 引 言

当今电路板向着高速数字化、高复杂度的方向发展,多种类型芯片正常工作的前提之一就是为其提供性能良好的时钟信号,时钟管理技术是高速电路设计的一个新方向,如何有效管理电路板时钟成为了新的挑战。时钟管理技术包括时钟同步、时钟去抖、时钟分频、时钟调相、时钟保持、时钟冗余等时钟管理技术。传统时钟管理采用 FPGA 等逻辑器件,通过其硬件描述语言或者器件内部 IP 核实现基本的时钟管理。本文提出一种新型基于时钟芯片的时钟管理电路,可替代传统时钟管理方式,下文将对新型时钟管理电路进行总体方案设计并对电路模型进行分析。

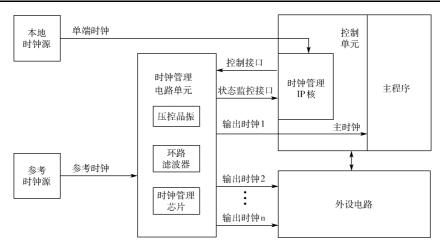

## 2 新型时钟管理电路总体方案设计

新型时钟管理电路主要由时钟管理电路单元与控制单元中的时钟管理 IP 核组成,电路总体框图如图 1 所示,其中时钟管理电路单元由压控晶振、环路滤波器和时钟管理芯片组成,时钟管理 IP 核主要由程序实现,编程语言的选择由控制单元类型而定,控制单元可以选用 FPGA、DSP或者 MCU。

时钟管理电路工作过程如下:时钟管理 IP 核通过控制接口对时钟管理电路单元进行配置,同时通过状态监测接口实时检查电路工作状态,待配置完成后时钟管理电路单元为主程序和外设电路提供的工作时钟信号,输出时钟

图 1 新型时钟管理电路总体框图

信号是与参考时钟相位同步,并且经过时钟管理电路去 抖动。

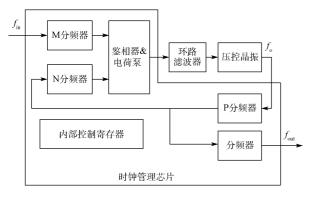

时钟管理电路单元主要由以下部分组成:鉴相器、电荷泵、环路滤波器、压控晶振和分频器,框图如图 2 所示。选择不同的压控晶振型号、环路滤波器参数、时钟管理芯片的内部参数,可以满足不同系统的需求。时钟管理电路单元的核心部分是锁相环(PLL)。当锁相环开始工作时,输入参考信号的频率  $f_{\rm m}$  经过 M 分频后与压控晶振的固有振荡频率  $f_{\rm m}$  经过 P 分频和 N 分频后是略不相同的,固有频率差  $\Delta f = f_{\rm m}/M - f_{\rm o}/(N \cdot P)$ , $\Delta f$  必然引起它们之间的相位差不断变化。鉴相器根据输出一定脉宽的误差电流脉冲,环路滤波器滤除脉冲电流高频噪声,将电流转换为控制电压,控制电压调节压控晶振使其分频后的频率趋向于参考时钟分频后的频率,直到输入鉴相器的两个时钟的频率和相位误差小于预定值,这时锁相环就进入"锁定"的状态[1-3]。

图 2 时钟管理电路单元框图

# 3 时钟管理电路单元模型分析与参数设计

下面分别对组成时钟管理电路单元的 2 个重要环节及整体电路模型进行分析,并给出参数设计方案及电路参数

对系统参数的影响。

#### 3.1 压控晶振模型分析与参数测量

在锁相环电路中,压控晶振(VCXO)是一个关键的器件,它的作用是进行电压到频率的变换。它输出的瞬时频率受到来自环路滤波器的误差电压控制,通常希望压控晶振的中心频率的瞬时频率偏移与控制电压成线性关系,满足式(1),其中  $K_{veo}$ 为压控晶振的压控灵敏度或者称为增益系数,是锁相环电路中一个十分重要的参数<sup>[4]</sup>。

$$K_{\text{veo}} = \frac{f_{\text{veo}}}{V} \tag{1}$$

由于鉴相器是对相位进行比较,所以要将 VXCO 输出 频率转换为相位,角频率随时间变化的相位角为瞬时角频 率对时间的积分,可表示为:

$$\frac{\mathrm{d}\theta_v(t)}{\mathrm{d}t} = 2\pi \cdot \Delta f_{vco} = 2\pi \cdot K_{vco} v_c(t) \tag{2}$$

对式(2)进行拉普拉斯变换,则有:

$$s\,\theta_{v}(s) = K_{v}V_{s}(s) \tag{3}$$

其中  $K_{\pi} = 2\pi \cdot K_{\pi\pi}$ , 整理得到压控晶振的传递函数:

$$H_{\text{vco}}(s) = \frac{\theta_{\text{v}}(s)}{V_{\text{c}}(s)} = \frac{K_{\text{v}}}{s} \tag{4}$$

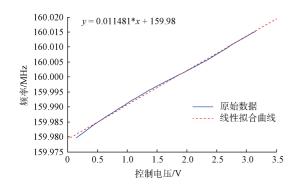

在实际电路情况下, $K_{vo}$ 可以通过手册估算或者实测配合估算,本文为获得更为准确的压控灵敏度采用后者。以 VG-4512CA-160 MHz 型号压控晶振为例,实验仪器采用 Agilent 53230A 频率计测量 VCXO 输出频率,采用 Agilent 33522A 信号源输出控制电压,均匀调节信号源输出电压从  $0.15\sim3.15$  V,依次记录 VCXO 输出时钟频率值。根据实验数据,得到 VG-4512CA-160MHz 的电压-频率曲线,如图 3 中蓝色曲线,可以通过曲线看到电压-频率之间并非理想的线性关系,该非线性是由于器件制造工艺和电气环境等因素造成的。对曲线进行线性拟合如图 3 中红色曲线,坐标系左上角是拟合后的一次方程式,由方程式可知  $K_{vo}$ =11.481 KHz/V。

图 3 VG-4512CA-160M 电压-频率曲线

#### 3.2 环路滤波器模型分析与参数设计

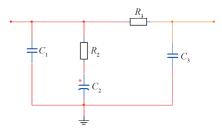

环路滤波器采用无源滤波器,如图 4 电路所示,该电路 将时钟管理芯片内部电荷泵输出的脉冲电流平均化,滤除 高频分量,变换为交流成分少的直流信号。

$$H_{LP}(s) = \frac{1 + sR_2C_2}{s^3(R_2R_3C_1C_2C_3) + s^2(R_2C_1C_2 + R_2C_2C_3 + R_3C_1C_3 + R_3C_2C_3) + s(C_1 + C_2 + C_3)}$$

(6)

环路滤波器的参数的选择会直接影响 PLL 电路系统参数,系统参数主要包括环路带宽、相角裕度和鉴相频率等。 $C_1$ 、 $C_2$ 、 $R_2$ 影响环路滤波器合理地选择零点和极点的交接频率,进一步影响系统的环路带宽和相角裕度。根据经验要实现适当的零点交接频率和极点交接频率位置,选择电路参数  $C_2$  >  $10C_1$ ,零点交接频率大约要小于期望环路带宽的十分之一,第二个极点交接频率大于期望环路带宽的十分之一,第二个极点交接频率大于期望环路带宽的十倍,经过几次迭代就能设计出满足要求的环路滤波器。然后通过改变  $R_2$  值调整相角曲线的峰值在期望环路带宽附近,这样可以使锁相环系统的开环相角裕度更大,易满足系统要求。 $R_3$  和  $C_3$  为滤波器传递函数提供第三个极点,这个极点作用是衰减鉴相频率点处的信号,极点值的选择要大于第二个极点 10 倍~100 倍,并且保证这个极点对应频率小于鉴相频率 10 倍。

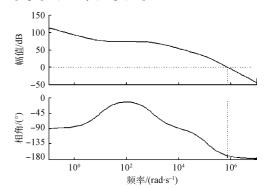

选择  $C_1 = 0.1 \mu F$ ,  $C_2 = 22 \mu F$ ,  $C_3 = 0.1 \mu F$ ,  $R_2 = 4.7 k\Omega$ ,  $R_3 = 160 \Omega$  为滤波器电路参数,求得环路滤波器的交接 频率分别为 0 Hz、1.539 Hz、166.57 Hz 和 20.41 kHz,滤波器传递函数的波特图如图 5,其中波特图横坐标是角频率,单位是 rad/s,是对应频率的  $2\pi$  倍。这组参数条件下,能满足系统环路带宽要求在15 Hz左右的情

图 4 无源滤波器原理

环路滤波器传递函数  $H_{LP}(s)$ 为输出电压与输入电流的比值,如式(5)所示。

$$H_{\rm LP}(s) = \frac{U_{\rm ctrl}(s)}{I_{\rm ep}(s)} \tag{5}$$

根据基尔霍夫电流定律,得到环路滤波器复频域传递函数  $H_{LP}(s)$ 如式(6)所示,传递函数由比例环节、积分环节、微分环节和惯性环节组成。

图 5 无源环路滤波器波特图

况,此时系统的鉴相频率设置要大于 200 kHz。

#### 3.3 电路整体模型分析与参数设计

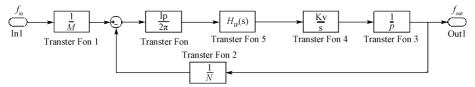

在压控晶振和环路滤波器的模型分析的基础上,本节对时钟管理电路单元的模型做整体的建模和分析。时钟芯片内部的3个分频器可建模为比例环节,增益分别为M、N、P的倒数,鉴相器可建模为比较器和比例环节,比例环节的增益与电荷泵电流IP有关,M、N、P、IP都为软件可配置参数。根据以上分析整个系统模型如图6所示。

图 6 时钟管理电路单元系统模型框图

根据数学模型可以得到系统开环传递函数和闭环传 递函数,如式(7)和式(8)所示

$$H_{\text{open}}(s) = H_{\text{PDF/CP}} \cdot H_{\text{LP}}(s) \cdot H_{\text{VCO}}(s) \cdot H_{\text{P}} \cdot H_{\text{N}}$$

(7)

$$H_{\text{closedloop}}(s) = \frac{H_{\text{M}} \cdot H_{\text{PFD/CP}} \cdot H_{\text{LP}}(s) \cdot H_{\text{VCO}}(s) \cdot H_{\text{P}}}{1 + H_{\text{openloop}}(s)} \tag{8}$$

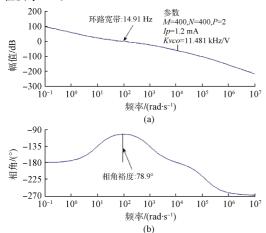

在系统性能参数中,重点关注系统稳定性、相对稳定性、开环增益、环路带宽。选择如下参数M=400,N=400,P=2,IP=1.4 mA,KVCO=11.481 kHz/V 作为例分析参数对系统性能影响。

首先,本质上讲,锁相环电路可以近似认为1个线性负反馈系统,稳定是电路能正常工作的前提,参数选择应满足系统稳定的充要条件,即系统的极点均在 s 平面的左半平面内或者原点上。求得系统3个极点分别为(0,0)、(-1046.6,0)、(-128 208.7,0),均位于 s 平面的负实轴上,满足线性系统稳定条件。

工程上常用相角裕度来衡量一个系统的相对稳定性,为保证系统具有一个较好的相对稳定,需要相角裕度大于0。工程上一般要求系统的相角裕度在55°~80°,在这个范围下的相角裕度值对于选择的环路带宽可以保证较好的相对稳定性,图7中环路带宽对应的相角裕度为78.9°,满足工程要求[5-9]。

图 7 锁相环开环传递函数幅频曲线与相频曲线

根据传递函数可知,在环路滤波器的参数和压控晶振型号确定的情况下,分频值 P、N和电荷泵电流 IP 是影响系统开环增益的参数,增大 IP、减小 P 和 N 都可以增大开环增益,开环增益越大,系统响应时间越短、稳态误差越小,但是过大的开环增益会造成系统不稳定,过小的开环增益造成系统稳定时间过长,所以需要根据实际需要选择合理的开环增益。考虑开环增益的同时,也要兼顾权衡考虑系统环路带宽,因为其会随增大 IP 或者减小 P 和 N 而增大。

环路带宽的选择与参考时钟和压控晶振相位噪声曲 线有关,环路带宽的取值还需要通过实验来确定。假设系 统所需的环路带宽为 15 Hz,图 7 是选择参数下锁相环开环传递函数幅频曲线与相频曲线,系统环路带宽在图 7 中为幅频曲线与横轴的交点值,即系统开环增益为 0 时所对应的角频率值 93.7 rad/s,转换为频率值为 14.91 Hz,满足工程设计需求<sup>[10]</sup>。

#### 4 结 论

本文针对新型基于时钟芯片的时钟管理电路进行了总体方案设计,然后对电路中时钟管理电路单元中的压控晶振、环路滤波器及整体电路单元进行数学建模,文中选择1组参数详细分析并归纳模型中电路参数、配置参数与系统稳定性、相对稳定性、开环增益、环路带宽之间的关系,结论对下一步新型时钟管理电路的原理设计、软硬件调试具有一定的指导意义。

### 参考文献

- [1] MADHU BALASUBRAMANIAN. Using the CDCE72010 as a Frequency Synthesizer [EB/OL]. www.ti.com,2008.

- [2] 远坂俊昭. 锁相环(PLL)电路设计与应用 [M]. 北京:科学出版社,2006.

- [3] 封彦彪,刘兴春,基于 Xilinx FPGA 的时钟管理设计 与实现[J]。电子测量技术,2010,33(10):52-55.

- [4] Silicon labs. VCXO tuning slope, stability and absolute pull range [EB/OL]. www. silabs. com, 2010.

- [5] 刘卫国. MATLAB 程序设计与应用[C]. 北京:高等教育出版社,2007.

- [6] 胡寿松. 自动控制原理[C]. 北京:科学出版 社,2001.

- [7] 李仲秋,曾全胜. 锁相环相位噪声与环路带宽的关系 分析[J]. 现代电子技术,2009(14):132-134.

- [8] 杨沛,张磊,王平连,等,锁相环相位噪声的研究与仿真[J]. 电子测量技术,2009,32(4):35-37.

- [9] 岳松洁, CMOS 电荷泵锁相环中电荷泵的研究与设计[J]. 企业技术开发: 学术版, 2009, 28(9): 4-9.

#### 作者简介

程甘霖,工学硕士,2011年获哈尔滨工程大学自动化学院控制理论与控制工程专业工学硕士学位,现为北京空间机电研究所工程师,现从事视频电子学设计研究。

E-mail: cgl85420@sina.com