DOI:10.19651/j.cnki.emt.1802377

# 基于 FPGA 的动态目标识别与跟踪系统设计

山丹 丛国涛

(大连东软信息学院 智能与电子工程学院 大连 116023)

**摘要:** 为满足动态目标识别与跟踪系统对实时性、低功耗和小型化的要求,设计了一种以 FPGA 为核心的电路系统,辅以 OV7670 视频采集模块和 VGA 接口显示器,实现对视频图像进行采集、处理、矩形框标识,最终实现对动态的识别、跟踪和显示。其中,对图像的处理部分由 FPGA 完成,包括缓存、灰度处理、改进的位运算中值滤波、背景前景分离、帧间差分法与背景差分法融合进行运动目标检测与跟踪等,充分利用 FPGA 的高速并行处理的特点,结合片内 RAM 高速处理和片外 SDRAM 大容量特性,实现对视频数据的处理和存储。同时,系统具有抗干扰性较强、小巧、灵活、低功耗、通用性及可扩展性强等特点,既适合工业领域,又适合家居使用。

**关键词:** FPGA; 帧间差分法; 运动目标检测与跟踪; 中值滤波

中图分类号: TN47 文献标识码: A 国家标准学科分类代码: 51010

## Design of dynamic target recognition and tracking system based on FPGA

Shan Dan Cong Guotao

(School of Intelligence &amp; Electronic Engineering, Dalian Neusoft University of Information, Dalian 116023, China)

**Abstract:** In order to satisfy the requirements of real-time, low-power and miniaturization for dynamic target recognition and tracking system, a system based on FPGA is designed, which is supplemented by OV7670 video acquisition module and VGA interface display. The image is captured, processed and marked with a rectangle. Consequently, the dynamic recognition, tracking and display are realized. Among them, the image processing part is completed by FPGA, including cache, gray processing, improved bit operation median filtering, background and foreground separation, inter-frame difference method and background difference method compromising. It makes full use of the merits of high-speed and parallel processing ability of FPGA, high-speed RAM on-chip, large capacity of off-chip SDRAM to achieve the processing and storage of video data. At the same time, the system has strong anti-interference, compact, flexible, low power consumption, versatility and scalability, which is suitable for industrial areas, but also suitable for home use.

**Keywords:** FPGA; inter-frame difference method; moving target detection and tracking; median filtering

## 0 引言

运动目标识别与跟踪技术作为机器视觉领域的重要分支,近年来成为广大学者研究的重要方向。目前,此类系统在军事制导、视觉导航、机器人、公共安全、智能家居等领域有着广泛的应用前景。而现有系统,绝大多数都是基于 PC 机和 ARM 实现的<sup>[1-4]</sup>,其采用的算法相对比较复杂<sup>[5-7]</sup>,从实时性、功耗、成本和小型化等方面都难以满足不同应用的需求。鉴于此,基于嵌入式平台的运动目标识别与跟踪系统成为了研究热点,而 FPGA 拥有大量逻辑单元和布线资源,具有并行处理、速度快、功耗低、成本低的特点,其设计灵活,易于维护和升级,较传统 PC 机及其它以单片机为核

心的嵌入式系统,有明显优势。因此,本文提出了一种基于 FPGA 硬件平台的动态目标识别与跟踪方案。

动态目标识别与跟踪分为对动态目标的检测,以及对动态目标的追踪。动态目标检测技术有 3 种典型算法,即帧间差分法、背景差分法和光流法<sup>[8-9]</sup>。光流法可以反应图像的运动方式,但是算法复杂,计算量大,实时性难以保证<sup>[10]</sup>;帧间差分法具有较好的稳定性,对光线变化不敏感,但易产生空洞现象<sup>[11]</sup>,背景差分算法能得到较为精确的检测信息,但易受外界环境干扰<sup>[12-13]</sup>。本设计将帧间差分法和背景差分法相融合,并结合阈值自适应算法,形成带背景补偿的自适应帧间差分算法,即保证了实时性,又降低了系统对光线的敏感程度,还避免了空洞的发生。对动态目标

的追踪,采用红色矩形框标识运动物体,既保证了对运动目标追踪,又保证了显示的直观性。

## 1 算法介绍

### 1.1 灰度处理

灰度处理是将彩色图像转换为灰度图像的过程。彩色图像中的每个像素的颜色由R、G、B3个分量决定,而灰度图像是R、G、B3个分量相同的一种特殊的彩色图像,灰度图像的描述与彩色图像一样,仍然反映了整幅图像的整体和局部的色度和亮度等级的分布和特征。根据YUV的颜色空间中,Y的分量的物理意义是点的亮度,由该值反映亮度等级的原理,依据式(1)获得每个像素点的灰度值。

$$Y = 0.3R + 0.59G + 0.11B \quad (1)$$

### 1.2 改进的位运算中值滤波

中值滤波器属于统计排序滤波器的一种,是对图像滤波器所包含区域的非线性空间滤波,用统计排序结果的中值来代替中心像素的值,对脉冲噪声有着较好的抑制作用。中值滤波算法的核心在于排序环节,而对于传统的冒泡排序、选择排序等直接排序方法,计算量大,实时性难于保证,而且实现相对复杂,占用资源多,不适合于FPGA内部的电路实现。因此,本设计采用基于比特平面的快速中值滤波算法<sup>[14]</sup>,对比特平面逐层分类处理,得到中值在各个比特平面的值,最后输出合成的中值。

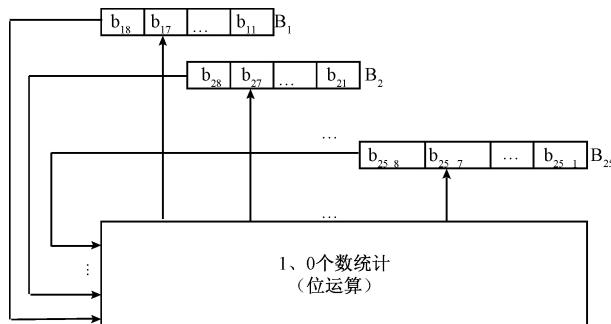

设中值滤波窗口中有M个数据,由于滤波通常选用 $3 \times 3$ 或者 $5 \times 5$ 窗口大小,所以这里的M为奇数。M个数据分别用 $B_i = [b_i^N, b_i^{N-1}, \dots, b_i^2, b_i^1]$ 表示,其中, $i=1, 2, 3 \dots, M, N$ 为二进制无符号数 $B_i$ 的位宽。按位即比特平面由高到低,逐平面进行处理,得到输出中值的各比特位。具体算法如下:

1)按照式(2),统计第j比特平面所有比特0、1的个数,若值为1的比特个数大于值为0的比特个数,则 $m^j = 1$ ,否则 $m^j = 0$ ,对最高比特平面 $j = N$ ,可直接获得 $m^j$ 的值。

$$m^j = \text{majority}(b_1^j, b_2^j, \dots, b_M^j) \quad (2)$$

2)对 $1 \leq j \leq N$ 的比特平面,需按照式(3)更新 $b_i^{j-1}$ 后,返回步骤1),计算 $m^{j-1}$ 的值。

$$b_i^{j-1} = \begin{cases} b_i^{j-1}, b_i^j = m^j \\ b_i^j, b_i^j \neq m^j \end{cases} \quad (3)$$

3)逐比特平面求出 $m^j$ 后,中值即为 $[m^N, m^{N-1}, \dots, m^1]$ 。

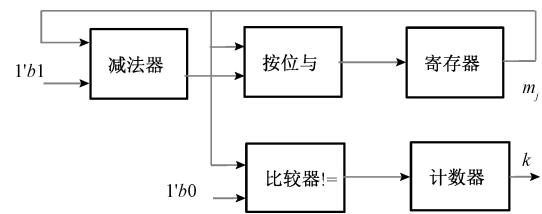

在1)中,比较每个比特平面中1和0的数量,如果采用传统的统计方式,即逐位判断、累计,完成1次比较至少需要N次计算。计算周期较长,不利于视频图像的实时处理,所以本设计提出将位运算特性引入比特面1的数量统计中来,只要1的数量大于 $M/2$ ,则1的数量多,否则0的数量多。设k表示1的数量,算法描述如下,当 $m^j > 0$ 时,

将 $m^j - 1$ ,再与 $m^j$ 相与,每执行一次与操作, $k + 1$ ,直到 $m^j$ 为0为止。这样,完成每个比特面中1和0的数量比较,最多需要N次运算,平均只需要 $N/2$ 次运算即可实现。

$$\text{while}(m^j > 0) \{ m^j = m^j \& (m^j - 1); k = k + 1; \} \quad (4)$$

### 1.3 带背景补偿的自适应帧间差分算法

由于摄像头采集视频序列具有连续性的特点,通过对相邻两帧图像二值化后的值进行差分,根据差分值的大小是否超过阈值,来判断是否含有运动目标,并获取运动目标的位置信息。设连续两帧图像经过灰度处理、中值滤波并二值化后的图像为 $f_k$ 和 $f_{k+1}$ ,两者的差分图像用 $d_c(x, y)$ 表示,则差分结果如式(5)、(6)所示。

$$d_c(x, y) = |f_k(x, y) - f_{k+1}(x, y)| \quad (5)$$

通过差分后得到的值与设定的阈值T的比较,可以得到:

$$R_c(x, y) = \begin{cases} 1 & \text{if } d_c(x, y) > T \\ 0 & \text{if } d_c(x, y) \leq T \end{cases} \quad (6)$$

这里,选取合适的二值化阈值,对算法检测的准确性起着关键作用。由于固定阈值,对环境光线等变化较为敏感,本设计避免采用固定阈值,而改为采用自适应的阈值选取方法,对中值滤波后的灰度图像,统计灰度最大值 $g_{\max}$ 和最小值 $g_{\min}$ ,取均值,即按照式(7),得到二值化时自适应的阈值。

$$g_{th} = (g_{\max} + g_{\min})/2 \quad (7)$$

虽然帧间差分法算法复杂率低,速度快,但容易出现“空洞”、“双影”等现象,考虑到很多情况下,人们更关心运动目标在背景中的移动情况,所以本设计在检测出移动目标的像素坐标位置 $(X_p, Y_p)$ 后,用最小红色矩形边框围绕移动目标坐标,形成移动目标的标识框,并将标识框放置于背景图片中的运动目标处。同时,为保证定位准确,背景图片每隔固定时间间隔进行更新。设二值化像素的像素点集为C,包围盒左上角坐标为 $(X_{\min}, Y_{\min})$ ,右下角坐标为 $(X_{\max}, Y_{\max})$ 则包围盒公式如式(8)~(11)所示。

$$X_{\min} = \min\{X_p \mid (X_p, X_p) \in C\} \quad (8)$$

$$X_{\max} = \max\{X_p \mid (X_p, X_p) \in C\} \quad (9)$$

$$Y_{\min} = \min\{Y_p \mid (X_p, Y_p) \in C\} \quad (10)$$

$$Y_{\max} = \max\{Y_p \mid (X_p, Y_p) \in C\} \quad (11)$$

## 2 系统总体设计方案及原理

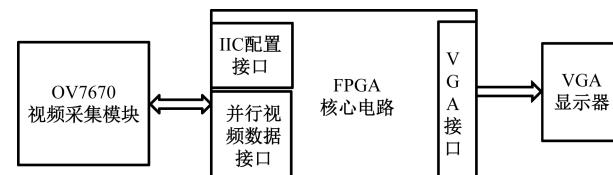

本系统是由FPGA核心板、OV7670视频采集模块、VGA显示模块组成,如图1所示。

图1 系统结构

系统工作原理如下,1)FPGA 核心板采用 Altera 的 CycloneIV 系列 4CE6F17 FPGA 作为控制和数据处理中心,接收由视频采集模块,通过 IIC 接口反馈回来的视频信息,对图像进行一系列处理后,产生 VGA 接口控制时序,最终完成图像显示。2)视频采集模块采用 CMOS 摄像头模块 OV7670,通过 IIC 接口对其进行配置后,开始采集图像数据,并通过 8 bit 并行接口,传输  $640 \times 480$  的  $3 \times 10^5$  Pixel RGB 值,给 FPGA 单元,供后续处理。3)VGA 显示模块用于接收来自 FPGA 的显示数据,经过 D/A 转换后,显示在显示器上。

### 3 FPGA 实现

#### 3.1 FPGA 内部电路结构

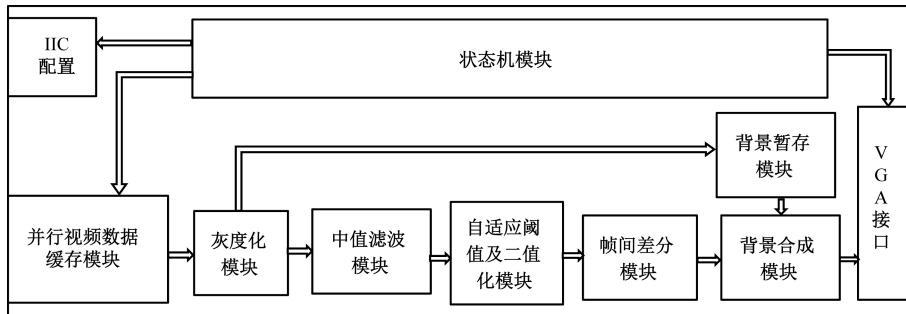

FPGA 内部电路作为整个电路的核心,如图 2 所示,主要由以下模块组成:IIC 配置模块、并行视频数据缓存模块、灰度化模块、中值滤波模块、自适应阈值产生及二值化

模块、帧间差分模块、背景暂存模块、背景合成模块、VGA 接口模块和状态机模块。这里,有限状态机模块决定着电路动作的步调,从配置摄像头模块,到采集并行视频数据,到对图像进行处理,并最终实现动态目标的显示,由状态机对电路动作的先后顺序进行控制。

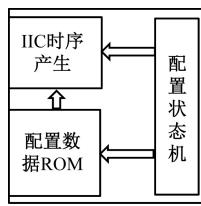

#### 3.2 OV7670 控制模块

FPGA 与图像采集模块 OV7670 模块的通信有 2 种接口,1)用于配置摄像头工作模式的 IIC 接口,2)接收图像数据的并行接口。由于 FPGA 外部晶振输入为 50 MHz,而 IIC 接口的通信频率为 10 KHz,并行数据传输频率为 25 MHz,所以模块内部需对 50 MHz 进行分频,首先二分频为 25 MHz,供给并行数据缓存模块使用,再对 25 MHz 进行一万分频为 10 KHz,供给 IIC 接口使用。这里,对 OV7670 寄存器的配置数据如图 3 所示,以初值文件形式存储于 ROM 中,由状态机控制,不断以 IIC 时序形式,传输给 OV7670,使其每帧图像以  $640 \times 480$  的 RGB565 格式输出。

图 2 FPGA 内部电路的模块

图 3 OV7670 控制模块

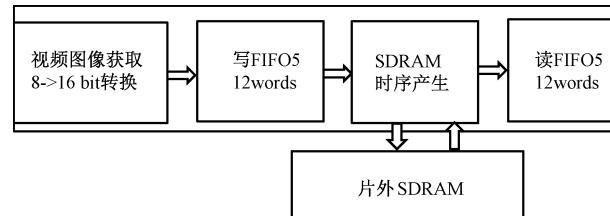

#### 3.3 图像缓存模块

由于图像信息数据量较大,而 FPGA 内部存储器资源有限,所以考虑使用片外 SDRAM 存储像素点颜色数据。由于 OV7670 图像信息是以 25 MHz,8 bit 形式输出,而为提高存储速率,SDRAM 工作在 100 MHz,两者时钟域不同。为解决这个问题,如图 4 所示,中间加入片内双端口 FIFO,图像数据以 25 MHz 写入 FIFO,容量设为 256,当 FIFO 满时,以 100 MHz 读出,并通过 SDRAM 时序产生电路写入 SDRAM 中,并以 100 MHz 的频率读出到 FIFO 中,以备后续处理。这里,OV7670 传输过来的是 8 bit 并行数据,而对于 RGB565 格式的数据来说,每个像素点需要 16 bit 二进制数表示,所以在写入 FIFO 之前,需要将 2 次

接收的 8 bit 数据拼成 16 bit 数据,以完整的表示一个像素点的颜色。另外,SDRAM 设置为突发传输方式,每次突发长度为 256。

图 4 图像缓存模块

#### 3.4 灰度处理模块

由于 FPGA 内部逻辑资源限制,在图像处理过程中,在保证图像质量的前提下,为了尽量减少计算量,将彩色 RGB 图像转成灰度图像。这里,原来 RGB565 最多可以表示  $65536(25 \times 26 \times 25)$  种颜色,而灰度化以后最多只需存储 256 种颜色即可,存储空间降到了彩色图像的 1/2。式(1)中灰度系数为浮点数,在 FPGA 中转为定点数处理,各系数同时扩大 256 倍,则式(1)变成式(12)的形式。对于输入数据为 RGB565 格式来说,红色占 5 bit,其最大值为

32,绿色占6 bit,其最大值为64,蓝色占5 bit,其最大值为32,所以输出最大值为 $12992(77 \times 32 + 150 \times 64 + 29 \times 32)$ ,即用14 bit二进制数表示,最后取高8 bit作为灰度值。

$$Y = 77R + 150G + 29B \quad (12)$$

### 3.5 中值滤波模块

实现基于比特平面的中值滤波算法的关键在于辨识出从高位到低位各比特平面中1和0的数量较多者。这里,以 $5 \times 5$ 滤波窗口为例,共25个灰度值,每个灰度值为8 bit二进制数。首先,如图5所示,对最高比特平面,即在 $[b_{1,8}, b_{2,8}, \dots, b_{25,8}]$ 这25个1 bit二进制数中找到1的数量,只要大于 $25/2$ 即12个,即可得出结论1的数量>0的数量,否则,1的数量<0的数量。由于这里25为奇数,所以不存在1的数量和0的数量相等的情况。根据1、0数量比较的结果,按照式(3)对次高比特平面进行更新,以此类推直到最低比特平面,共完成8次比较。将每次比较的结果拼接起来即为中值。计算每个比特面1的数量,可通过如图6所示电路来实现。

图5 中值滤波模块

图6 比特面1数量位运算模块图

### 3.6 动态目标识别与跟踪模块

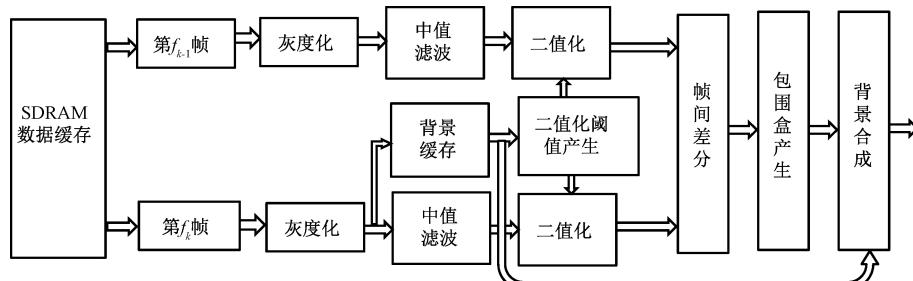

从CMOS摄像头采集来的图像数据经过双端口FIFO完成异步时钟域的数据交互,最终储存于片外SDRAM中。如图7所示,系统上电后,首先完成对SDRAM工作模式寄存器的设置。之后,连续存储2帧的图像数据,SDRAM有1个写端口和2个读端口,写端口的地址范围为 $0 \sim (640 \times 480 \times 2 - 1)$ 2个读端口地址分别为 $0 \sim (640 \times 480 - 1)$ 和 $640 \times 480 - (640 \times 480 \times 2 - 1)$ 。读出的2帧数据分别做灰度化处理、中值滤波、二值化处理后相减,得到运动物体的图像。这里,二值化处理时阈值的选取采用从背景中提取的方式,由式(7)灰度最大值和最小值之和右移2 bit得到阈值。差分结果的绝对值为255或者0;将值为255的像素点坐标 $(x, y)$ 保存于片内RAM中,保存RAM的同时,通过遍历查找出 $x$ 和 $y$ 的最小和最大值,即获得包围盒左上角坐标和右下角坐标。最后将包围盒左上角和右下角连成一个矩形跟踪框,叠加在背景图像上,最终输出。对背景图像的更新设在25 ms/次,可根据实际场景运动目标移动速度,调整背景图像更新频率。

图7 动态目标识别与跟踪模块

### 3.7 VGA接口模块

VGA接口模块用来产生VGA显示器所需要的接口时序,包括行同步、场同步和数据总线信号,并读取视频数据,以25 MHz的频率送到RGB数据总线上。这里,R为5 bit、G为6 bit、B为5 bit,分别取自灰度值的高5 bit、高6 bit和高5 bit。由于视频数据输出频率为25 MHz,对于显示分辨率为 $640 \times 480$ 的VGA显示器而言,刷新频率约为60 Hz。

## 4 实验结果与分析

FPGA电路在黑金开发板AX-301上实现,并配以

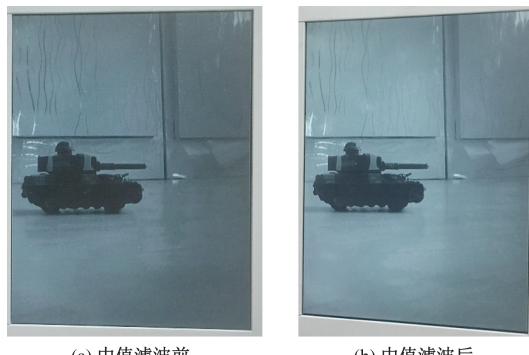

OV7670视频采集模块和VGA接口显示器,构建系统并验证基于FPGA的动态目标识别与跟踪系统的实现效果。中值滤波前和中值滤波后的图像对比如图8所示,由(b)图可见,经过中值滤波后噪声点被滤除了。

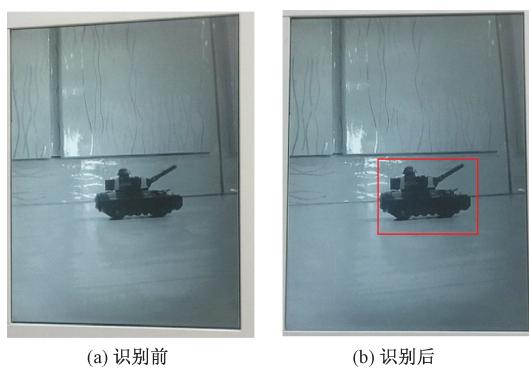

运动目标检测前和运动目标检测后的图像对比如图9所示。运动目标检测后的图像中,用红色矩形框直观地标识出运动物体区域。

系统特性参数<sup>[15-19]</sup>如表1所示,从资源占用情况来看,普通FPGA芯片即可满足要求,实现了低成本的系统设计。从功耗来看,动态功耗和静态功耗之和为0.399 W,实

图 8 中值滤波前和中值滤波后的图像对比

图 9 运动目标检测前和运动目标检测后的图像对比

现了低功耗的目标。从识别率和识别滞后时间来看,能够满足系统对准确性和实时性的需要。从上述各参数来看,系统能够适应未来对系统小型化、低成本、低功耗、实时性的要求。但是,对运动目标的识别区域精确化,以及在识别框精确涵盖运动目标轮廓方面,仍有提升空间。

表 1 系统特性参数

| 资源使用  |          | 功耗/W  |       | 识别率/ | 滞后/ |

|-------|----------|-------|-------|------|-----|

| LE    | Register | 静态    | 动态    | %    | ms  |

| 4 266 | 2 679    | 0.265 | 0.134 | 95.7 | 6   |

## 5 结 论

本系统充分利用 FPGA 的高速并行处理能力,配以图像采集单元和 VGA 显示器,实现了基于 FPGA 的运动目标检测及跟踪。并提出了改进的基于比特平面的中值滤波算法及带背景补偿的自适应帧间差分算法,既方便 FPGA 电路实现,又提高算法效率。本设计具有低功耗、低成本等特点,既可应用于工业环境,也可作为家居安防的一部分使用。但本设计对于复杂动态背景的情况和识别框精确化要求,考虑尚有不足,接下来将就该问题进一步深入研究。

## 参考文献

- [1] 田鹏云,胡孟权. 多飞行器动态目标追踪协同控制研究[J]. 飞行力学, 2017, 35(4): 52-55.

- [2] 田军委,牛秀娟,赵彦飞. 基于动态模板匹配的运动目标识别[J]. 机械与电子, 2017, 35(1): 77-80.

- [3] 高祥,胡文才,王露露,等. 融合动态-静态图像特征的运动目标检测方法[J]. 计算机工程与设计, 2017, 38(6): 1585-1589, 1641.

- [4] 吴永亮,李巴津. 基于 ARM9 的视频监控与目标检测方法的研究[J]. 电子测量技术, 2010, 33(5): 77-79, 83.

- [5] 王蒙,李晋惠. 对动态目标进行匹配的快速算法[J]. 国外电子测量技术, 2006, 25(9): 5-8.

- [6] 翟敬梅,刘坤. 特征点辅助的时空上下文目标跟踪与定位[J]. 仪器仪表学报, 2017, 38(11): 2839-2848.

- [7] 李朕阳,郎朗,陈孟元. 基于 SR-CKF 的移动机器人动态目标跟踪算法[J]. 电子测量与仪器学报, 2016, 30(8): 1198-1205.

- [8] 屈晶晶,辛云宏. 连续帧间差分与背景差分相融合的运动目标检测方法[J]. 光子学报, 2014, 43(7): 219-226.

- [9] 袁国武,陈志强,龚健,等. 一种结合光流法与三帧差分法的运动目标检测算法[J]. 小型微型计算机系统, 2013, 34(3): 668-671.

- [10] GULTEKIN G K, SARANLI A. An FPGA based high performance optical flow hardware design for computer vision applications[J]. Microprocessors and Microsystems, 2013, 37(3): 270-286.

- [11] 陈志勇,彭力,张纪宽. 动态环境下改进五帧差分的运动目标检测新算法[J]. 江南大学学报(自然科学版), 2015, 14(1): 34-37.

- [12] 黄海涛,蔡坚固,洪亲,等. 快速混合高斯模型的运动目标检测[J]. 计算机系统应用, 2015, 24(6): 127-131.

- [13] 陈银,任侃,顾国华,等. 基于改进的单高斯背景模型运动目标检测算法[J]. 中国激光, 2014, 41(11): 239-247.

- [14] 王莹,高美凤. 基于 FPGA 的视频图像目标检测系统[J]. 计算机系统应用, 2017, 26(6): 98-102.

- [15] 吴长江,赵不贿,郑博,等. 基于 FPGA 的动态目标跟踪系统设计[J]. 电子技术应用, 2010, 36(3): 45-47, 50.

- [16] 耿益莹. 基于 FPGA 的目标识别与跟踪系统研究[D]. 长春:长春工业大学, 2016.

- [17] 赵利勇. 基于 FPGA 的视频运动目标检测系统[D]. 西安:西安电子科技大学, 2007.

- [18] 杜建宝,张祖锋. 基于 FPGA 的运动目标检测系统的设计[J]. 仪器仪表用户, 2018, 25(3): 40-42, 48.

- [19] 邵鹏,杨晨,张晋敏. 基于 FPGA 的自适应阈值运动目标检测[J]. 应用光学, 2017, 38(6): 903-909.

## 作者简介

- 山丹,硕士,讲师,主要研究方向为数字集成电路设计与验证。

E-mail: shandan@neusoft.edu.cn

- 丛国涛,硕士,讲师,主要研究方向为数字集成电路设计与验证。

E-mail: congguotao@neusoft.edu.cn